|

List Of Intel Xeon Chipsets

Around the time that the Pentium III processor was introduced, Intel's Xeon line diverged from its line of desktop processors, which at the time was using the Pentium branding. The divergence was implemented by using different sockets; since then, the sockets for Xeon chips have tended to remain constant across several generations of implementation. The chipsets contain a 'memory controller hub' and an 'I/O controller hub', which tend to be called 'north bridge' and 'south bridge' respectively. The memory controller hub connects to the processors, memory, high-speed I/O such as PCI Express, and to the I/O controller hub by a proprietary link. The I/O controller hub, on the other hand, connects to lower-speed I/O, such as SATA, PCI, USB, and Ethernet. P6-based Xeon chipsets Dual processor P6-based Xeon chipsets Intel's initial preferred chipset for Pentium III Xeon was the 840. Four processor P6-based Xeon chipsets The Pentium III Xeon bus protocol allowed four proces ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Pentium III

The Pentium III (marketed as Intel Pentium III Processor, informally PIII or P3) brand refers to Intel's 32-bit x86 desktop and mobile CPUs based on the sixth-generation P6 microarchitecture introduced on February 28, 1999. The brand's initial processors were very similar to the earlier Pentium II-branded processors. The most notable differences were the addition of the Streaming SIMD Extensions (SSE) instruction set (to accelerate floating point and parallel calculations), and the introduction of a controversial serial number embedded in the chip during manufacturing. The Pentium III is also a single-core processor. Even after the release of the Pentium 4 in late 2000, the Pentium III continued to be produced with new models introduced until early 2003, and were discontinued in April 2004 for desktop units, and May 2007 for mobile units. Processor cores Similarly to the Pentium II it superseded, the Pentium III was also accompanied by the Celeron brand for lower-end versions ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Snoop Filter

Bus snooping or bus sniffing is a scheme by which a coherency controller (snooper) in a cache (a snoopy cache) monitors or snoops the bus transactions, and its goal is to maintain a cache coherency in distributed shared memory systems. A cache containing a coherency controller (snooper) is called a snoopy cache. This scheme was introduced by Ravishankar and Goodman in 1983. How it works When specific data is shared by several caches and a processor modifies the value of the shared data, the change must be propagated to all the other caches which have a copy of the data. This change propagation prevents the system from violating cache coherency. The notification of data change can be done by bus snooping. All the snoopers monitor every transaction on a bus. If a transaction modifying a shared cache block appears on a bus, all the snoopers check whether their caches have the same copy of the shared block. If a cache has a copy of the shared block, the corresponding snooper performs ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Panther Point

The Platform Controller Hub (PCH) is a family of Intel's single-chip chipsets, first introduced in 2009. It is the successor to the Intel Hub Architecture, which used two chips - a northbridge and southbridge, and first appeared in the Intel 5 Series. The PCH controls certain data paths and support functions used in conjunction with Intel CPUs. These include clocking (the system clock), Flexible Display Interface (FDI) and Direct Media Interface (DMI), although FDI is used only when the chipset is required to support a processor with integrated graphics. As such, I/O functions are reassigned between this new central hub and the CPU compared to the previous architecture: some northbridge functions, the memory controller and PCIe lanes, were integrated into the CPU while the PCH took over the remaining functions in addition to the traditional roles of the southbridge. AMD has its equivalent for the PCH, known simply as a chipset, no longer using the previous term Fusion control ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ivy Bridge (microarchitecture)

Ivy Bridge is the codename for Intel's 22 nm microarchitecture used in the third generation of the Intel Core processors (Core i7, i5, i3). Ivy Bridge is a die shrink to 22 nm process based on FinFET ("3D") Tri-Gate transistors, from the former generation's 32 nm Sandy Bridge microarchitecture—also known as tick–tock model. The name is also applied more broadly to the Xeon and Core i7 Ivy Bridge-E series of processors released in 2013. Ivy Bridge processors are backward compatible with the Sandy Bridge platform, but such systems might require a firmware update (vendor specific). In 2011, Intel released the 7-series Panther Point chipsets with integrated USB 3.0 and SATA 3.0 to complement Ivy Bridge. Volume production of Ivy Bridge chips began in the third quarter of 2011. Quad-core and dual-core-mobile models launched on April 29, 2012 and May 31, 2012 respectively. Core i3 desktop processors, as well as the first 22 nm Pentium, wer ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cave Creek (PCH)

The Platform Controller Hub (PCH) is a family of Intel's single-chip chipsets, first introduced in 2009. It is the successor to the Intel Hub Architecture, which used two chips - a northbridge and southbridge, and first appeared in the Intel 5 Series. The PCH controls certain data paths and support functions used in conjunction with Intel CPUs. These include clocking (the system clock), Flexible Display Interface (FDI) and Direct Media Interface (DMI), although FDI is used only when the chipset is required to support a processor with integrated graphics. As such, I/O functions are reassigned between this new central hub and the CPU compared to the previous architecture: some northbridge functions, the memory controller and PCIe lanes, were integrated into the CPU while the PCH took over the remaining functions in addition to the traditional roles of the southbridge. AMD has its equivalent for the PCH, known simply as a chipset, no longer using the previous term Fusion controll ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Patsburg

The Platform Controller Hub (PCH) is a family of Intel's single-chip chipsets, first introduced in 2009. It is the successor to the Intel Hub Architecture, which used two chips - a northbridge and southbridge, and first appeared in the Intel 5 Series. The PCH controls certain data paths and support functions used in conjunction with Intel CPUs. These include clocking (the system clock), Flexible Display Interface (FDI) and Direct Media Interface (DMI), although FDI is used only when the chipset is required to support a processor with integrated graphics. As such, I/O functions are reassigned between this new central hub and the CPU compared to the previous architecture: some northbridge functions, the memory controller and PCIe lanes, were integrated into the CPU while the PCH took over the remaining functions in addition to the traditional roles of the southbridge. AMD has its equivalent for the PCH, known simply as a chipset, no longer using the previous term Fusion controll ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Gigabaud

In telecommunication and electronics, baud (; symbol: Bd) is a common unit of measurement of symbol rate, which is one of the components that determine the speed of communication over a data channel. It is the unit for symbol rate or modulation rate in symbols per second or pulses per second. It is the number of distinct symbol changes (signalling events) made to the transmission medium per second in a digitally modulated signal or a bd rate line code. Baud is related to ''gross bit rate'', which can be expressed in bits per second. If there are precisely two symbols in the system (typically 0 and 1), then baud and bit per second (bit/s) are equivalent. Naming The baud unit is named after Émile Baudot, the inventor of the Baudot code for telegraphy, and is represented according to the rules for SI units. That is, the first letter of its symbol is uppercase (Bd), but when the unit is spelled out, it should be written in lowercase (baud) except when it begins a sentence. It w ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Active Management Technology

Intel Active Management Technology (AMT) is hardware and firmware for remote out-of-band management of select business computers, running on the Intel Management Engine, a microprocessor subsystem not exposed to the user, intended for monitoring, maintenance, updating, and repairing systems. Out-of-band (OOB) or hardware-based management is different from software-based (or in-band) management and software management agents. Hardware-based management works at a different level from software applications, and uses a communication channel (through the TCP/IP stack) that is different from software-based communication (which is through the software stack in the operating system). Hardware-based management does not depend on the presence of an OS or a locally installed management agent. Hardware-based management has been available on Intel/AMD based computers in the past, but it has largely been limited to auto-configuration using DHCP or BOOTP for dynamic IP address allocation and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cougar Point

The cougar (''Puma concolor'') is a large cat native to the Americas. Its range spans from the Canadian Yukon to the southern Andes in South America and is the most widespread of any large wild terrestrial mammal in the Western Hemisphere. It is an adaptable, generalist species, occurring in most American habitat types. This wide range has brought it many common names, including puma, mountain lion, catamount and panther (for the Florida sub-population). It is the second-largest cat in the New World, after the jaguar (''Panthera onca''). Secretive and largely solitary by nature, the cougar is properly considered both nocturnal and crepuscular, although daytime sightings do occur. Despite its size, the cougar is more closely related to smaller felines, including the domestic cat (''Felis catus'') than to any species of the subfamily Pantherinae. The cougar is an ambush predator that pursues a wide variety of prey. Primary food sources are ungulates, particularly deer, but ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

List Of Intel Xeon Microprocessors

The following is a list of Intel Xeon microprocessors, by generation. P6-based * Pentium II Xeon 400 * Pentium II Xeon 400 * Pentium II Xeon 450 * Pentium II Xeon 450 * Pentium II Xeon 450 * Pentium III Xeon 500 * Pentium III Xeon 500 * Pentium III Xeon 500 * Pentium III Xeon 550 * Pentium III Xeon 550 * Pentium III Xeon 550 * Pentium III Xeon 600 * Pentium III Xeon 667 * Pentium III Xeon 700 * Pentium III Xeon 700 * Pentium III Xeon 733 * Pentium III Xeon 800 * Pentium III Xeon 866 * Pentium III Xeon 900 * Pentium III Xeon 933 * Pentium III Xeon 1.00 NetBurst-based * Xeon 1.4 * Xeon 1.5 * Xeon 1.7 * Xeon 2.0 * Xeon 1.8 * Xeon 2.0A * Xeon 2.0B * Xeon 2.2 * Xeon 2.4 * Xeon 2.4B * Xeon 2.6 * Xeon 2.66 * Xeon 2.8 * Xeon 2.8B * Xeon 3.0 * Xeon 3.06 * Xeon LV 1.6 * Xeon LV 2.0 * Xeon LV 2.4 * Xeon 2.4B * Xeon 2.8B * Xeon 3.06 * Xeon 3.2 * Xeon 3.2 * Xeon 2.8 * Xeon 2.8D * Xeon 3.0 * Xeon 3.0D * Xeon 3.2 * Xeon 3.4 * Xeon 3. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Sandy Bridge (microarchitecture)

Sandy Bridge is the codename for Intel's 32 nm microarchitecture used in the second generation of the Intel Core processors (Core i7, i5, i3). The Sandy Bridge microarchitecture is the successor to Nehalem and Westmere microarchitecture. Intel demonstrated a Sandy Bridge processor in 2009, and released first products based on the architecture in January 2011 under the Core brand. Sandy Bridge is manufactured in the 32 nm process and has a soldered contact with the die and IHS (Integrated Heat Spreader), while Intel's subsequent generation Ivy Bridge uses a 22 nm die shrink and a TIM (Thermal Interface Material) between the die and the IHS. Technology Intel demonstrated a Sandy Bridge processor with A1 stepping at 2 GHz during the Intel Developer Forum in September 2009. Upgraded features from Nehalem include: CPU * Intel Turbo Boost 2.0 * 32 KB data + 32 KB instruction L1 cache and 256 KB L2 cache per core * Shared L3 cache which includes ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

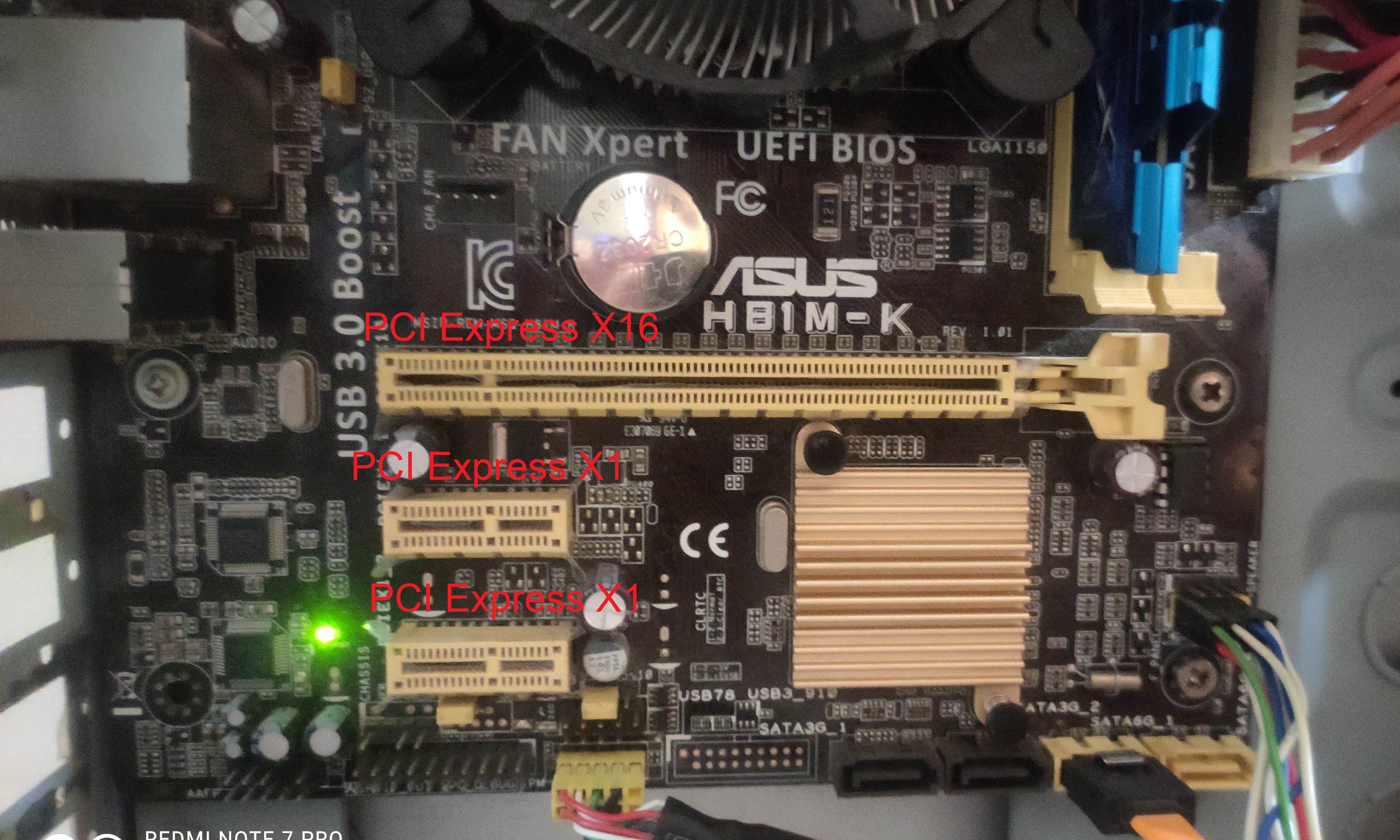

PCI Express

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common motherboard interface for personal computers' graphics cards, hard disk drive host adapters, SSDs, Wi-Fi and Ethernet hardware connections. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism (Advanced Error Reporting, AER), and native hot-swap functionality. More recent revisions of the PCIe standard provide hardware support for I/O virtualization. The PCI Express electrical interface is measured by the number of simultaneous lanes. (A lane is a single send/receive line of data. The analogy is a highway with traffic in both directions. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |