|

Esterel Studio

Esterel is a synchronous programming language for the development of complex reactive systems. The imperative programming style of Esterel allows the simple expression of parallelism and preemption. As a consequence, it is well suited for control-dominated model designs. The development of the language started in the early 1980s, and was mainly carried out by a team of Ecole des Mines de Paris and INRIA led by Gérard Berry in France. Current compilers take Esterel programs and generate C code or hardware (RTL) implementations (VHDL or Verilog). The language is still under development, with several compilers out. The commercial version of Esterel is the development environment Esterel Studio. The company that commercialize itSynfora initiated a normalization process with the IEEE in April 2007 however the working group (P1778) dissolved March 2011. ThEsterel v7 Reference Manual Version v7 30 – initial IEEE standardization proposalis publicly available. The Multiform Notio ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Synchronous Programming Language

A synchronous programming language is a computer programming language optimized for programming reactive systems. Computer systems can be sorted in three main classes: (1) transformational systems that take some inputs, process them, deliver their outputs, and terminate their execution; a typical example is a compiler; (2) interactive systems that interact continuously with their environment, at their own speed; a typical example is the web; and (3) reactive systems that interact continuously with their environment, at a speed imposed by the environment; a typical example is the automatic flight control system of modern airplanes. Reactive systems must therefore react to stimuli from the environment within strict time bounds. For this reason they are often also called real-time systems, and are found often in embedded systems. Synchronous programming (also synchronous reactive programming or SRP) is a computer programming paradigm supported by synchronous programming languages. The ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Esterel Studio

Esterel is a synchronous programming language for the development of complex reactive systems. The imperative programming style of Esterel allows the simple expression of parallelism and preemption. As a consequence, it is well suited for control-dominated model designs. The development of the language started in the early 1980s, and was mainly carried out by a team of Ecole des Mines de Paris and INRIA led by Gérard Berry in France. Current compilers take Esterel programs and generate C code or hardware (RTL) implementations (VHDL or Verilog). The language is still under development, with several compilers out. The commercial version of Esterel is the development environment Esterel Studio. The company that commercialize itSynfora initiated a normalization process with the IEEE in April 2007 however the working group (P1778) dissolved March 2011. ThEsterel v7 Reference Manual Version v7 30 – initial IEEE standardization proposalis publicly available. The Multiform Notio ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Parallel Programming Model

In computing, a parallel programming model is an abstraction of parallel computer architecture, with which it is convenient to express algorithms and their composition in programs. The value of a programming model can be judged on its ''generality'': how well a range of different problems can be expressed for a variety of different architectures, and its ''performance'': how efficiently the compiled programs can execute. The implementation of a parallel programming model can take the form of a library invoked from a sequential language, as an extension to an existing language, or as an entirely new language. Consensus around a particular programming model is important because it leads to different parallel computers being built with support for the model, thereby facilitating portability of software. In this sense, programming models are referred to as '' bridging'' between hardware and software.Leslie G. Valiant, "A bridging model for parallel computation", Communications of the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Esterel Technologies

Esterel Technologies is a supplier of model-based design, validation, and code generation tools for safety-critical software and hardware applications. Esterel's tools create formal specifications that produce control designs code in software and/or hardware. Esterel Technologies, a wholly owned subsidiary of Ansys, Inc., has offices in Élancourt, France, and Mountain View, California. Esterel also has direct sales offices in Ottobrunn, Germany, Bracknell, United Kingdom, and Shanghai, P.R. China. Distributors in Japan, China, South Korea, Israel, and India complement the Esterel direct sales offices. Products The Esterel Technologies' SCADE Product Family includes: SCADE System, SCADE Suite, SCADE Display, and SCADE LifeCycle. SCADE Suite was acquired from Telelogic in 2001. In September 2006, Esterel Technologies acquired the IMAGE product from Thales and Diehl Aerospace. It is now proposed as SCADE Display, a display framework targeted for Real-time applications, for ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SIGNAL Programming Language

SIGNAL is a programming language based on synchronized data-flow (flows + synchronization): a process is a set of equations on elementary flows describing both data and control. The SIGNAL formal model provides the capability to describe systems with several clocks (polychronous systems) as relational specifications. Relations are useful as partial specifications and as specifications of non-deterministic devices (for instance a non-deterministic bus) or external processes (for instance an unsafe car driver). Using SIGNAL allows one to specify an application, to design an architecture, to refine detailed components down to RTOS or hardware description. The SIGNAL model supports a design methodology which goes from specification to implementation, from abstraction to concretization, from synchrony to asynchrony. SIGNAL has been mainly developed iINRIAhttp://www.inria.fr/en/en/teams/espresso Espresso team] since the 1980s, at the same time as similar programming languages, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Lustre Programming Language

Lustre is a formally defined, declarative, and synchronous dataflow programming language for programming reactive systems. It began as a research project in the early 1980s. A formal presentation of the language can be found in the 1991 Proceedings of the IEEE. In 1993 it progressed to practical, industrial use in a commercial product as the core language of the industrial environment SCADE, developed by Esterel Technologies. It is now used for critical control software in aircraft, helicopters, and nuclear power plants. Structure of Lustre programs A Lustre program is a series of ''node'' definitions, written as: node foo(a : bool) returns (b : bool); let b = not a; tel Where foo is the name of the node, a is the name of the single input of this node and b is the name of the single output. In this example the node foo returns the negation of its input a, which is the expected result. Inner variables Additional internal variables can be declared as follows: node Nan ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Erroneous Program

In the design of programming languages, an erroneous program is one whose semantics are not well-defined, but where the language implementation is not obligated to signal an error either at compile or at execution time. For example, in Ada Ada may refer to: Places Africa * Ada Foah, a town in Ghana * Ada (Ghana parliament constituency) * Ada, Osun, a town in Nigeria Asia * Ada, Urmia, a village in West Azerbaijan Province, Iran * Ada, Karaman, a village in Karaman Province, ...: :In addition to bounded errors, the language rules define certain kinds of errors as leading to erroneous execution. Like bounded errors, the implementation need not detect such errors either prior to or during run time. Unlike bounded errors, there is no language-specified bound on the possible effect of erroneous execution; the effect is in general not predictable.''Ada Reference Manual'' ISO/IEC 8652:1995(Epdf section 1.1.5. Defining a condition as "erroneous" means that the language implement ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IEEE

The Institute of Electrical and Electronics Engineers (IEEE) is a 501(c)(3) professional association for electronic engineering and electrical engineering (and associated disciplines) with its corporate office in New York City and its operations center in Piscataway, New Jersey. The mission of the IEEE is ''advancing technology for the benefit of humanity''. The IEEE was formed from the amalgamation of the American Institute of Electrical Engineers and the Institute of Radio Engineers in 1963. Due to its expansion of scope into so many related fields, it is simply referred to by the letters I-E-E-E (pronounced I-triple-E), except on legal business documents. , it is the world's largest association of technical professionals with more than 423,000 members in over 160 countries around the world. Its objectives are the educational and technical advancement of electrical and electronic engineering, telecommunications, computer engineering and similar disciplines. History Origin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Verilog

Verilog, standardized as IEEE 1364, is a hardware description language (HDL) used to model electronic systems. It is most commonly used in the design and verification of digital circuits at the register-transfer level of abstraction. It is also used in the verification of analog circuits and mixed-signal circuits, as well as in the design of genetic circuits. In 2009, the Verilog standard (IEEE 1364-2005) was merged into the SystemVerilog standard, creating IEEE Standard 1800-2009. Since then, Verilog is officially part of the SystemVerilog language. The current version is IEEE standard 1800-2017. Overview Hardware description languages such as Verilog are similar to software programming languages because they include ways of describing the propagation time and signal strengths (sensitivity). There are two types of assignment operators; a blocking assignment (=), and a non-blocking (>>. A generate–endgenerate construct (similar to VHDL's generate–endgenerate) allows Verilog ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Imperative Programming

In computer science, imperative programming is a programming paradigm of software that uses statements that change a program's state. In much the same way that the imperative mood in natural languages expresses commands, an imperative program consists of commands for the computer to perform. Imperative programming focuses on describing ''how'' a program operates step by step, rather than on high-level descriptions of its expected results. The term is often used in contrast to declarative programming, which focuses on ''what'' the program should accomplish without specifying all the details of ''how'' the program should achieve the result. Imperative and procedural programming Procedural programming is a type of imperative programming in which the program is built from one or more procedures (also termed subroutines or functions). The terms are often used as synonyms, but the use of procedures has a dramatic effect on how imperative programs appear and how they are constructed ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

VHDL

The VHSIC Hardware Description Language (VHDL) is a hardware description language (HDL) that can model the behavior and structure of digital systems at multiple levels of abstraction, ranging from the system level down to that of logic gates, for design entry, documentation, and verification purposes. Since 1987, VHDL has been standardized by the Institute of Electrical and Electronics Engineers (IEEE) as IEEE Std 1076; the latest version of which is IEEE Std 1076-2019. To model analog and mixed-signal systems, an IEEE-standardized HDL based on VHDL called VHDL-AMS (officially IEEE 1076.1) has been developed. VHDL is named after the United States Department of Defense program that created it, the Very High-Speed Integrated Circuits Program (VHSIC). In the early 1980s, the VHSIC Program sought a new HDL for use in the design of the integrated circuits it aimed to develop. The product of this effort was VHDL Version 7.2, released in 1985. The effo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

C (programming Language)

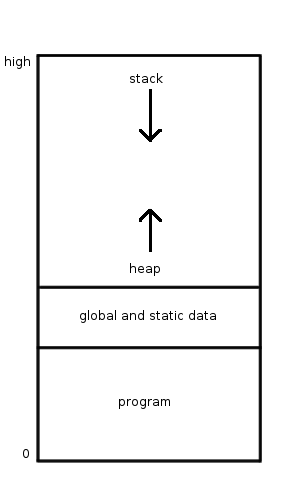

C (''pronounced like the letter c'') is a General-purpose language, general-purpose computer programming language. It was created in the 1970s by Dennis Ritchie, and remains very widely used and influential. By design, C's features cleanly reflect the capabilities of the targeted CPUs. It has found lasting use in operating systems, device drivers, protocol stacks, though decreasingly for application software. C is commonly used on computer architectures that range from the largest supercomputers to the smallest microcontrollers and embedded systems. A successor to the programming language B (programming language), B, C was originally developed at Bell Labs by Ritchie between 1972 and 1973 to construct utilities running on Unix. It was applied to re-implementing the kernel of the Unix operating system. During the 1980s, C gradually gained popularity. It has become one of the measuring programming language popularity, most widely used programming languages, with C compilers avail ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |