|

Synchronous Data Flow

Synchronous Data Flow (SDF) is a restriction on Kahn process networks where the number of tokens read and written by each process is known ahead of time. In some cases, processes can be scheduled such that channels have bounded FIFOs. Limitations SDF does not account for asynchronous processes as their token read/write rates will vary. Practically, one can divide the network into synchronous sub-networks connected by asynchronous links. Alternatively a runtime supervisor can enforce fairness and other desired properties. Applications SDF is useful for modeling digital signal processing (DSP) routines. Models can be compiled to target parallel hardware like FPGAs, processors with DSP instruction sets like Qualcomm's Hexagon, and other systems. See also * Kahn process networks * Petri net *Dataflow architecture Dataflow architecture is a dataflow-based computer architecture that directly contrasts the traditional von Neumann architecture or control flow architecture ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Kahn Process Networks

A Kahn process network (KPN, or process network) is a Distributed computing, distributed ''model of computation'' in which a group of deterministic sequential Process (computing), processes communicate through unbounded FIFO (computing and electronics), first in, first out channels. The model requires that reading from a channel is Blocking (computing), blocking while writing is Asynchronous I/O, non-blocking. Due to these key restrictions, the resulting process network exhibits Deterministic algorithm, deterministic behavior that does not depend on the timing of computation nor on Network delay, communication delays. Kahn process networks were originally developed for modeling parallel programs, but have proven convenient for modeling embedded systems, high-performance computing systems, signal processing systems, stream processing systems, dataflow programming languages, and other computational tasks. KPNs were introduced by Gilles Kahn in 1974. Execution model KPN is a common m ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

FIFO (computing And Electronics)

Representation of a FIFO queue In computing and in systems theory, first in, first out (the first in is the first out), acronymized as FIFO, is a method for organizing the manipulation of a data structure (often, specifically a data buffer) where the oldest (first) entry, or "head" of the queue, is processed first. Such processing is analogous to servicing people in a queue area on a first-come, first-served (FCFS) basis, i.e. in the same sequence in which they arrive at the queue's tail. FCFS is also the jargon term for the FIFO operating system scheduling algorithm, which gives every process central processing unit (CPU) time in the order in which it is demanded. FIFO's opposite is LIFO, last-in-first-out, where the youngest entry or "top of the stack" is processed first. A priority queue is neither FIFO or LIFO but may adopt similar behaviour temporarily or by default. Queueing theory encompasses these methods for processing data structures, as well as interactions be ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Unbounded Nondeterminism

In computer science, unbounded nondeterminism or unbounded indeterminacy refers to a behavior in concurrency (multiple tasks running at once) where a process may face unpredictable delays due to competition for shared resources—such as a printer or memory—or have infinitely many options to choose from at a given point. While these delays or choices can be arbitrarily large, the process is typically guaranteed to complete eventually under certain conditions (e.g., fairness in resource allocation). This concept, explored in abstract models rather than practical systems, became significant in developing mathematical descriptions of such systems (denotational semantics) and later contributed to research on advanced computing theories (hypercomputation). Fairness Unbounded nondeterminism is often discussed alongside the concept of ''fairness''. In this context, fairness means that if a system keeps returning to a certain state forever, it must eventually try every possible next s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Digital Signal Processing

Digital signal processing (DSP) is the use of digital processing, such as by computers or more specialized digital signal processors, to perform a wide variety of signal processing operations. The digital signals processed in this manner are a sequence of numbers that represent Sampling (signal processing), samples of a continuous variable in a domain such as time, space, or frequency. In digital electronics, a digital signal is represented as a pulse train, which is typically generated by the switching of a transistor. Digital signal processing and analog signal processing are subfields of signal processing. DSP applications include Audio signal processing, audio and speech processing, sonar, radar and other sensor array processing, spectral density estimation, statistical signal processing, digital image processing, data compression, video coding, audio coding, image compression, signal processing for telecommunications, control systems, biomedical engineering, and seismology ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Field-programmable Gate Array

A field-programmable gate array (FPGA) is a type of configurable integrated circuit that can be repeatedly programmed after manufacturing. FPGAs are a subset of logic devices referred to as programmable logic devices (PLDs). They consist of an array of programmable logic device, programmable logic block, logic blocks with a connecting grid, that can be configured "in the field" to interconnect with other logic blocks to perform various digital functions. FPGAs are often used in limited (low) quantity production of custom-made products, and in research and development, where the higher cost of individual FPGAs is not as important, and where creating and manufacturing a custom circuit would not be feasible. Other applications for FPGAs include the telecommunications, automotive, aerospace, and industrial sectors, which benefit from their flexibility, high signal processing speed, and parallel processing abilities. A FPGA configuration is generally written using a hardware descr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Qualcomm Hexagon

Hexagon is the brand name for a family of digital signal processor (DSP) and later neural processing unit (NPU) products by Qualcomm. Hexagon is also known as QDSP6, standing for “sixth generation digital signal processor.” According to Qualcomm, the Hexagon architecture is designed to deliver performance with low power over a variety of applications. Each version of Hexagon has an instruction set and a micro-architecture. These two features are intimately related. Hexagon is used in Qualcomm Snapdragon chips, for example in smartphones, cars, wearable devices and other mobile devices and is also used in components of cellular phone networks. Instruction set architecture Computing devices have instruction sets, which are their lowest, most primitive languages. Common instructions are those which cause two numbers to be added, multiplied or combined in other ways, as well as instructions that direct the processor where to look in memory for its next instruction. There ar ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

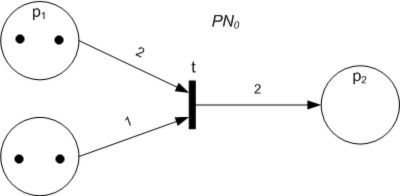

Petri Net

A Petri net, also known as a place/transition net (PT net), is one of several mathematical modeling languages for the description of distributed systems. It is a class of discrete event dynamic system. A Petri net is a directed bipartite graph that has two types of elements: places and transitions. Place elements are depicted as white circles and transition elements are depicted as rectangles. A place can contain any number of tokens, depicted as black circles. A transition is enabled if all places connected to it as inputs contain at least one token. Some sources state that Petri nets were invented in August 1939 by Carl Adam Petri — at the age of 13 — for the purpose of describing chemical processes. Like industry standards such as UML activity diagrams, Business Process Model and Notation, and event-driven process chains, Petri nets offer a graphical notation for stepwise processes that include choice, iteration, and concurrent execution. Unlike these standards, Pet ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Dataflow Architecture

Dataflow architecture is a dataflow-based computer architecture that directly contrasts the traditional von Neumann architecture or control flow architecture. Dataflow architectures have no program counter, in concept: the executability and execution of instructions is solely determined based on the availability of input arguments to the instructions, so that the order of instruction execution may be hard to predict. Although no commercially successful general-purpose computer hardware has used a dataflow architecture, it has been successfully implemented in specialized hardware such as in digital signal processing, network routing, graphics processing, telemetry, and more recently in data warehousing, and artificial intelligence (as: polymorphic dataflow Convolution Engine, structure-driven, dataflow scheduling). It is also very relevant in many software architectures today including database engine designs and parallel computing Parallel computing is a type of compu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |