|

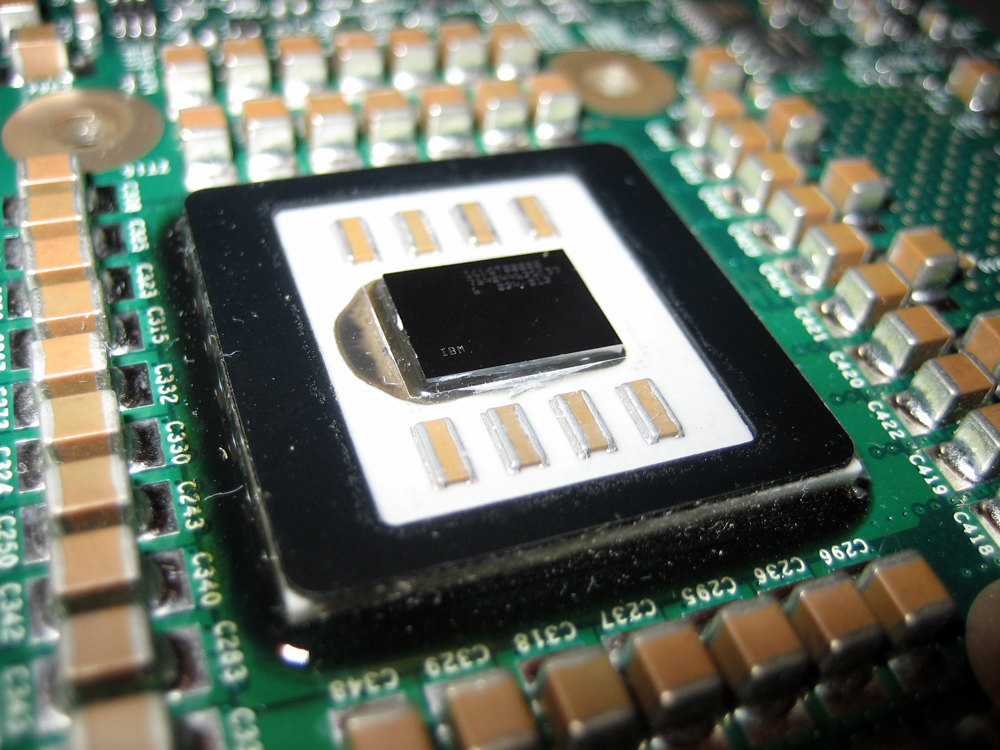

PowerPC G5

The PowerPC 970, PowerPC 970FX, and PowerPC 970MP are 64-bit PowerPC CPUs from IBM introduced in 2002. Apple branded the 970 as PowerPC G5 for its Power Mac G5. Having created the PowerPC architecture in the early 1990s via the AIM alliance, the 970 family was created through a further collaboration between IBM and Apple. The project was codenamed GP-UL or Giga Processor Ultra Light, where Giga Processor is the codename for the POWER4 from which the core was derived. When Apple introduced the Power Mac G5, it stated that this was a five-year collaborative effort, with multi-generation roadmap. This forecast however was short-lived when Apple later had to retract its promise to deliver a 3 GHz processor only one year after its introduction. IBM was also unable to reduce power consumption to levels necessary for laptop computers. Ultimately, Apple only used three variants of the processor. IBM's JS20/JS21 blade modules and some low-end workstations and System p servers are b ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

130 Nanometer

The 130 nanometer (130 nm) process is a level of semiconductor process technology that was reached in the 2000–2001 timeframe by such leading semiconductor companies as Intel, Texas Instruments, IBM, and TSMC. The origin of the 130 nm value is historical, as it reflects a trend of 70% scaling every 2–3 years. The naming is formally determined by the International Technology Roadmap for Semiconductors (ITRS). Some of the first CPUs manufactured with this process include Intel Tualatin family of Pentium III processors. Processors using 130 nm manufacturing technology * Motorola PowerPC 7447 and 7457 2002 * IBM Gekko (GameCube) * IBM PowerPC G5 970 - October 2002 - June 2003 * Intel Pentium III Tualatin - 2001-06 * Intel Celeron Tualatin-256 - 2001-10-02 * Intel Pentium M Banias - 2003-03-12 * Intel Pentium 4 Northwood - 2002-01-07 * Intel Celeron Northwood-128 - 2002-09-18 * Intel Xeon Prestonia and Gallatin - 2002-02-25 * VIA C3 - 2001 * AMD Athlon XP Thorough ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Instruction Prefetch

Instruction or instructions may refer to: A specific direction or order given to someone to perform a task or carry out a procedure. They provide clear guidance on how to achieve a desired outcome. They can be written or verbal, and they typically include detailed steps or actions to follow. Instructions are crucial for ensuring tasks are completed correctly and efficiently. Computing * Instruction, one operation of a processor within a computer architecture instruction set * Computer program, a collection of instructions Music * Instruction (band), a 2002 rock band from New York City, US * "Instruction" (song), a 2017 song by English DJ Jax Jones * ''Instructions'' (album), a 2001 album by Jermaine Dupri Other uses * Instruction, teaching or education performed by a teacher * Sebayt, a work of the ancient Egyptian didactic literature aiming to teach ethical behaviour * Instruction, the pre-trial phase of an investigation led by a judge in an inquisitorial system of justice * I ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IMac G5

The iMac G5 is a series of all-in-one personal computers that was designed, manufactured and sold by Apple Computer from 2004 to 2006. The iMac G5 returned to a more traditional design after the "sunflower" iMac G4, with the computer components fitted behind a liquid-crystal display and mounted on an aluminum foot. The computer was designed around the need to cool its PowerPC 970 processor, and features an interior divided into zones for cooler, quieter operation. The iMac G5 was announced at the Apple Expo in Paris in August 2004, and was revised twice during its lifespan before being replaced by the first iMacs based on Intel processors. The iMac G5 was well received by critics, who noted its performance, quiet operation, and ease of use. Criticisms included its port placement, lack of ergonomic adjustments, and lack of base memory. The design established by the G5 iMacs would influence the design of subsequent models. Overview The iMac G5 is an all-in-one personal comp ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Xserve G5

The Xserve is a discontinued series of rack-mounted servers that was manufactured by Apple Inc. between 2002 and 2011. It was Apple's first rack-mounted server, and could function as a file server, web server or run high-performance computing applications in clusters – a dedicated cluster Xserve, the Xserve Cluster Node, without a video card and optical drives was also available. The first Xserve had a processor, replaced by a in 2004, and by Intel Xeon processors in 2006; each was available in single-processor and dual-processor configurations. The Xserve was discontinued in 2011, and replaced with the Mac Pro Server and the Mac Mini Server. Before the Xserve, Apple's server line included the Apple Workgroup Server, Macintosh Server, and Apple Network Server. Xserve G4 Apple introduced the Xserve on May 14, 2002 (released in June). Initially, two configuration options were available: a single-processor Xserve at US$2999, and a dual-processor Xserve at US$3999. Xserv ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

L2 Cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (MMU) whic ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM BladeCenter

The IBM BladeCenter was IBM's blade server architecture, until it was replaced by Flex System in 2012. The x86 division was later sold to Lenovo in 2014. History Introduced in 2002, based on engineering work started in 1999, the IBM eServer BladeCenter was relatively late to the blade server market. It differed from prior offerings in that it offered a range of x86 Intel server processors and input/output (I/O) options. The naming was changed to IBM BladeCenter in 2005. In February 2006, IBM introduced the BladeCenter H with switch capabilities for 10 Gigabit Ethernet and InfiniBand 4X. A web site called Blade.org was available for the blade computing community through about 2009. In 2012, the replacement Flex System was introduced. Enclosures IBM BladeCenter (E) The original IBM BladeCenter was later marketed as BladeCenter E. Power supplies have been upgraded through the life of the chassis from the original 1200 to 1400, 1800, 2000 and 2320 watt. The BladeCenter (E) ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Northbridge (computing)

In computing, a northbridge (also host bridge, or memory controller hub) is a microchip that comprises the core logic chipset architecture on motherboards to handle high-performance tasks, especially for older personal computers. It is connected directly to a CPU via the front-side bus (FSB), and is usually used in conjunction with a slower southbridge to manage communication between the CPU and other parts of the motherboard. Historically, separation of functions between CPU, northbridge, and southbridge chips was necessary due to the difficulty of integrating all components onto a single chip die. However, as CPU speeds increased over time, a bottleneck emerged due to limitations caused by data transmission between the CPU and its support chipset. The trend for integrated northbridges began near the end of the 2000s for example, the Nvidia GeForce 320M GPU in the 2010 MacBook Air was a northbridge/southbridge/GPU combo chip. On older Intel based PCs, the northbridge was ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Double Data Rate

In computing, double data rate (DDR) describes a computer bus that transfers data on both the rising and falling edges of the clock signal and hence doubles the memory bandwidth by transferring data twice per clock cycle. This is also known as double pumped, dual-pumped, and double transition. The term toggle mode is used in the context of NAND flash memory. Overview The simplest way to design a clocked electronic circuit is to make it perform one transfer per full cycle (rise and fall) of a clock signal. This, however, requires that the clock signal changes twice per transfer, while the data lines change at most once per transfer. When operating at a high bandwidth, signal integrity limitations constrain the clock frequency. By using both edges of the clock, the data signals operate with the same limiting frequency, thereby doubling the data transmission rate. This technique has been used for microprocessor front-side busses, Ultra-3 SCSI, expansion buses ( AGP, PCI ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Microprocessor Report

''Microprocessor Report'' is a newsletter covering the microprocessor industry. The publication is accessible only to paying subscribers. To avoid bias, it does not take advertisements. The publication provides extensive analysis of new high-performance microprocessor chips. It also covers microprocessor design issues, microprocessor-based systems, memory and system logic chips, embedded processors, GPUs, DSPs, and intellectual property (IP) cores. History and profile ''Microprocessor Report'' was first published in 1987 by Michael Slater (engineer). Original board members included Bruce Koball, George Morrow, Brian Case, John Wakerly, Nick Tredennick, Bernard Peuto, Rich Belgard, Dennis Allison, and J H Wharton all of whom served for many years. Slater left MicroDesign Resources (MDR), at the end of 1999. Slater's company MDR, based in Sebastopol, California, originally published ''Microprocessor Report.'' MDR also hosted an annual conference, the Microprocessor Forum, and r ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Floating-point Unit

A floating-point unit (FPU), numeric processing unit (NPU), colloquially math coprocessor, is a part of a computer system specially designed to carry out operations on floating-point numbers. Typical operations are addition, subtraction, multiplication, division, and square root. Modern designs generally include a fused multiply-add instruction, which was found to be very common in real-world code. Some FPUs can also perform various transcendental functions such as exponential or trigonometric calculations, but the accuracy can be low, so some systems prefer to compute these functions in software. Floating-point operations were originally handled in software in early computers. Over time, manufacturers began to provide standardized floating-point libraries as part of their software collections. Some machines, those dedicated to scientific processing, would include specialized hardware to perform some of these tasks with much greater speed. The introduction of microcode in ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Double-precision Floating-point Format

Double-precision floating-point format (sometimes called FP64 or float64) is a floating-point number format, usually occupying 64 bits in computer memory; it represents a wide range of numeric values by using a floating radix point. Double precision may be chosen when the range or precision of single precision would be insufficient. In the IEEE 754 standard, the 64-bit base-2 format is officially referred to as binary64; it was called double in IEEE 754-1985. IEEE 754 specifies additional floating-point formats, including 32-bit base-2 ''single precision'' and, more recently, base-10 representations (decimal floating point). One of the first programming languages to provide floating-point data types was Fortran. Before the widespread adoption of IEEE 754-1985, the representation and properties of floating-point data types depended on the computer manufacturer and computer model, and upon decisions made by programming-language implementers. E.g., GW-BASIC's double-precision ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |