|

Lynnfield (microprocessor)

Lynnfield is the code name for a quad-core processor from Intel released in September 2009. It was sold in varying configurations as Intel Core i5, Core i5-7xx, Intel Core i7, Core i7-8xx or Xeon X34xx. Lynnfield uses the Nehalem (microarchitecture), Nehalem microarchitecture and replaces the earlier Penryn (microarchitecture), Penryn based Wolfdale (microprocessor), Wolfdale and Yorkfield (microprocessor), Yorkfield processors, using the same 45 nm process technology, but with a new memory and bus interface. The product code for Lynnfield is 80605, its CPUID value identifies it as family 6, model 30 (0106Ex). Lynnfield is related to the earlier Bloomfield (microprocessor), Bloomfield and Gainestown (microprocessor), Gainestown microprocessors, which are used in server and high-end desktop systems. The main difference between the two is Lynnfield's use of the LGA 1156 processor socket as opposed to the LGA 1366 socket used by Bloomfield and Gainestown processors. LGA 1156 processor ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

45 Nm

Per the International Technology Roadmap for Semiconductors, the 45 nm process is a MOSFET technology node referring to the average half-pitch of a memory cell manufactured at around the 2007–2008 time frame. Matsushita and Intel started mass-producing 45 nm chips in late 2007, and AMD started production of 45 nm chips in late 2008, while IBM, Infineon, Samsung, and Chartered Semiconductor have already completed a common 45 nm process platform. At the end of 2008, SMIC was the first China-based semiconductor company to move to 45 nm, having licensed the bulk 45 nm process from IBM. In 2008, TSMC moved on to a 40nm process. Many critical feature sizes are smaller than the wavelength of light used for lithography (i.e., 193 nm and 248 nm). A variety of techniques, such as larger lenses, are used to make sub-wavelength features. Double patterning has also been introduced to assist in shrinking distances between features, especially if dry li ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Penryn (microarchitecture)

In Intel's Tick-Tock cycle, the 2007/2008 "Tick" was the shrink of the Core microarchitecture to 45 nanometers as CPUID model 23. In Core 2 processors, it is used with the code names Penryn (Socket P), Wolfdale (LGA 775) and Yorkfield (MCM, LGA 775), some of which are also sold as Celeron, Pentium and Xeon processors. In the Xeon brand, the Wolfdale-DP and Harpertown code names are used for LGA 771 based MCMs with two or four active Wolfdale cores. Architectural improvements over 65-nanometer Core 2 CPUs include a new divider with reduced latency, a new shuffle engine, and SSE4.1 instructions (some of which are enabled by the new single-cycle shuffle engine). Maximum L2 cache size per chip was increased from 4 to 6 MB, with L2 associativity increased from 16-way to 24-way. Cut-down versions with 3 MB L2 also exist, which are commonly called Penryn-3M and Wolfdale-3M as well as Yorkfield-6M, respectively. The single-core version of Penryn, listed as Penryn-L here, is not a sepa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

List Of Intel Core I7 Microprocessors

The following is a list of Intel Core processors. This includes Intel's original Core (Solo/Duo) mobile series based on the Enhanced Pentium M microarchitecture, as well as its Core 2- (Solo/Duo/Quad/Extreme), Core i3-, Core i5-, Core i7-, Core i9-, Core M- (m3/m5/m7/m9), Core 3-, Core 5-, and Core 7- Core 9-, branded processors. Desktop processors Core 2 "Allendale" (65 nm, 800 MT/s) *All models support: '' MMX, SSE, SSE2, SSE3, SSSE3, Enhanced Intel SpeedStep Technology (EIST), Intel 64, XD bit (an NX bit implementation), Intel Active Management Technology (iAMT2)'' * Die size: 111 mm2 * Steppings: L2, M0, G0 Note: The M0 and G0 Steppings have better optimizations to lower idle power consumption from 12W to 8W. Note: The E4700 uses G0 Stepping which makes it a Conroe CPU. "Conroe" (65 nm, 1066 MT/s) *All models support: '' MMX, SSE, SSE2, SSE3, SSSE3, Enhanced Intel SpeedStep Technology (EIST), Intel 64, XD bit (an NX bit implementat ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Dynamic Random Access Memory

Dynamics (from Greek δυναμικός ''dynamikos'' "powerful", from δύναμις ''dynamis'' " power") or dynamic may refer to: Physics and engineering * Dynamics (mechanics), the study of forces and their effect on motion Brands and enterprises * Dynamic (record label), an Italian record label in Genoa Mathematics * Dynamical system, a concept describing a point's time dependency ** Topological dynamics, the study of dynamical systems from the viewpoint of general topology * Symbolic dynamics, a method to model dynamical systems Social science * Group dynamics, the study of social group processes especially * Population dynamics, in life sciences, the changes in the composition of a population * Psychodynamics, the study of psychological forces driving human behavior * Social dynamics, the ability of a society to react to changes * Spiral Dynamics, a social development theory Other uses * Dynamics (music), the softness or loudness of a sound or note * DTA Dynamic, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Clarkdale (microprocessor)

Clarkdale is the codename for Intel's first-generation Core i5, i3 and Pentium dual-core desktop processors. It is closely related to the mobile Arrandale processor; both use dual-core dies based on the 32 nm Westmere microarchitecture and have integrated Graphics, PCI Express and DMI links built-in. Clarkdale is the successor of the Wolfdale used in desktop Intel Core 2, Celeron and Pentium Dual-Core processors. Unlike its predecessor, Clarkdale already contains the major north bridge components, such as memory controller, PCI Express for external graphics, integrated graphics and the DMI connector, making it possible to build more compact systems without a separate north bridge or discrete graphics like Lynnfield. The Clarkdale processor package contains two dies: the 32 nm processor die with the I/O connections, and the 45 nm graphics and integrated memory controller die. Physical separation of the processor die and memory controller die resulted in increased ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Havendale (microprocessor)

Havendale is a suburban *Uptown *, neighborhood located in Kingston, Jamaica Kingston is the Capital (political), capital and largest city of Jamaica, located on the southeastern coast of the island. It faces a natural harbour protected by the Palisadoes, a long spit (landform), sand spit which connects the town of Por .... References Neighbourhoods in Kingston, Jamaica {{Jamaica-geo-stub ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Clarksfield (microprocessor)

Clarksfield is the code name for an Intel processor, initially sold as mobile Intel Core i7. It is closely related to the desktop Lynnfield processor, both use quad-core dies based on the 45 nm Nehalem microarchitecture and have integrated PCI Express and DMI links. The predecessor of Clarksfield, Penryn-QC was a multi-chip module with two dual-core Penryn dies based on Penryn microarchitecture, a shrink of Merom microarchitecture. The name of the direct successor of Clarksfield has not been announced. Arrandale is a later mobile processor but opens a new line of mid-range dual-core processors with integrated graphics. At the time of its release at the Intel Developer Forum on September 23, 2009, Clarksfield processors were significantly faster than any other laptop processor, including the Core 2 Extreme QX9300. The initial laptop manufacturers shipping products based on Clarksfield processors include MSI, Dell/Alienware, Hewlett-Packard, Toshiba and Asustek. [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Northbridge (computing)

In computing, a northbridge (also host bridge, or memory controller hub) is a microchip that comprises the core logic chipset architecture on motherboards to handle high-performance tasks, especially for older personal computers. It is connected directly to a CPU via the front-side bus (FSB), and is usually used in conjunction with a slower southbridge to manage communication between the CPU and other parts of the motherboard. Historically, separation of functions between CPU, northbridge, and southbridge chips was necessary due to the difficulty of integrating all components onto a single chip die. However, as CPU speeds increased over time, a bottleneck emerged due to limitations caused by data transmission between the CPU and its support chipset. The trend for integrated northbridges began near the end of the 2000s for example, the Nvidia GeForce 320M GPU in the 2010 MacBook Air was a northbridge/southbridge/GPU combo chip. On older Intel based PCs, the northbridge was ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PCI Express

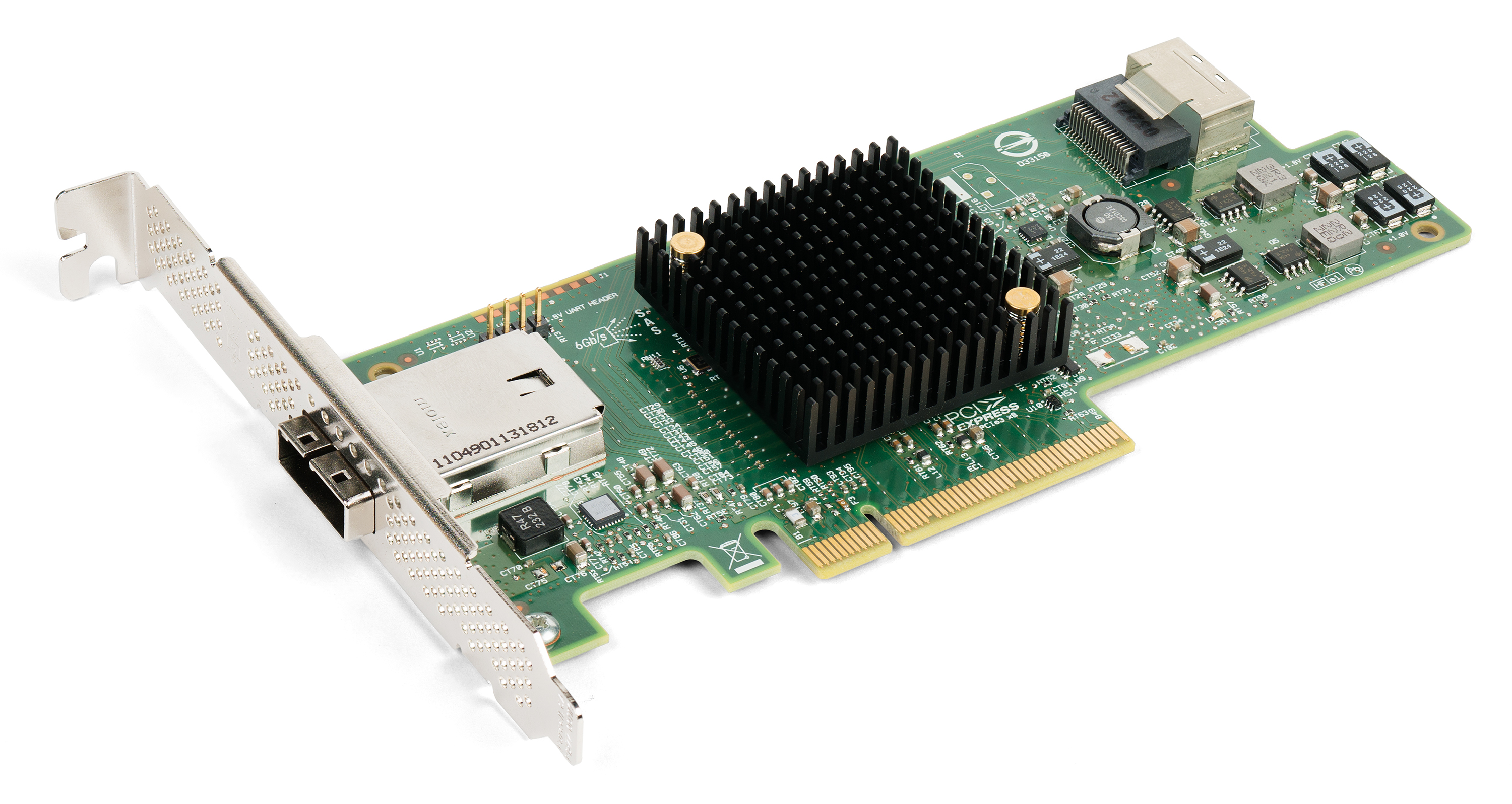

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe, is a high-speed standard used to connect hardware components inside computers. It is designed to replace older expansion bus standards such as Peripheral Component Interconnect, PCI, PCI-X and Accelerated Graphics Port, AGP. Developed and maintained by the PCI-SIG (PCI Special Interest Group), PCIe is commonly used to connect graphics cards, sound cards, Wi-Fi and Ethernet adapters, and storage devices such as solid-state drives and hard disk drives. Compared to earlier standards, PCIe supports faster data transfer, uses fewer pins, takes up less space, and allows devices to be added or removed while the computer is running (hot swapping). It also includes better error detection and supports newer features like I/O virtualization for advanced computing needs. PCIe connections are made through "lanes," which are pairs of wires that send and receive data. Devices can use one or more lanes ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Direct Media Interface

In computing, Direct Media Interface (DMI) is Intel's proprietary link between the northbridge (or CPU) and southbridge (e.g. Platform Controller Hub family) chipset on a computer motherboard. It was first used between the 9xx chipsets and the ICH6, released in 2004. Previous Intel chipsets had used the Intel Hub Architecture to perform the same function, and server chipsets use a similar interface called ''Enterprise Southbridge Interface'' (ESI). While the "DMI" name dates back to ICH6, Intel mandates specific combinations of compatible devices, so the presence of a DMI does not guarantee by itself that a particular northbridge–southbridge combination is allowed. DMI is essentially PCI Express, using multiple lanes and differential signaling to form a point-to-point link. Most implementations use a ×8 or ×4 link, while some mobile systems (e.g. 915GMS, 945GMS/GSE/GU and the Atom N450) use a ×2 link, halving the bandwidth. The original implementation provides 10& ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |