|

Dimensity

This is a list of MediaTek processors for use in smartphones, tablets, smartwatches, IoT, Smart TVs and smartbooks. Smartphone processors from ARMv5 to ARMv8 (2003–2019) ARMv5 ARMv6 ARMv7 Single core Dual-core Quad-core Hexa-core and octa-core ARMv8 Quad-core Octa-core Helio Series Helio X Series (2014–2017) Helio A Series (2018–2020) Helio P Series (2015–2020) Helio G Series (2019–present) Dimensity Series (2020–present) Dimensity 700 Series Dimensity 800 Series Dimensity 900 Series Dimensity 1000 Series Dimensity 8000 Series Dimensity 9000 Series Standalone application and tablet processors Kompanio Series Digital television SoCs Pentonic Series Wearable device SoCs Internet-of-Things (IoT) SoCs Wireless connectivity SoC MT6630 (2014) is a five-in-one combo wireless SoC integrating dual-band 802.11a/b/g/n/ac, advanced Wi-Fi Direct and Miracast support, Bluetooth ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Cortex-A76

The ARM Cortex-A76 is a central processing unit implementing the ARMv8.2-A 64-bit instruction set designed by ARM Holdings' Austin design centre. ARM states a 25% and 35% increase in integer and floating point performance, respectively, over a Cortex-A75 of the previous generation. Design The Cortex-A76 serves as the successor of the ARM Cortex-A73 and ARM Cortex-A75, though based on a clean sheet design. The Cortex-A76 frontend is a 4-wide decode out-of-order superscalar design. It can fetch 4 instructions per cycle. And rename and dispatch 4 Mops, and 8 µops per cycle. The out-of-order window size is 128 entries. The backend is 8 execution ports with a pipeline depth of 13 stages and the execution latencies of 11 stages. The core supports unprivileged 32-bit applications, but privileged applications must utilize the 64-bit ARMv8-A ISA. It also supports Load acquire (LDAPR) instructions ( ARMv8.3-A), Dot Product instructions (ARMv8.4-A), PSTATE Speculative Store Bypass ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Cortex-A710

The ARM Cortex-A710 is the successor to the ARM Cortex-A78, being the First-Generation Armv9 “big” Cortex CPU. It is the companion to the ARM Cortex-A510 "LITTLE" efficiency core. It was designed by ARM Ltd. Arm is a British semiconductor and software design company based in Cambridge, England. Its primary business is in the design of ARM processors (CPUs). It also designs other chips, provides software development tools under the DS-5, RealView an ...'s Austin centre. It is the fourth and last iteration of Arm’s Austin core family. Design * 10-cycle pipeline * The only ARMv9 to support EL0 AArch32 Improvements: * 30% more power efficient than Cortex-A78. * 10% uplift in performance compared to Cortex-A78 *2x ML uplift Usage * MediaTek Dimensity 9000/9000+ * Qualcomm Snapdragon 7 Gen 1 * Qualcomm Snapdragon 8/8+ Gen 1 * Samsung Exynos 2200 References {{Application ARM-based chips ARM processors ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Cortex-X3

The ARM Cortex-X3 is the third generation X-series high-performance CPU core from Arm. Improvements * 25% peak performance improvement over the Cortex-X2. * 11% IPC uplift over the Cortex-X2, when based on the same process, clock speed, and cache setup (also known as ISO-process). * 34% performance gain over a mid-tier Intel Core i7-1260P ( Alder Lake). Usage * MediaTek Dimensity 9200 * Qualcomm Snapdragon 8 Gen 2 ''Antirrhinum'' is a genus of plants commonly known as dragon flowers, snapdragons and dog flower because of the flowers' fancied resemblance to the face of a dragon that opens and closes its mouth when laterally squeezed. They are native t ... References ARM processors {{Comp-hardware-stub ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Cortex-X2

The ARM Cortex-X2 is a central processing unit implementing the ARMv9-A 64-bit instruction set designed by ARM Holdings' Austin design centre as part of ARM's Cortex-X Custom (CXC) program. Architecture changes in comparison with ARM Cortex-X1 The processor implements the following changes: * 10 cycle pipeline down from 11, created by reducing the dispatch stage from 2 cycles to 1 * reorder buffer increased by 30% from 224 entries to 288 * dTLB increased by 20% from 40 entries to 48 * SVE2 SIMD support *Bfloat16 data type support * Support for Aarch32 removed *Comparing the Cortex-X2 with 8MB of L3 cache to the Cortex-X1 with 4MB of L3 cache: **16% greater integer performance **100% greater ML performance Usage * MediaTek Dimensity 9000/9000+ * Qualcomm Snapdragon 8/8+ Gen 1 * Samsung Exynos 2200 See also * ARM Cortex-A710 The ARM Cortex-A710 is the successor to the ARM Cortex-A78, being the First-Generation Armv9 “big” Cortex CPU. It is the companion to th ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Cortex-A77

The ARM Cortex-A77 is a central processing unit implementing the ARMv8.2-A 64-bit instruction set designed by ARM Holdings' Austin design centre. ARM announced an increase of 23% and 35% in integer and floating point performance, respectively. Memory bandwidth increased 15% relative to the A76. Design The Cortex-A77 serves as the successor of the Cortex-A76. The Cortex-A77 is a 4-wide decode out-of-order superscalar design with a new 1.5K macro-OP (MOPs) cache. It can fetch 4 instructions and 6 Mops per cycle. And rename and dispatch 6 Mops, and 13 µops per cycle. The out-of-order window size has been increased to 160 entries. The backend is 12 execution ports with a 50% increase over Cortex-A76. It has a pipeline depth of 13 stages and the execution latencies of 10 stages. There are six pipelines in the integer cluster – an increase of two additional integer pipelines from Cortex-A76. One of the changes from Cortex-A76 is the unification of the issue queues. Previously ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Cortex-A78

The ARM Cortex-A78 is a central processing unit implementing the ARMv8.2-A 64-bit instruction set designed by ARM Ltd.'s Austin centre, set to be distributed amongst high-end devices in 2020–2021. Design The ARM Cortex-A78 is the successor to the ARM Cortex-A77. It can be paired with the ARM Cortex-X1 and/or ARM Cortex-A55 CPUs in a DynamIQ configuration to deliver both performance and efficiency. The processor also claims as much as 50% energy savings over its predecessor. The Cortex-A78 is a 4-wide decode out-of-order superscalar design with a 1.5K macro-OP (MOPs) cache. It can fetch 4 instructions and 6 Mops per cycle, and rename and dispatch 6 Mops, and 13 µops per cycle. The out-of-order window size is 160 entries and the backend has 13 execution ports with a pipeline depth of 13 stages, and the execution latencies consist of 10 stages. The processor is built on a standard Cortex-A roadmap and offers a 2.1 GHz (5 nm) chipset which makes it better than its ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

MediaTek

MediaTek Inc. () is a Taiwanese fabless semiconductor company that provides chips for wireless communications, high-definition television, handheld mobile devices like smartphones and tablet computers, navigation systems, consumer multimedia products and digital subscriber line services as well as optical disc drives. Headquartered in Hsinchu, the company has 25 offices worldwide and was the third largest fabless chip designer worldwide in 2016. Mediatek was founded in 1997. The company also provides its customers with reference designs. MediaTek became the biggest smartphone chipset vendor with 31% market share in Q3 2020. MediaTek’s strong performance in regions like China and India helped it become the biggest smartphone chipset vendor. Corporate history MediaTek was originally a unit of the Taiwanese firm, United Microelectronics Corporation (UMC), tasked with designing chipsets for home entertainment products. On May 28, 1997, the unit was spun off and incorporated ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Cortex-A53

The ARM Cortex-A53 is one of the first two central processing units implementing the ARMv8-A 64-bit instruction set designed by ARM Holdings' Cambridge design centre. The Cortex-A53 is a 2-wide decode superscalar processor, capable of dual-issuing some instructions. It was announced October 30, 2012 and is marketed by ARM as either a stand-alone, more energy-efficient alternative to the more powerful Cortex-A57 microarchitecture, or to be used alongside a more powerful microarchitecture in a big.LITTLE configuration. It is available as an IP core to licensees, like other ARM intellectual property and processor designs. Overview * 8-stage pipelined processor with 2-way superscalar, in-order execution pipeline * DSP and NEON SIMD extensions are mandatory per core * VFPv4 Floating Point Unit onboard (per core) * Hardware virtualization support * TrustZone security extensions * 64-byte cache lines * 10-entry L1 TLB, and 512-entry L2 TLB * 4KiB conditional branch predictor, 25 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

System On A Chip

A system on a chip or system-on-chip (SoC ; pl. ''SoCs'' ) is an integrated circuit that integrates most or all components of a computer or other electronic system. These components almost always include a central processing unit (CPU), memory interfaces, on-chip input/output devices, input/output interfaces, and secondary storage interfaces, often alongside other components such as radio modems and a graphics processing unit (GPU) – all on a single substrate or microchip. It may contain digital, analog, mixed-signal, and often radio frequency signal processing functions (otherwise it is considered only an application processor). Higher-performance SoCs are often paired with dedicated and physically separate memory and secondary storage (such as LPDDR and eUFS or eMMC, respectively) chips, that may be layered on top of the SoC in what's known as a package on package (PoP) configuration, or be placed close to the SoC. Additionally, SoCs may use separate wireless ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM9

ARM9 is a group of 32-bit RISC ARM processor cores licensed by ARM Holdings for microcontroller use. The ARM9 core family consists of ARM9TDMI, ARM940T, ARM9E-S, ARM966E-S, ARM920T, ARM922T, ARM946E-S, ARM9EJ-S, ARM926EJ-S, ARM968E-S, ARM996HS. Since ARM9 cores were released from 1998 to 2006, they are no longer recommended for new IC designs, instead ARM Cortex-A, ARM Cortex-M, ARM Cortex-R cores are preferred. Overview With this design generation, ARM moved from a von Neumann architecture (Princeton architecture) to a (modified; meaning split cache) Harvard architecture with separate instruction and data buses (and caches), significantly increasing its potential speed. Most silicon chips integrating these cores will package them as modified Harvard architecture chips, combining the two address buses on the other side of separated CPU caches and tightly coupled memories. There are two subfamilies, implementing different ARM architecture versions. Differences ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

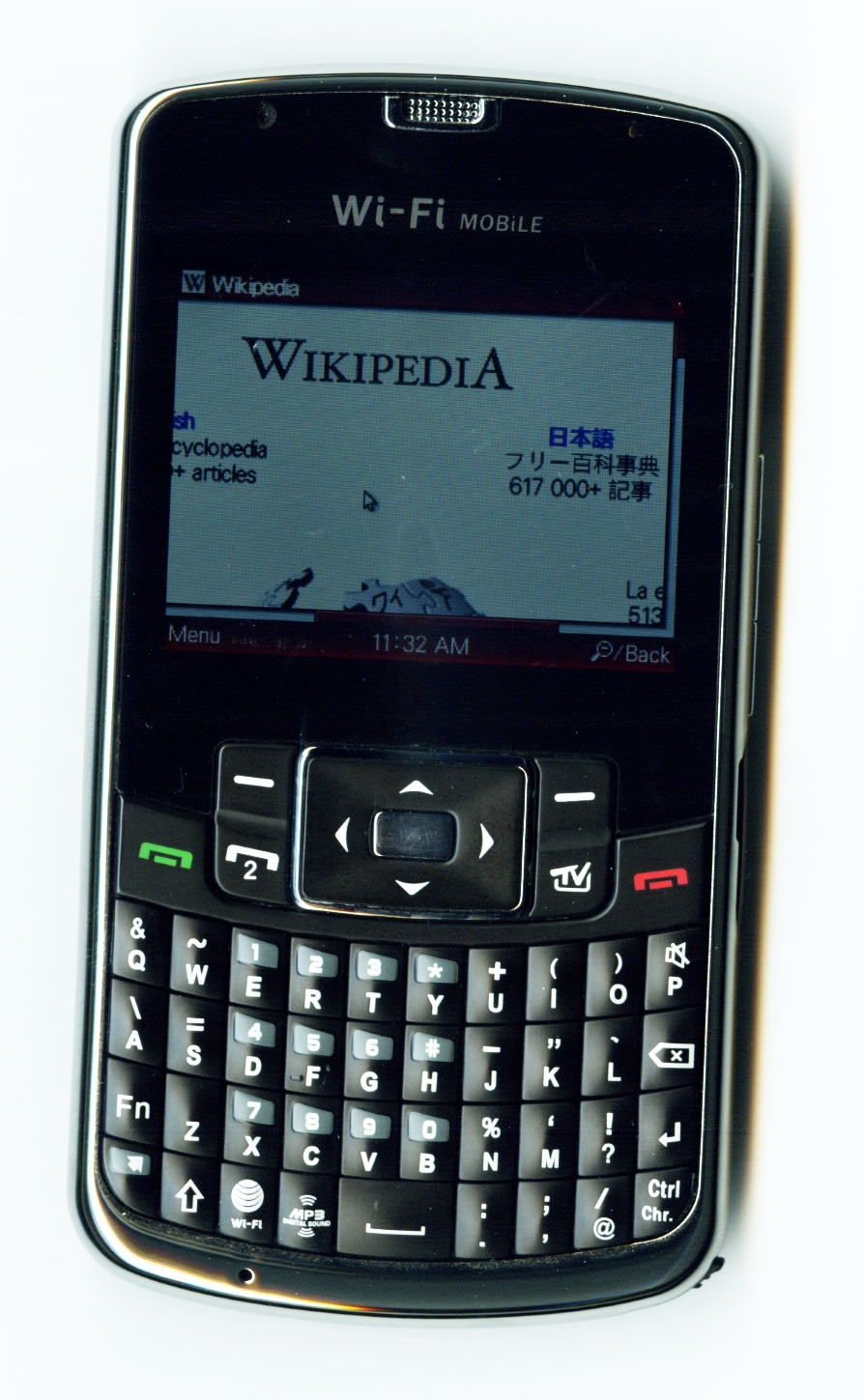

MT6235

{{refimprove, date=September 2014 The MT6235 is a processor used in many Chinese cellular phones (eg. ZTE). It is a member of the MT62xx series of processors by MediaTek. MediaTek-based Chinese cell phones often come with features not common to North American phones, such as analog television viewing and recording. While these phones have vastly different builds and configurations, they all run Mediatek's proprietary operating system based on the Nucleus RTOS. The MT6235 is a specialized processor design containing both an ARM926EJ-S RISC CPU running at frequencies between 26/52/104 and 208 MHz and a digital signal processor A digital signal processor (DSP) is a specialized microprocessor chip, with its architecture optimized for the operational needs of digital signal processing. DSPs are fabricated on MOS integrated circuit chips. They are widely used in audio si ... (DSP). Subsystems * Microcontroller Unit (MCU) Subsystem: includes an ARM926EJ-S RISC processor and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM7

ARM7 is a group of 32-bit RISC ARM processor cores licensed by ARM Holdings for microcontroller use. The ARM7 core family consists of ARM700, ARM710, ARM7DI, ARM710a, ARM720T, ARM740T, ARM710T, ARM7TDMI, ARM7TDMI-S, ARM7EJ-S. The ARM7TDMI and ARM7TDMI-S were the most popular cores of the family. Since ARM7 cores were released from 1993 to 2001, they are no longer recommended for new IC designs; instead ARM Cortex-M or ARM Cortex-R cores are preferred. Overview This generation introduced the Thumb 16-bit instruction set providing improved code density compared to previous designs. The most widely used ARM7 designs implement the ARMv4T architecture, but some implement ARMv3 or ARMv5TEJ. ARM7TDMI has 37 registers (31 GPR and 6 SPR). All these designs use a Von Neumann architecture, thus the few versions containing a cache do not separate data and instruction caches. Some ARM7 cores are obsolete. One historically significant model, the ARM7DI"ARM7DI Data Sheet"; Docu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |