|

Bobcat (microarchitecture)

The AMD Bobcat Family 14h is a microarchitecture created by AMD for its AMD APUs, aimed at a low-power/low-cost market. It was revealed during a speech from AMD executive vice-president Henri Richard in Computex 2007 and was put into production Q1 2011. One of the major supporters was executive vice-president Mario A. Rivas who felt it was difficult to compete in the x86 market with a single core optimized for the 10–100 W range and actively promoted the development of the simpler core with a target range of 1–10 W. In addition, it was believed that the core could migrate into the hand-held space if the power consumption can be reduced to less than 1 W. Bobcat cores are used together with GPU cores in accelerated processing units (APUs) under the "Fusion" brand. A simplified architecture diagram was released at AMD's Analyst Day in November 2009. This is similar in concept with earlier AMD research in 2003,AMD 2003 Microprocessor Forum SlidesSlide 11anSlide ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

List Of AMD Accelerated Processing Unit Microprocessors

This is a list of microprocessors designed by AMD containing a 3D integrated graphics processing unit (iGPU), including those under the AMD APU (Accelerated Processing Unit) product series. Features overview Graphics API overview Desktop processors with 3D graphics APU or Radeon Graphics branded Lynx: "Llano" (2011) * Socket FM1 * CPU: K10 (also ''Husky'' or ''K10.5'') cores with an upgraded ''Stars'' architecture, no L3 cache ** L1 cache: 64 KB Data per core and 64 KB Instruction cache per core ** L2 cache: 512 KB on dual-core, 1 MB on tri- and quad-core models ** '' MMX, Enhanced 3DNow!, SSE, SSE2, SSE3, SSE4a, ABM, NX bit, AMD64, Cool'n'Quiet'', ''AMD-V'' * GPU: TeraScale 2 (Evergreen); all A and E series models feature ''Redwood''-class integrated graphics on die (''BeaverCreek'' for the dual-core variants and ''WinterPark'' for the quad-core variants). Sempron and Athlon models exclude integrated graphics. * List of embedded GPU's * Support for up to four ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Streaming SIMD Extensions

In computing, Streaming SIMD Extensions (SSE) is a single instruction, multiple data ( SIMD) instruction set extension to the x86 architecture, designed by Intel and introduced in 1999 in its Pentium III series of central processing units (CPUs) shortly after the appearance of Advanced Micro Devices (AMD's) 3DNow!. SSE contains 70 new instructions (65 unique mnemonics using 70 encodings), most of which work on single precision floating-point data. SIMD instructions can greatly increase performance when exactly the same operations are to be performed on multiple data objects. Typical applications are digital signal processing and graphics processing. Intel's first IA-32 SIMD effort was the MMX instruction set. MMX had two main problems: it re-used existing x87 floating-point registers making the CPUs unable to work on both floating-point and SIMD data at the same time, and it only worked on integers. SSE floating-point instructions operate on a new independent register s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD X86 Microprocessors

Advanced Micro Devices, Inc. (AMD) is an American multinational corporation and technology company headquartered in Santa Clara, California and maintains significant operations in Austin, Texas. AMD is a hardware and fabless company that designs and develops central processing units (CPUs), graphics processing units (GPUs), field-programmable gate arrays (FPGAs), system-on-chip (SoC), and high-performance computer solutions. AMD serves a wide range of business and consumer markets, including gaming, data centers, artificial intelligence (AI), and embedded systems. AMD's main products include microprocessors, motherboard chipsets, embedded processors, and graphics processors for servers, workstations, personal computers, and embedded system applications. The company has also expanded into new markets, such as the data center, gaming, and high-performance computing markets. AMD's processors are used in a wide range of computing devices, including personal computers, servers ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ISSCC

International Solid-State Circuits Conference is a global forum for presentation of advances in solid-state circuits and Systems-on-a-Chip. The conference is held every year in February at the San Francisco Marriott Marquis in downtown San Francisco. ISSCC is sponsored by IEEE Solid-State Circuits Society. According to ''The Register'', "The ISSCC event is the second event of each new year, following the Consumer Electronics Show, where new PC processors and sundry other computing gadgets are brought to market." History of ISSCC Early participants in the inaugural conference in 1954 belonged to the Institute of Radio Engineers (IRE) Circuit Theory Group and the IRE subcommittee of Transistor Circuits. The conference was held in Philadelphia and local chapters of IRE and American Institute of Electrical Engineers (AIEE) were in attendance. Later on AIEE and IRE would merge to become the present-day IEEE. The first conference consisted of papers from six organizations: Bel ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

List Of AMD Processors With 3D Graphics

This is a list of microprocessors designed by AMD containing a 3D integrated graphics processing unit (iGPU), including those under the AMD APU (Accelerated Processing Unit) product series. Features overview Graphics API overview Desktop processors with 3D graphics APU or Radeon Graphics branded Lynx: "Llano" (2011) * Socket Socket FM1, FM1 * CPU: AMD 10h, K10 (also ''Husky'' or ''K10.5'') cores with an upgraded ''Stars'' architecture, no L3 cache ** L1 cache: 64 KB Data per core and 64 KB Instruction cache per core ** L2 cache: 512 KB on dual-core, 1 MB on tri- and quad-core models ** ''MMX (instruction set), MMX, 3DNow!, Enhanced 3DNow!, Streaming SIMD Extensions, SSE, SSE2, SSE3, SSE4a, Bit Manipulation Instruction Sets#ABM (Advanced Bit Manipulation), ABM, NX bit, Amd64, AMD64, Cool'n'Quiet'', ''AMD-V'' * GPU: TeraScale 2, TeraScale 2 (Evergreen); all A and E series models feature ''Redwood''-class integrated graphics on die (''BeaverCreek'' for the dual-core varia ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

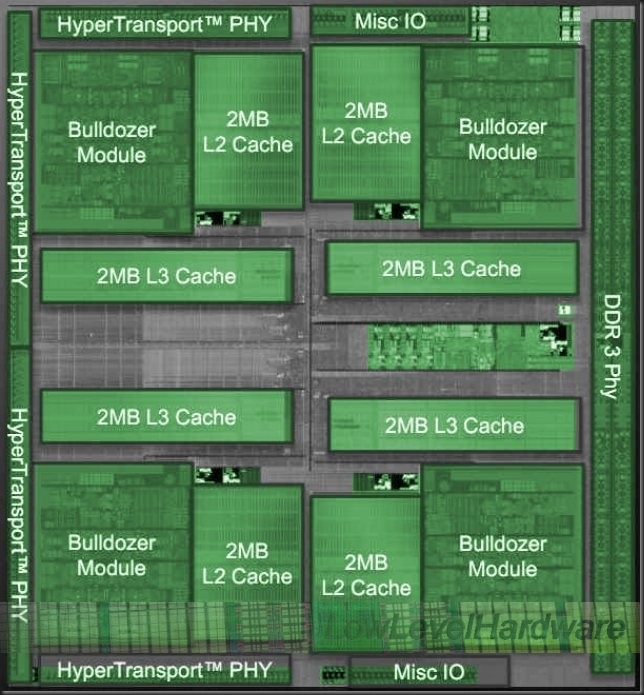

Bulldozer (processor)

The AMD Bulldozer Family 15h is a microprocessor microarchitecture for the FX and Opteron line of processors, developed by AMD for the desktop and server markets. Bulldozer is the codename for this family of microarchitectures. It was released on October 12, 2011, as the successor to the K10 microarchitecture. Bulldozer is designed from scratch, not a development of earlier processors. The core is specifically aimed at computing products with TDPs of 10 to 125 watts. AMD claims dramatic performance-per-watt efficiency improvements in high-performance computing (HPC) applications with Bulldozer cores. The ''Bulldozer'' cores support most of the instruction sets implemented by Intel processors (Sandy Bridge) available at its introduction (including SSSE3, SSE4.1, SSE4.2, AES, CLMUL, and AVX) as well as new instruction sets proposed by AMD; ABM, XOP, FMA4 and F16C. Only Bulldozer GEN4 (Excavator) supports AVX2 instruction sets. Overview According to AMD, Bull ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Watt

The watt (symbol: W) is the unit of Power (physics), power or radiant flux in the International System of Units (SI), equal to 1 joule per second or 1 kg⋅m2⋅s−3. It is used to quantification (science), quantify the rate of Work (physics), energy transfer. The watt is named in honor of James Watt (1736–1819), an 18th-century Scottish people, Scottish inventor, mechanical engineer, and chemist who improved the Newcomen engine with his own Watt steam engine, steam engine in 1776, which became fundamental for the Industrial Revolution. Overview When an object's velocity is held constant at one meter per second against a constant opposing force of one Newton (unit), newton, the rate at which Work (physics), work is done is one watt. \mathrm. In terms of electromagnetism, one watt is the rate at which electrical work is performed when a current of one ampere (A) flows across an electrical potential difference of one volt (V), meaning the watt is equivalent to the vo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Hertz

The hertz (symbol: Hz) is the unit of frequency in the International System of Units (SI), often described as being equivalent to one event (or Cycle per second, cycle) per second. The hertz is an SI derived unit whose formal expression in terms of SI base units is 1/s or s−1, meaning that one hertz is one per second or the Inverse second, reciprocal of one second. It is used only in the case of periodic events. It is named after Heinrich Hertz, Heinrich Rudolf Hertz (1857–1894), the first person to provide conclusive proof of the existence of electromagnetic waves. For high frequencies, the unit is commonly expressed in metric prefix, multiples: kilohertz (kHz), megahertz (MHz), gigahertz (GHz), terahertz (THz). Some of the unit's most common uses are in the description of periodic waveforms and musical tones, particularly those used in radio- and audio-related applications. It is also used to describe the clock speeds at which computers and other electronics are driven. T ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD CMC60

Advanced Micro Devices, Inc. (AMD) is an American multinational corporation and technology company headquartered in Santa Clara, California and maintains significant operations in Austin, Texas. AMD is a hardware and fabless company that designs and develops central processing units (CPUs), graphics processing units (GPUs), field-programmable gate arrays (FPGAs), system-on-chip (SoC), and high-performance computer solutions. AMD serves a wide range of business and consumer markets, including gaming, data centers, artificial intelligence (AI), and embedded systems. AMD's main products include microprocessors, motherboard chipsets, embedded processors, and graphics processors for servers, workstations, personal computers, and embedded system applications. The company has also expanded into new markets, such as the data center, gaming, and high-performance computing markets. AMD's processors are used in a wide range of computing devices, including personal computers, servers, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Bit Manipulation Instruction Sets

Bit manipulation instructions sets (BMI sets) are extensions to the x86 instruction set architecture for microprocessors from Intel and AMD. The purpose of these instruction sets is to improve the speed of bit manipulation. All the instructions in these sets are non-SIMD and operate only on general-purpose registers. There are two sets published by Intel: BMI (now referred to as BMI1) and BMI2; they were both introduced with the Haswell microarchitecture with BMI1 matching features offered by AMD's ABM instruction set and BMI2 extending them. Another two sets were published by AMD: ABM (''Advanced Bit Manipulation'', which is also a subset of SSE4a implemented by Intel as part of SSE4.2 and BMI1), and TBM (''Trailing Bit Manipulation'', an extension introduced with Piledriver-based processors as an extension to BMI1, but dropped again in Zen-based processors). ABM (Advanced Bit Manipulation) AMD was the first to introduce the instructions that now form Intel's BMI1 as part ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SSE4a

SSE4 (Streaming SIMD Extensions 4) is a SIMD CPU instruction set used in the Intel Core microarchitecture and AMD K10 (K8L). It was announced on September 27, 2006, at the Fall 2006 Intel Developer Forum, with vague details in a white paper;Intel Streaming SIMD Extensions 4 (SSE4) Instruction Set Innovation , Intel. more precise details of 47 instructions became available at the Spring 2007 Intel Developer Forum in , in the presentation. SSE4 extended the instruction set which was released in early 2004. All software using ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |