Floor planning on:

[Wikipedia]

[Google]

[Amazon]

In

In

A sliceable floorplan is a floorplan that may be defined recursively as described below. "The Electrical Engineering Handbook", Richard C. Dorf (1997)

*A floorplan that consists of a single rectangular block is sliceable.

*If a block from a sliceable floorplan is cut ("sliced") in two by a vertical or horizontal line, the resulting floorplan is sliceable.

Sliceable floorplans have been used in a number of early

A sliceable floorplan is a floorplan that may be defined recursively as described below. "The Electrical Engineering Handbook", Richard C. Dorf (1997)

*A floorplan that consists of a single rectangular block is sliceable.

*If a block from a sliceable floorplan is cut ("sliced") in two by a vertical or horizontal line, the resulting floorplan is sliceable.

Sliceable floorplans have been used in a number of early

Transforming an arbitrary floorplan into a sliceable one

, Proc. 1993 IEEE/ACM International Conference on Computer-Aided Design (ICCAD-93), pp. 386-389.

In

In electronic design automation

Electronic design automation (EDA), also referred to as electronic computer-aided design (ECAD), is a category of software tools for designing Electronics, electronic systems such as integrated circuits and printed circuit boards. The tools wo ...

, a floorplan of an integrated circuit

An integrated circuit or monolithic integrated circuit (also referred to as an IC, a chip, or a microchip) is a set of electronic circuits on one small flat piece (or "chip") of semiconductor material, usually silicon. Large numbers of tiny ...

is a schematics representation of tentative placement of its major functional blocks.

In modern electronic design process floorplans are created during the floorplanning design stage, an early stage in the hierarchical approach to integrated circuit design.

Depending on the design methodology being followed, the actual definition of a floorplan may differ.

Floorplanning

Floorplanning takes in some of the geometrical constraints in a design. Here are some examples: * bonding pads for off-chip connections (often using wire bonding) are normally located at the circumference of the chip; * line drivers often have to be located as close to bonding pads as possible; * chip area is therefore in some cases given a minimum area in order to fit in the required number of pads; * areas are clustered in order to limit data paths thus frequently featuring defined structures such as cache RAM, multiplier,barrel shifter

A barrel shifter is a digital circuit that can shift a data word by a specified number of bits without the use of any sequential logic, only pure combinational logic, i.e. it inherently provides a binary operation. It can however in theory also ...

, line driver and arithmetic logic unit

In computing, an arithmetic logic unit (ALU) is a Combinational logic, combinational digital circuit that performs arithmetic and bitwise operations on integer binary numbers. This is in contrast to a floating-point unit (FPU), which operates on ...

;

* purchased intellectual property blocks ( IP-blocks), such as a processor core, come in predefined area blocks;

* some IP-blocks come with legal limitations such as permitting no routing of signals directly above the block.

Mathematical models and optimization problems

In some approaches the floorplan may be a partition of the whole chip area intoaxis aligned rectangle

A rectilinear polygon is a polygon all of whose sides meet at right angles. Thus the interior angle at each vertex is either 90° or 270°. Rectilinear polygons are a special case of isothetic polygons.

In many cases another definition is pr ...

s to be occupied by IC blocks. This partition is subject to various constraints and requirements of optimization: block area, aspect ratios, estimated total measure of interconnects, etc.

Finding good floorplans has been a research area in combinatorial optimization. Most of the problems related to finding optimal floorplans are NP-hard

In computational complexity theory, NP-hardness ( non-deterministic polynomial-time hardness) is the defining property of a class of problems that are informally "at least as hard as the hardest problems in NP". A simple example of an NP-hard pr ...

, i.e., require vast computational resources. Therefore, the most common approach is to use various optimization heuristics for finding good solutions.

Another approach is to restrict design methodology to certain classes of floorplans, such as sliceable floorplans.

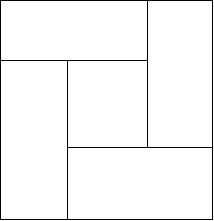

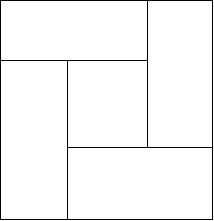

Sliceable floorplans

A sliceable floorplan is a floorplan that may be defined recursively as described below. "The Electrical Engineering Handbook", Richard C. Dorf (1997)

*A floorplan that consists of a single rectangular block is sliceable.

*If a block from a sliceable floorplan is cut ("sliced") in two by a vertical or horizontal line, the resulting floorplan is sliceable.

Sliceable floorplans have been used in a number of early

A sliceable floorplan is a floorplan that may be defined recursively as described below. "The Electrical Engineering Handbook", Richard C. Dorf (1997)

*A floorplan that consists of a single rectangular block is sliceable.

*If a block from a sliceable floorplan is cut ("sliced") in two by a vertical or horizontal line, the resulting floorplan is sliceable.

Sliceable floorplans have been used in a number of early Electronic Design Automation

Electronic design automation (EDA), also referred to as electronic computer-aided design (ECAD), is a category of software tools for designing Electronics, electronic systems such as integrated circuits and printed circuit boards. The tools wo ...

tools for a number of reasons. Sliceable floorplans may be conveniently represented by binary tree

In computer science, a binary tree is a k-ary k = 2 tree data structure in which each node has at most two children, which are referred to as the ' and the '. A recursive definition using just set theory notions is that a (non-empty) binary t ...

s (more specifically, ''k''-d trees), which correspond to the order of slicing. More importantly, a number of NP-hard problems with floorplans have polynomial time

In computer science, the time complexity is the computational complexity that describes the amount of computer time it takes to run an algorithm. Time complexity is commonly estimated by counting the number of elementary operations performed by ...

algorithms when restricted to sliceable floorplans.Sarrafzadeh, M,Transforming an arbitrary floorplan into a sliceable one

, Proc. 1993 IEEE/ACM International Conference on Computer-Aided Design (ICCAD-93), pp. 386-389.

Further reading

References

{{reflist Electronic design automation Electronics optimization Combinatorial optimization