|

Wafer Testing

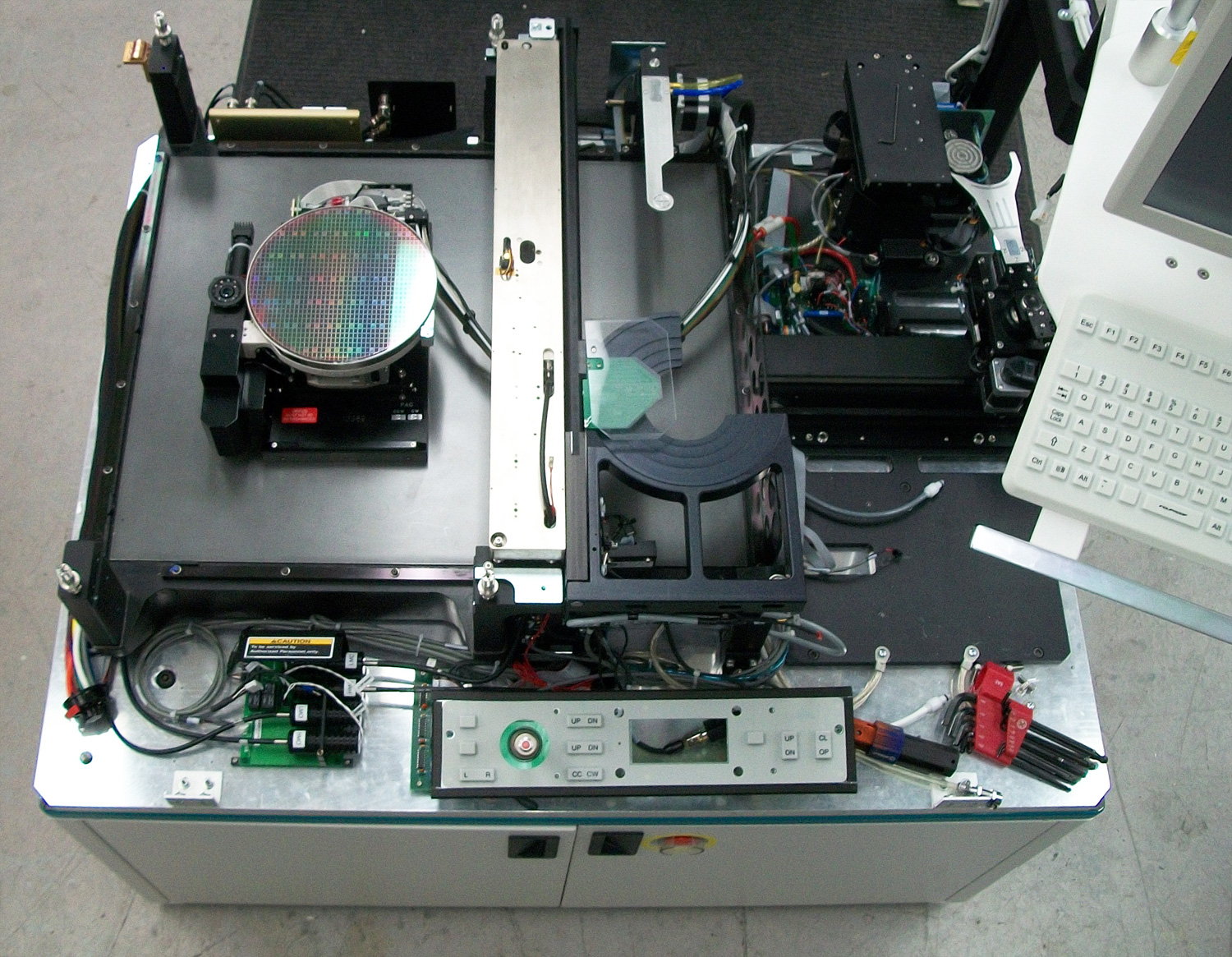

Wafer testing is a step performed during semiconductor device fabrication after BEOL process is finished. During this step, performed before a wafer is sent to die preparation, all individual integrated circuits that are present on the wafer are tested for functional defects by applying special test patterns to them. The wafer testing is performed by a piece of test equipment called a wafer prober. The process of wafer testing can be referred to in several ways: Wafer Final Test (WFT), Electronic Die Sort (EDS) and Circuit Probe (CP) are probably the most common. Wafer prober A wafer prober is a machine used for integrated circuits verification against designed functionality. It's either manual or automatic test equipment. For electrical testing a set of microscopic contacts or probes called a probe card are held in place whilst the wafer, vacuum-mounted on a wafer chuck, is moved into electrical contact. When a die (or array of dice) have been electrically tested the prober mo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Fabrication (semiconductor)

Semiconductor device fabrication is the process used to manufacture semiconductor devices, typically integrated circuit (IC) chips such as modern computer processors, microcontrollers, and memory chips such as NAND flash and DRAM that are present in everyday electrical and electronic devices. It is a multiple-step sequence of photolithographic and chemical processing steps (such as surface passivation, thermal oxidation, planar diffusion and junction isolation) during which electronic circuits are gradually created on a wafer made of pure semiconducting material. Silicon is almost always used, but various compound semiconductors are used for specialized applications. The entire manufacturing process takes time, from start to packaged chips ready for shipment, at least six to eight weeks (tape-out only, not including the circuit design) and is performed in highly specialized semiconductor fabrication plants, also called foundries or fabs. All fabrication takes place inside a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Chip-scale Package

A chip scale package or chip-scale package (CSP) is a type of integrated circuit package. Originally, CSP was the acronym for ''chip-size packaging.'' Since only a few packages are chip size, the meaning of the acronym was adapted to ''chip-scale packaging''. According to IPC's standard J-STD-012, ''Implementation of Flip Chip and Chip Scale Technology'', in order to qualify as chip scale, the package must have an area no greater than 1.2 times that of the die and it must be a single-die, direct surface mountable package. Another criterion that is often applied to qualify these packages as CSPs is their ball pitch should be no more than 1 mm. The concept was first proposed by Junichi Kasai of Fujitsu and Gen Murakami of Hitachi Cable in 1993. The first concept demonstration however came from Mitsubishi Electric. The die may be mounted on an interposer upon which pads or balls are formed, like with flip chip ball grid array (BGA) packaging, or the pads may be etched or pr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Bond Characterization

The wafer bond characterization is based on different methods and tests. Considered a high importance of the wafer are the successful bonded wafers without flaws. Those flaws can be caused by void formation in the interface due to unevenness or impurities. The bond connection is characterized for wafer bond development or quality assessment of fabricated wafers and sensors. Overview Wafer bonds are commonly characterized by three important encapsulation parameters: bond strength, hermeticity of encapsulation and bonding induced stress. The bond strength can be evaluated using double cantilever beam or chevron respectively micro-chevron tests. Other pull tests as well as burst, direct shear tests or bend tests enable the determination of the bond strength. The packaging hermeticity is characterized using membrane, He-leak, resonator/pressure tests. Three additional possibilities to evaluate the bond connection are optical, electron and Acoustical measurements and instrumentati ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Semiconductor Fabrication

Semiconductor device fabrication is the process used to manufacture semiconductor devices, typically integrated circuit (IC) chips such as modern computer processors, microcontrollers, and memory chips such as NAND flash and DRAM that are present in everyday electrical and electronic devices. It is a multiple-step sequence of photolithographic and chemical processing steps (such as surface passivation, thermal oxidation, planar diffusion and junction isolation) during which electronic circuits are gradually created on a wafer made of pure semiconducting material. Silicon is almost always used, but various compound semiconductors are used for specialized applications. The entire manufacturing process takes time, from start to packaged chips ready for shipment, at least six to eight weeks (tape-out only, not including the circuit design) and is performed in highly specialized semiconductor fabrication plants, also called foundries or fabs. All fabrication takes place inside a c ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Test Program

Test(s), testing, or TEST may refer to: * Test (assessment), an educational assessment intended to measure the respondents' knowledge or other abilities Arts and entertainment * ''Test'' (2013 film), an American film * ''Test'' (2014 film), a Russian film * ''Test'' (group), a jazz collective * ''Tests'' (album), a 1998 album by The Microphones Computing * .test, a reserved top-level domain * test (Unix), a Unix command for evaluating conditional expressions * TEST (x86 instruction), an x86 assembly language instruction People * Test (wrestler), ring name for Andrew Martin (1975–2009), Canadian professional wrestler * John Test (1771–1849), American politician * Zack Test (born 1989), American rugby union player Science and technology * Proof test * Stress testing * Test (biology), the shell of sea urchins and certain microorganisms * Test equipment Sports * Test cricket, a series of matches played by two national representative teams * Test match (rugby league), ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CPU Cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (MMU) w ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Substrate Mapping

Substrate mapping (or wafer mapping) is a process in which the performance of semiconductor devices on a substrate is represented by a map showing the performance as a colour-coded grid. The map is a convenient representation of the variation in performance across the substrate, since the distribution of those variations may be a clue as to their cause. The concept also includes the package of data generated by modern wafer testing equipment which can be transmitted to equipment used for subsequent 'back-end' manufacturing operations. History The initial process supported by substrate maps was inkless binning. Each tested die is assigned a bin value, depending on the result of the test. For example, a pass die is assigned a bin value of 1 for a good bin, bin 10 for an open circuit, and bin 11 for a short circuit. In the very early days of wafer test, the dies were put in different bins or buckets, depending on the test results. Physical binning may no longer be used, but the ana ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Die Attachment

In electronics manufacturing, integrated circuit packaging is the final stage of semiconductor device fabrication, in which the block of semiconductor material is encapsulated in a supporting case that prevents physical damage and corrosion. The case, known as a " package", supports the electrical contacts which connect the device to a circuit board. In the integrated circuit industry, the process is often referred to as packaging. Other names include semiconductor device assembly, assembly, encapsulation or sealing. The packaging stage is followed by testing of the integrated circuit. The term is sometimes confused with electronic packaging, which is the mounting and interconnecting of integrated circuits (and other components) onto printed-circuit boards. Design considerations Electrical The current-carrying traces that run out of the die, through the package, and into the printed circuit board (PCB) have very different electrical properties compared to on-chip signa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Integrated Circuit Packaging

In electronics manufacturing, integrated circuit packaging is the final stage of semiconductor device fabrication, in which the block of semiconductor material is encapsulated in a supporting case that prevents physical damage and corrosion. The case, known as a " package", supports the electrical contacts which connect the device to a circuit board. In the integrated circuit industry, the process is often referred to as packaging. Other names include semiconductor device assembly, assembly, encapsulation or sealing. The packaging stage is followed by testing of the integrated circuit. The term is sometimes confused with electronic packaging, which is the mounting and interconnecting of integrated circuits (and other components) onto printed-circuit boards. Design considerations Electrical The current-carrying traces that run out of the die, through the package, and into the printed circuit board (PCB) have very different electrical properties compared to on-chip signal ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Contact Pad

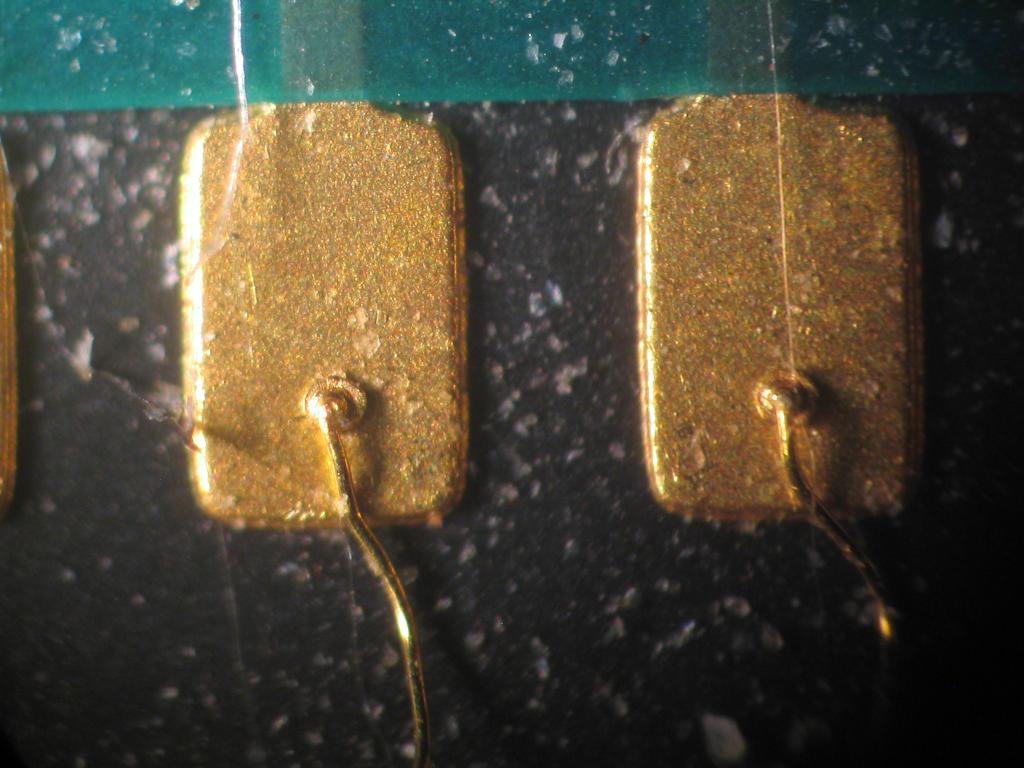

Contact pads or bond pads are designated surface areas of a printed circuit board (PCB) or die of an integrated circuit. Possibilities to contact to pads include soldering, wirebonding, flip chip Flip chip, also known as controlled collapse chip connection or its abbreviation, C4, is a method for interconnecting dies such as semiconductor devices, IC chips, integrated passive devices and microelectromechanical systems (MEMS), to exter ... mounting, or probe needles. Further reading *Kraig Mitzner, ''Complete PCB Design Using OrCAD Capture and PCB Editor'', Newnes, 2009 . *Jing Li, ''Evaluation and Improvement of the Robustness of a PCB Pad in a Lead-free Environment'', ProQuest, 2007 . *Deborah Lea, Fredirikus Jonck, Christopher Hunt, ''Solderability Measurements of PCB Pad Finishes and Geometries'', National Physical Laboratory, 2001 . Electronic engineering Printed circuit board manufacturing {{Electronics-stub ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Back End Of Line

The back end of line (BEOL) is the second portion of IC fabrication where the individual devices (transistors, capacitors, resistors, etc.) get interconnected with wiring on the wafer, the metalization layer. Common metals are copper and aluminum. BEOL generally begins when the first layer of metal is deposited on the wafer. BEOL includes contacts, insulating layers (dielectrics), metal levels, and bonding sites for chip-to-package connections. After the last FEOL step, there is a wafer with isolated transistors (without any wires). In BEOL part of fabrication stage contacts (pads), interconnect wires, vias and dielectric structures are formed. For modern IC process, more than 10 metal layers can be added in the BEOL. Steps of the BEOL: # Silicidation of source and drain regions and the polysilicon region. # Adding a dielectric (first, lower layer is pre-metal dielectric (PMD) – to isolate metal from silicon and polysilicon), CMP processing it # Make holes in PMD, make a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Probe Card

A probe card is an interface between an electronic test system and a semiconductor wafer. Typically the probe card is mechanically docked to a prober and electrically connected to a tester. Its purpose is to provide an electrical path between the test system and the circuits on the wafer, thereby permitting the testing and validation of the circuits at the wafer level, usually before they are diced and packaged. It consists, normally, of a printed circuit board (PCB) and some form of contact elements, usually metallic, but possibly of other materials as well. A semiconductor manufacturer will typically require a new probe card for each new device wafer and for device shrinks (when the manufacturer reduces the size of the device while keeping its functionality) because the probe card is effectively a custom connector that takes the universal pattern of a given tester and translates the signals to connect to electrical pads on the wafer. For testing of DRAM and FLASH memory dev ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |