|

Quad-channel Architecture

Quad-channel computer memory is a memory bus technology used by AMD Socket G34 released on May, 2010, with Opteron 6100-series "Magny-Cours" (45 nm) and later by the Intel X79 chipset released on November, 2011, for LGA2011-based Core i7 CPUs utilizing the Sandy Bridge microarchitecture. It is the successor of the triple-channel architecture used by the Intel X58 chipset for LGA1366-based CPUs. See also *Multi-channel memory architecture References {{reflist Computer memory ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Computer Memory

In computing, memory is a device or system that is used to store information for immediate use in a computer or related computer hardware and digital electronic devices. The term ''memory'' is often synonymous with the term ''primary storage'' or '' main memory''. An archaic synonym for memory is store. Computer memory operates at a high speed compared to storage that is slower but less expensive and higher in capacity. Besides storing opened programs, computer memory serves as disk cache and write buffer to improve both reading and writing performance. Operating systems borrow RAM capacity for caching so long as not needed by running software. If needed, contents of the computer memory can be transferred to storage; a common way of doing this is through a memory management technique called ''virtual memory''. Modern memory is implemented as semiconductor memory, where data is stored within memory cells built from MOS transistors and other components on an integrated c ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Memory Bus

In computer architecture, a bus (shortened form of the Latin '' omnibus'', and historically also called data highway or databus) is a communication system that transfers data between components inside a computer, or between computers. This expression covers all related hardware components (wire, optical fiber, etc.) and software, including communication protocols. Early computer buses were parallel electrical wires with multiple hardware connections, but the term is now used for any physical arrangement that provides the same logical function as a parallel electrical busbar. Modern computer buses can use both parallel and bit serial connections, and can be wired in either a multidrop (electrical parallel) or daisy chain topology, or connected by switched hubs, as in the case of Universal Serial Bus (USB). Background and nomenclature Computer systems generally consist of three main parts: * The central processing unit (CPU) that processes data, * The memory that holds the p ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Socket G34

Socket G34 is a land grid array CPU socket designed by AMD to support AMD's multi-chip module Opteron 6000-series server processors. G34 was launched on March 29, 2010, alongside the initial grouping of Opteron 6100 processors designed for it. Socket G34 supports four DDR3 SDRAM channels, two for each die in the 1944 pin CPU package. Socket G34 is available in up to four-socket arrangements, which is a change from the Socket F CPUs supporting up to eight-socket arrangements. However, four Socket G34 CPUs have eight dies, which is identical to what eight Socket F CPUs have. AMD declined to extend Socket G34 to eight-way operation citing shrinking demand of the >4-socket market. AMD is targeting Socket G34 at the high-end two-socket market and the four-socket market. The lower-end two-socket market will be serviced by monolithic-die Socket C32 CPUs with half the core count as the equivalent Socket G34 CPUs. Both Socket G34 and its contemporary Socket C32 were succeeded in 2017 by So ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel X79

The Intel X79 ( codenamed ''Patsburg'') is a Platform Controller Hub (PCH) designed and manufactured by Intel for their LGA 2011 (Socket R) and LGA 2011-1 (Socket R2). Socket and chipset support CPUs targeted at the high-end desktop (HEDT) and enthusiast segments of the Intel product lineup: Core i7-branded and Xeon-branded processors from the Sandy Bridge and Ivy Bridge CPU architectures. The supported CPUs feature quad channel memory controllers, and a certain number of PCIe lanes, the chipset features additional PCIe lanes; it is designed to connect an Intel processor through a DMI 2.0 interface to peripheral devices. Features The first product was announced on November 14, 2011, for "Extreme" CPUs using the LGA 2011 socket. Features include: * 2× Serial ATA (SATA) 3.0 (6Gbit/s) ports & 4x SATA 2 (3Gbit/s) ports. * 8× PCI Express 2.0 lanes * 14 Universal Serial Bus (USB) 2.0 ports * Integrated Gigabit Ethernet MAC (Lewisville PHY) * Optional Intel Rapid Storage Technolo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

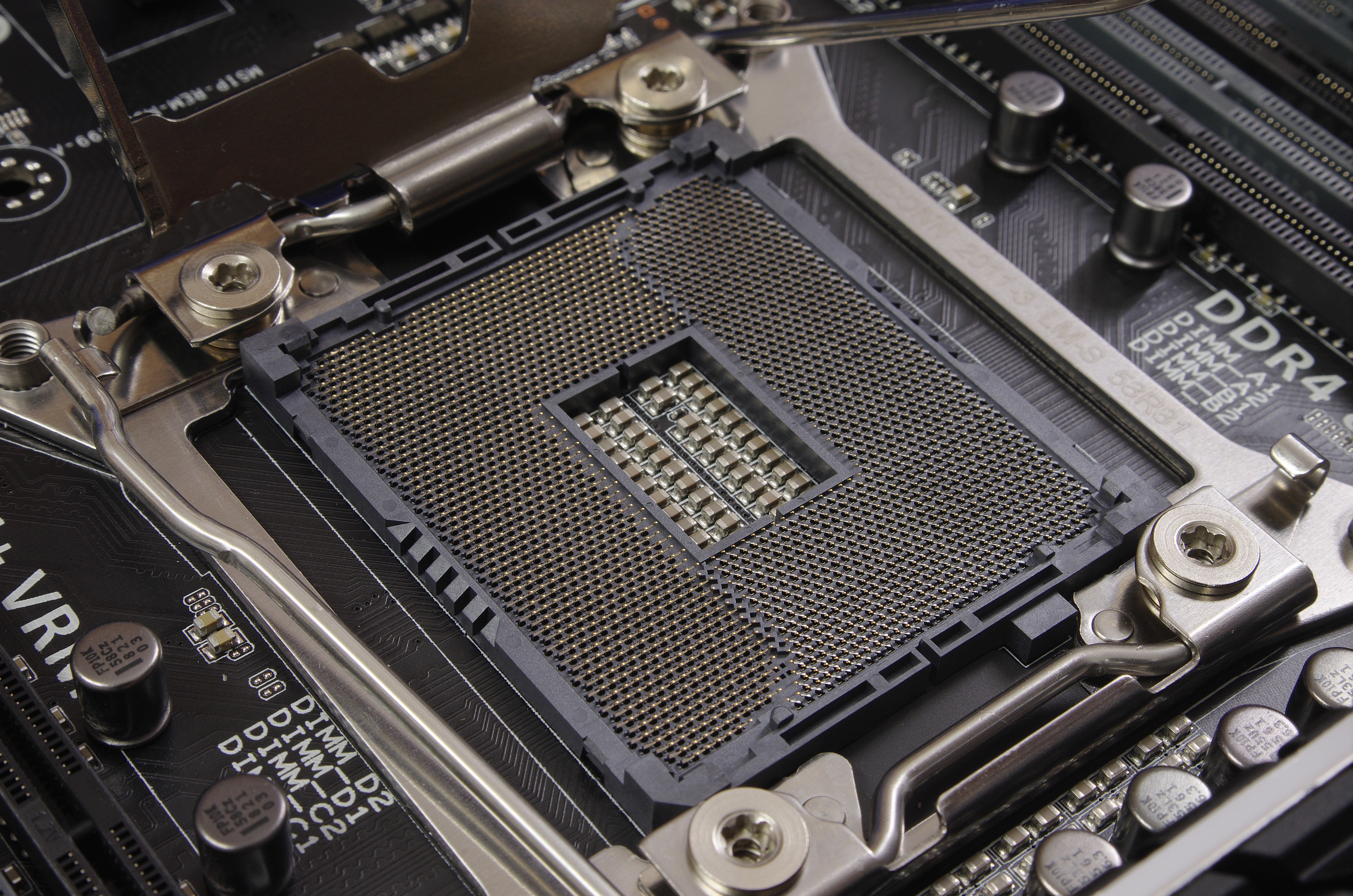

LGA2011

LGA 2011, also called ''Socket R'', is a CPU socket by Intel released on November 14, 2011. It launched along with LGA 1356 to replace its predecessor, LGA 1366 (Socket B) and LGA 1567. While LGA 1356 was designed for dual-processor or low-end servers, LGA 2011 was designed for high-end desktops and high-performance servers. The socket has 2011 protruding pins that touch contact points on the underside of the processor. The LGA 2011 socket uses QPI to connect the CPU to additional CPUs. DMI 2.0 is used to connect the processor to the PCH. The memory controller and 40 PCI Express (PCIe) lanes are integrated on the CPU. On a secondary processor an extra ×4 PCIe interface replaces the DMI interface. As with its predecessor LGA 1366, there is no provisioning for integrated graphics. This socket supports four DDR3 or DDR4 SDRAM memory channels with up to three unbuffered or registered DIMMs per channel, as well as up to 40 PCI Express 2.0 or 3.0 lanes. LGA ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Core I7

The following is a list of Intel Core i7 brand microprocessors. Introduced in 2008, the Core i7 line of microprocessors are intended to be used by high-end users. Desktop processors Nehalem microarchitecture (1st generation) "Bloomfield" (45 nm) * All models support: MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, Enhanced Intel SpeedStep Technology (EIST), Intel 64, XD bit (an NX bit implementation), Intel VT-x, Hyper-threading, Turbo Boost, Smart Cache. * FSB has been replaced with QPI. * Transistors: 731 million * Die size: 263 mm * Steppings: C0, D0 "Lynnfield" (45 nm) * All models support: MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, Enhanced Intel SpeedStep Technology (EIST), Intel 64, XD bit (an NX bit implementation), TXT, Intel VT-x, Intel VT-d, Hyper-threading, Turbo Boost, Smart Cache. * Core i7-875K features an unlocked multiplier and does not support Intel TXT and Intel VT-d. * FSB has been replaced with DMI. *Moves the QPI link and PCI ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Sandy Bridge

Sandy Bridge is the codename for Intel's 32 nm microarchitecture used in the second generation of the Intel Core processors (Core i7, i5, i3). The Sandy Bridge microarchitecture is the successor to Nehalem and Westmere microarchitecture. Intel demonstrated a Sandy Bridge processor in 2009, and released first products based on the architecture in January 2011 under the Core brand. Sandy Bridge is manufactured in the 32 nm process and has a soldered contact with the die and IHS (Integrated Heat Spreader), while Intel's subsequent generation Ivy Bridge uses a 22 nm die shrink and a TIM (Thermal Interface Material) between the die and the IHS. Technology Intel demonstrated a Sandy Bridge processor with A1 stepping at 2 GHz during the Intel Developer Forum in September 2009. Upgraded features from Nehalem include: CPU * Intel Turbo Boost 2.0 * 32 KB data + 32 KB instruction L1 cache and 256 KB L2 cache per core * Shared L3 cache which inclu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Microarchitecture

In computer engineering, microarchitecture, also called computer organization and sometimes abbreviated as µarch or uarch, is the way a given instruction set architecture (ISA) is implemented in a particular processor. A given ISA may be implemented with different microarchitectures; implementations may vary due to different goals of a given design or due to shifts in technology. Computer architecture is the combination of microarchitecture and instruction set architecture. Relation to instruction set architecture The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the instructions, execution model, processor registers, address and data formats among other things. The microarchitecture includes the constituent parts of the processor and how these interconnect and interoperate to implement the ISA. The microarchitecture of a machine is usually represented as (more or less detai ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Triple-channel

In the fields of digital electronics and computer hardware, multi-channel memory architecture is a technology that increases the data transfer rate between the DRAM memory and the memory controller by adding more channels of communication between them. Theoretically, this multiplies the data rate by exactly the number of channels present. Dual-channel memory employs two channels. The technique goes back as far as the 1960s having been used in IBM System/360 Model 91 and in CDC 6600. Modern high-end desktop and workstation processors such as the AMD Ryzen Threadripper series and the Intel Core i9 Extreme Edition lineup support quad-channel memory. Server processors from the AMD Epyc series and the Intel Xeon platforms give support to memory bandwidth starting from quad-channel module layout to up to octa-channel layout. In March 2010, AMD released Socket G34 and Magny-Cours Opteron 6100 series processors with support for quad-channel memory. In 2006, Intel released chips ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel X58

The Intel X58 ( codenamed ''Tylersburg'') is an Intel chip designed to connect Intel processors with Intel QuickPath Interconnect (QPI) interface to peripheral devices. Supported processors implement the Nehalem microarchitecture and therefore have an integrated memory controller (IMC), so the X58 does not have a memory interface. Initially supported processors were the Core i7, but the chip also supported Nehalem and Westmere-based Xeon processors. Description The QuickPath architecture differs considerably from earlier Intel architectures, and is much closer to AMD's HyperTransport architecture. Except for the lack of a memory interface, the X58 is similar to the traditional northbridge: it communicates with the processor(s) via the high bandwidth QuickPath Interconnect, it communicates with the southbridge via Direct Media Interface (DMI), and it communicates with high bandwidth peripherals via PCI Express (PCIe). The X58 is not a ''memory controller hub'' (MCH), becaus ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

LGA1366

LGA 1366 (land grid array 1366), also known as Socket B, is an Intel CPU socket. This socket supersedes Intel's LGA 775 (Socket T) in the high-end and performance desktop segments. It also replaces the server-oriented LGA 771 (Socket J) in the entry level and is superseded itself by LGA 2011. This socket has 1,366 protruding pins which touch contact points on the underside of the processor (CPU) and accesses up to three channels of DDR3 memory via the processor's internal memory controller. Socket 1366 (Socket B) uses Intel QuickPath Interconnect (QPI) to connect the CPU to a reduced-function northbridge that serves mainly as a PCI-Express controller. A slower DMI is used to connect Intel's most recent northbridge and southbridge components. By comparison, Intel's LGA 1156 (Socket H) moves the QPI link and PCI-Express controller onto the processor itself, using DMI to interface a single-component "chipset" (now called PCH) that serves traditional southbridge functions. The d ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Multi-channel Memory Architecture

In the fields of digital electronics and computer hardware, multi-channel memory architecture is a technology that increases the data transfer rate between the DRAM memory and the memory controller by adding more channels of communication between them. Theoretically, this multiplies the data rate by exactly the number of channels present. Dual-channel memory employs two channels. The technique goes back as far as the 1960s having been used in IBM System/360 Model 91 and in CDC 6600. Modern high-end desktop and workstation processors such as the AMD Ryzen Threadripper series and the Intel Core i9 Extreme Edition lineup support quad-channel memory. Server processors from the AMD Epyc series and the Intel Xeon platforms give support to memory bandwidth starting from quad-channel module layout to up to octa-channel layout. In March 2010, AMD released Socket G34 and Magny-Cours Opteron 6100 series processors with support for quad-channel memory. In 2006, Intel released chipsets that s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

.jpg)

.jpg)