|

Program Status Word

The program status word (PSW) is a register that performs the function of a status register and program counter, and sometimes more. The term is also applied to a copy of the PSW in storage. This article only discusses the PSW in the IBM System/360 and its successors, and follows the IBM convention of numbering bits starting with 0 as the leftmost (most significant) bit. Although certain fields within the PSW may be tested or set by using non-privileged instructions, testing or setting the remaining fields may only be accomplished by using privileged instructions. Contained within the PSW are the two bit condition code, representing zero, positive, negative, overflow, and similar flags of other architectures' status registers. Conditional branch instructions test this encoded as a four bit value, with each bit representing a test of one of the four condition code values, 23 + 22 + 21 + 20. (Since IBM uses big-endian bit numbering, mask value 8 selects code 0, mask value 4 sele ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Status Register

A status register, flag register, or condition code register (CCR) is a collection of status Flag (computing), flag bits for a Central processing unit, processor. Examples of such registers include FLAGS register (computing), FLAGS register in the x86 architecture, flags in the program status word (PSW) register in the IBM System/360 architecture through z/Architecture, and the application program status register (APSR) in the ARM Cortex-A architecture. The status register is a hardware register that contains information about the state of the Central processing unit, processor. Individual bits are implicitly or explicitly read and/or written by the machine code instructions executing on the processor. The status register lets an instruction take action contingent on the outcome of a previous instruction. Typically, flags in the status register are modified as effects of arithmetic and bit manipulation operations. For example, a Z bit may be set if the result of the operation is ze ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Program Counter

The program counter (PC), commonly called the instruction pointer (IP) in Intel x86 and Itanium microprocessors, and sometimes called the instruction address register (IAR), the instruction counter, or just part of the instruction sequencer, is a processor register that indicates where a computer is in its program sequence. Usually, the PC is incremented after fetching an instruction, and holds the memory address of (" points to") the next instruction that would be executed. Processors usually fetch instructions sequentially from memory, but ''control transfer'' instructions change the sequence by placing a new value in the PC. These include branches (sometimes called jumps), subroutine calls, and returns. A transfer that is conditional on the truth of some assertion lets the computer follow a different sequence under different conditions. A branch provides that the next instruction is fetched from elsewhere in memory. A subroutine call not only branches but saves the preced ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

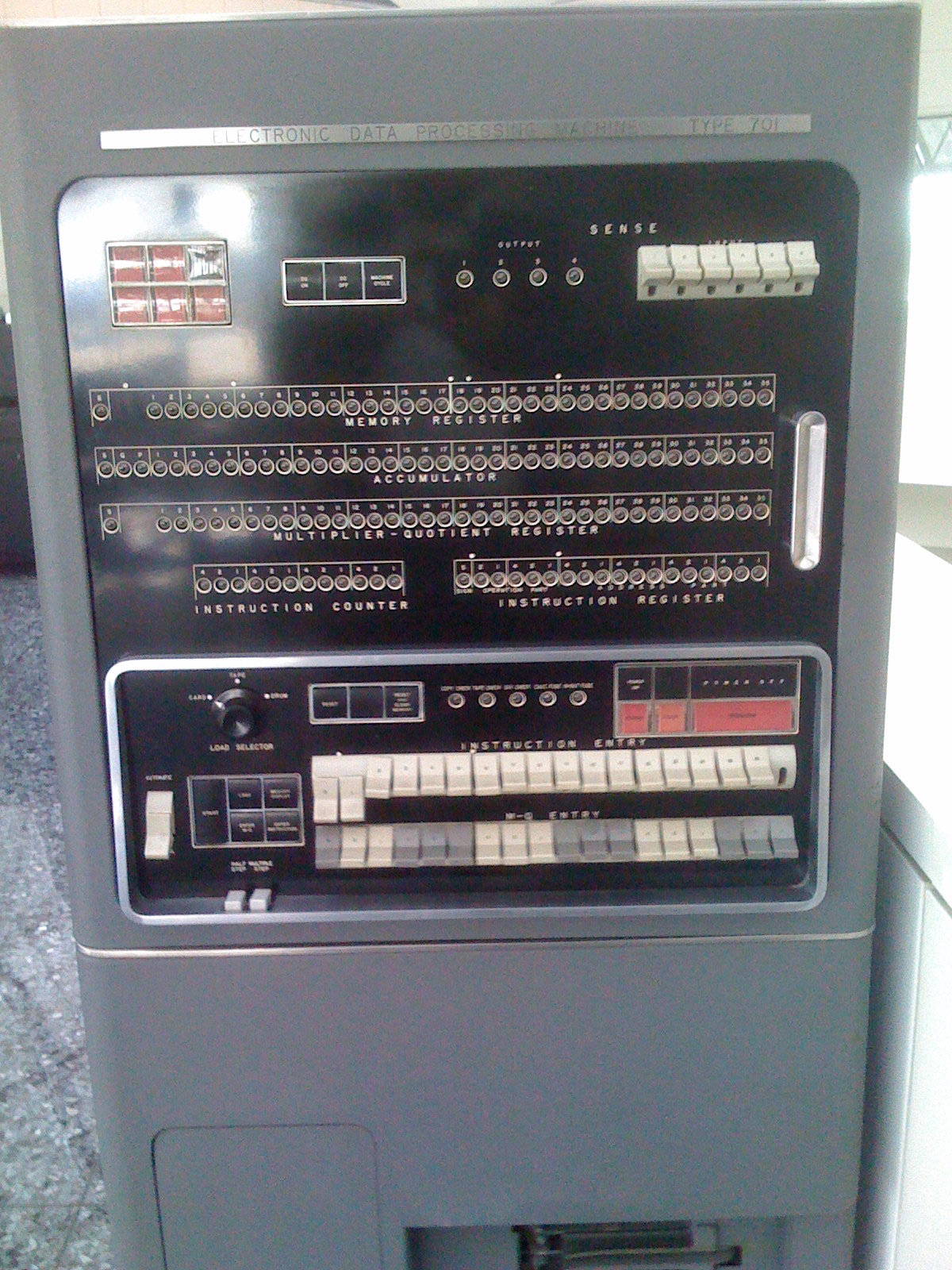

IBM System/360

The IBM System/360 (S/360) is a family of mainframe computer systems that was announced by IBM on April 7, 1964, and delivered between 1965 and 1978. It was the first family of computers designed to cover both commercial and scientific applications and to cover a complete range of applications from small to large. The design distinguished between architecture and implementation, allowing IBM to release a suite of compatible designs at different prices. All but the only partially compatible Model 44 and the most expensive systems use microcode to implement the instruction set, which features 8-bit byte addressing and binary, decimal, and hexadecimal floating-point calculations. The System/360 family introduced IBM's Solid Logic Technology (SLT), which packed more transistors onto a circuit card, allowing more powerful but smaller computers to be built. The slowest System/360 model announced in 1964, the Model 30, could perform up to 34,500 instructions per second, with memo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Condition Code Register

A status register, flag register, or condition code register (CCR) is a collection of status flag bits for a processor. Examples of such registers include FLAGS register in the x86 architecture, flags in the program status word (PSW) register in the IBM System/360 architecture through z/Architecture, and the application program status register (APSR) in the ARM Cortex-A architecture. The status register is a hardware register that contains information about the state of the processor. Individual bits are implicitly or explicitly read and/or written by the machine code instructions executing on the processor. The status register lets an instruction take action contingent on the outcome of a previous instruction. Typically, flags in the status register are modified as effects of arithmetic and bit manipulation operations. For example, a Z bit may be set if the result of the operation is zero and cleared if it is nonzero. Other classes of instructions may also modify the flags to indi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Branch (computer Science)

A branch is an instruction in a computer program that can cause a computer to begin executing a different instruction sequence and thus deviate from its default behavior of executing instructions in order. ''Branch'' (or ''branching'', ''branched'') may also refer to the act of switching execution to a different instruction sequence as a result of executing a branch instruction. Branch instructions are used to implement control flow in program loops and conditionals (i.e., executing a particular sequence of instructions only if certain conditions are satisfied). A branch instruction can be either an ''unconditional branch'', which always results in branching, or a ''conditional branch'', which may or may not cause branching depending on some condition. Also, depending on how it specifies the address of the new instruction sequence (the "target" address), a branch instruction is generally classified as ''direct'', ''indirect'' or ''relative'', meaning that the instruction contai ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Interrupt Mask

In digital computers, an interrupt (sometimes referred to as a trap) is a request for the processor to ''interrupt'' currently executing code (when permitted), so that the event can be processed in a timely manner. If the request is accepted, the processor will suspend its current activities, save its state, and execute a function called an ''interrupt handler'' (or an ''interrupt service routine'', ISR) to deal with the event. This interruption is often temporary, allowing the software to resume normal activities after the interrupt handler finishes, although the interrupt could instead indicate a fatal error. Interrupts are commonly used by hardware devices to indicate electronic or physical state changes that require time-sensitive attention. Interrupts are also commonly used to implement computer multitasking, especially in real-time computing. Systems that use interrupts in these ways are said to be interrupt-driven. Types Interrupt signals may be issued in response to ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM System/360 Model 67

The IBM System/360 Model 67 (S/360-67) was an important IBM mainframe model in the late 1960s. * It had "its own powerful operating system... heTime Sharing System monitor (TSS)" offering "virtually instantaneous access to and response from the computer" to "take advantage of the unique capabilities of a multiprocessor system" * It offered "dynamic relocation of problem programs using the dynamic address translation facilities of the 2067 Processing Unit, permitting response, within seconds, to many simultaneous users" Virtual memory The S/360-67 design added a component for implementing virtual memory, the "DAT box" (Dynamic Address Translation box). DAT on the 360/67 was based on the architecture outlined in a 1966 '' JACM'' paper by Arden, Galler, Westervelt, and O'Brien and included both segment and page tables. The Model 67's virtual memory support was very similar to the virtual memory support that eventually became standard on the entire System/370 line. The S/360-67 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

32-bit

In computer architecture, 32-bit computing refers to computer systems with a processor, memory, and other major system components that operate on data in 32-bit units. Compared to smaller bit widths, 32-bit computers can perform large calculations more efficiently and process more data per clock cycle. Typical 32-bit personal computers also have a 32-bit address bus, permitting up to 4 GB of RAM to be accessed; far more than previous generations of system architecture allowed. 32-bit designs have been used since the earliest days of electronic computing, in experimental systems and then in large mainframe and minicomputer systems. The first hybrid 16/32-bit microprocessor, the Motorola 68000, was introduced in the late 1970s and used in systems such as the original Apple Macintosh. Fully 32-bit microprocessors such as the Motorola 68020 and Intel 80386 were launched in the early to mid 1980s and became dominant by the early 1990s. This generation of personal computers coincided ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Z/Architecture

z/Architecture, initially and briefly called ESA Modal Extensions (ESAME), is IBM's 64-bit complex instruction set computer (CISC) instruction set architecture, implemented by its mainframe computers. IBM introduced its first z/Architecture-based system, the z900, in late 2000. Later z/Architecture systems include the IBM z800, z990, z890, System z9, System z10, zEnterprise 196, zEnterprise 114, zEC12, zBC12, z13, z14, z15 and z16. z/Architecture retains backward compatibility with previous 32-bit-data/31-bit-addressing architecture ESA/390 and its predecessors all the way back to the 32-bit-data/24-bit-addressing System/360. The IBM z13 is the last z Systems server to support running an operating system in ESA/390 architecture mode. However, all 24-bit and 31-bit problem-state application programs originally written to run on the ESA/390 architecture will be unaffected by this change. Each z/OS address space, called a 64-bit address space, is 16 exabytes in size. C ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Load Program Status Word Instruction

The IBM System/360 architecture is the model independent architecture for the entire S/360 line of mainframe computers, including but not limited to the instruction set architecture. The elements of the architecture are documented in the ''IBM System/360 Principles of Operation'' and the ''IBM System/360 I/O Interface Channel to Control Unit Original Equipment Manufacturers' Information'' manuals. Features The System/360 architecture provides the following features: * 16 32-bit general-purpose registers * 4 64-bit floating-point registers * 64-bit processor status register (PSW), which includes a 24-bit instruction address * 24-bit (16 MB) byte-addressable memory space * Big-endian byte/word order * A ''standard instruction set'', including fixed-point binary arithmetic and logical instructions, present on all System/360 models (except the Model 20, see below). ** A ''commercial instruction set'', adding decimal arithmetic instructions, is optional on some models, as ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

360/20

The IBM System/360 Model 20 is the smallest member of the IBM System/360 family announced in November 1964. The Model 20 supports only a subset of the System/360 instruction set, with binary numbers limited to 16 bits and no floating point. In later years it would have been classified as a 16-bit minicomputer rather than a mainframe, but the term "minicomputer" was not current, and in any case IBM wanted to emphasize the compatibility of the Model 20 rather than its differences from the rest of the System/360 line. It does, however, have the full System/360 decimal instruction set, that allows for addition, subtraction, product, and dividend of up to 31 decimal digits. Developed by IBM in Böblingen, Germany, the system was intended for data processing and as a replacement for tab equipment. An incompatible small computer, the IBM 1130 introduced the following year, was designed for scientific and engineering computing. The design of the Model 20 was the result of a tug of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

360/67

The IBM System/360 Model 67 (S/360-67) was an important IBM mainframe model in the late 1960s. * It had "its own powerful operating system... heTime Sharing System monitor (TSS)" offering "virtually instantaneous access to and response from the computer" to "take advantage of the unique capabilities of a multiprocessor system" * It offered "dynamic relocation of problem programs using the dynamic address translation facilities of the 2067 Processing Unit, permitting response, within seconds, to many simultaneous users" Virtual memory The S/360-67 design added a component for implementing virtual memory, the "DAT box" (Dynamic Address Translation box). DAT on the 360/67 was based on the architecture outlined in a 1966 ''JACM'' paper by Arden, Galler, Westervelt, and O'Brien and included both segment and page tables. The Model 67's virtual memory support was very similar to the virtual memory support that eventually became standard on the entire System/370 line. The S/360-67 p ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |