|

MP6

The Rise mP6 was a superpipelined and superscalar microprocessor designed by Rise Technology to compete with the Intel Pentium line. History Rise Technology had spent 5 years developing a x86 compatible microprocessor, and finally introduced it in November 1998 as a low-cost, low-power alternative for the Super Socket 7 platform, that allowed for higher Front-side bus speeds than the previous Socket 7 and that made it possible for other CPU manufacturers to keep competing against Intel, that had moved to the Slot 1 platform. Design The mP6 made use of the MMX instruction set and had three MMX pipelines which allowed the CPU to execute up to three MMX instructions in a single cycle. Its three integer units made it possible to execute three integer instructions in a single cycle as well and the fully pipelined floating point unit could execute up to two floating-point instructions per cycle. To further improve the performance the core utilized branch prediction and a number of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Silicon Integrated Systems

Silicon Integrated Systems (SiS; ) is a company that manufactures, among other things, motherboard chipsets. The company was founded in 1987 in Hsinchu Science Park, Taiwan. Business In the late 1990s, SiS made the decision to invest in their own chip fabrication facilities. At the end of 1999, SiS acquired Rise Technology and its mP6 x86 core technology. Mainboard chipsets One of the most famous chipsets produced by SiS was the late 486-age chipset 496/497 which supported PCI bus among older ISA- and VLB-buses. Mainboards using this chipset and equipped with CPUs such as the Intel 80486DX4, AMD 5x86 or Cyrix Cx5x86 processors had performance and compatibility comparable with early Intel Pentium systems in addition to a lower price. After this late success, SiS continued positioning itself as a budget chipset producer. The company emphasized high integration to minimize the cost to implement their solutions. As such, SiS one-chip mainboard chipsets that included integrated ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Rise Technology

Rise Technology was a short lived microprocessor manufacturer that produced the Intel x86 MMX compatible mP6 processor. The mP6 was a microprocessor that was designed to perform a smaller number of types of computer instructions so that it can operate at a higher speed (perform more millions of instructions per second, or MIPS). The Santa Clara, California based company was started by David Lin in 1993 with funding from 15 Taiwanese investors, including UMC, ACER and VIA Technologies. After multiple company restructurings, the mP6 was announced at the end of 1998 and went into small production in 1999. The device was meant for the low-end, low-power segment of laptop computers. Finding itself unable to compete in the computing market with the larger vendors (Intel and AMD), Rise re-targeted itself to set-top box A set-top box (STB), also colloquially known as a cable box and historically television decoder, is an information appliance device that generally contains a T ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

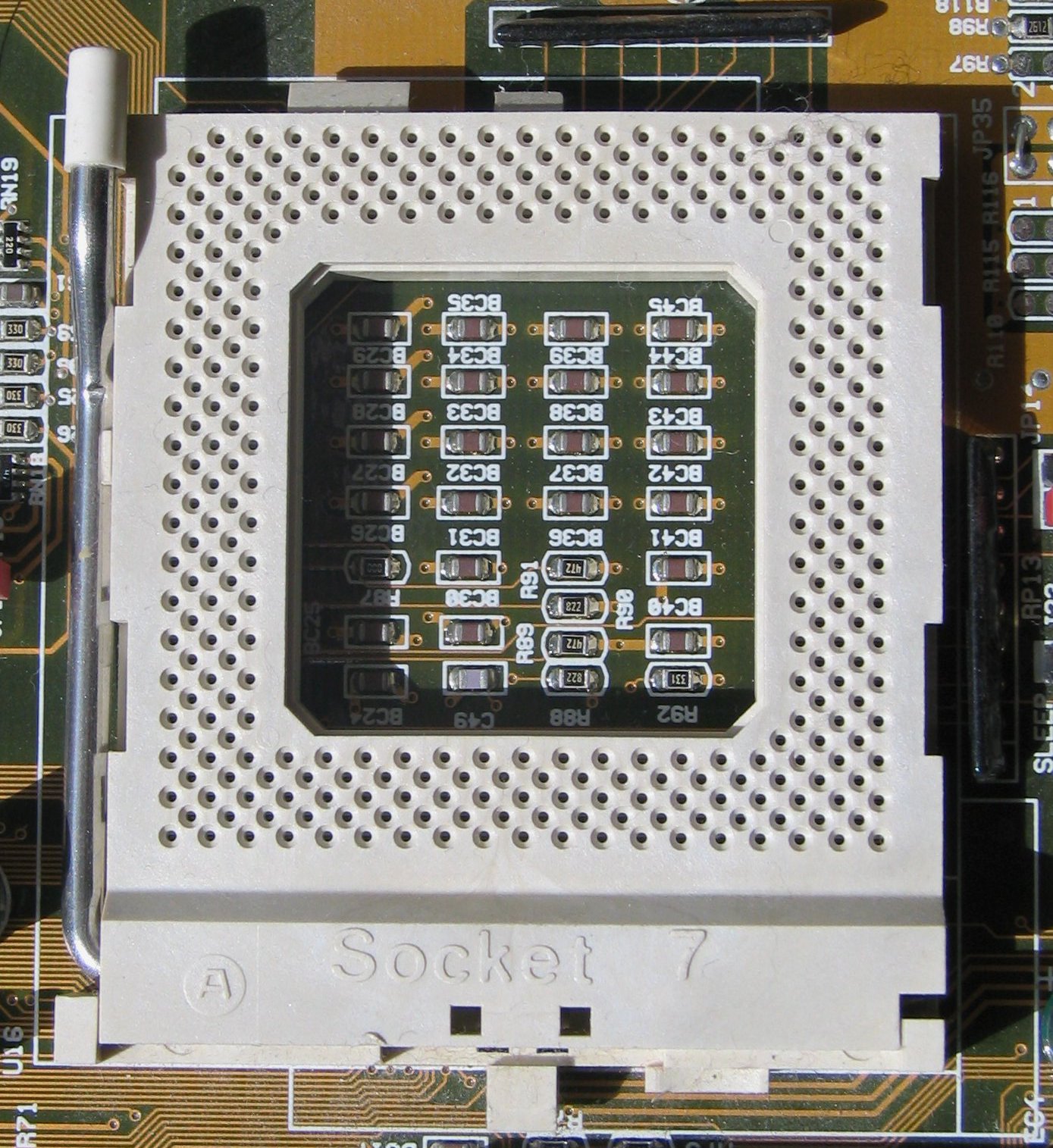

Super Socket 7

Super Socket 7, also referred to as Super 7, is a hardware-level extension of the Socket 7 ZIF socket specification for x86 processors. Compatible motherboards and chipsets use a standard Socket 7 connection for the CPU, while adding certain features including a maximum 100 MHz front-side bus and support for AGP graphics cards. Super Socket 7 was used by AMD K6-2 and K6-III processors, some of the final Cyrix M-II processors, some of the final IDT WinChip 2 processors, and Rise mP6 processors. It is backward compatible with Socket 7 CPUs, meaning a Socket 7 CPU can be used with a Super Socket 7 motherboard, but a Super Socket 7 CPU cannot operate at full speed in a Socket 7 motherboard. Socket 5 CPUs are pin-compatible with Super Socket 7, but not all motherboards designed for Super Socket 7 supported the voltages or bus speeds needed for Socket 5 CPUs. While AMD had previously always used Intel sockets for their processors, Socket 7 was the last one for which AMD ret ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel P5

The Pentium (also referred to as P5, its microarchitecture, or i586) is a fifth generation, 32-bit x86 microprocessor that was introduced by Intel on March 22, 1993, as the very first CPU in the Pentium brand. It was instruction set compatible with the 80486 but was a new and very different microarchitecture design from previous iterations. The P5 Pentium was the first superscalar x86 microarchitecture and the world's first superscalar microprocessor to be in mass productionmeaning it generally executes at least 2 instructions per clock mainly because of a design-first dual integer pipeline design previously thought impossible to implement on a CISC microarchitecture. Additional features include a faster floating-point unit, wider data bus, separate code and data caches, and many other techniques and features to enhance performance and support security, encryption, and multiprocessing, for workstations and servers when compared to the next best previous industry standard proces ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Socket 7

Socket 7 is a physical and electrical specification for an x86-style CPU socket on a personal computer motherboard. It was released in June 1995. The socket supersedes the earlier Socket 5, and accepts P5 Pentium microprocessors manufactured by Intel, as well as compatibles made by Cyrix/ IBM, AMD, IDT and others. Socket 7 was the only socket that supported a wide range of CPUs from different manufacturers and a wide range of speeds. Differences between Socket 5 and Socket 7 are that Socket 7 has an extra pin and is designed to provide dual split rail voltage, as opposed to Socket 5's single voltage. However, not all motherboard manufacturers supported the dual voltage on their boards initially. Socket 7 is backwards compatible; a Socket 5 CPU can be inserted and used on a Socket 7 motherboard. Processors that used Socket 7 are the AMD K5 and K6, the Cyrix 6x86 and 6x86MX, the IDT WinChip, the Intel P5 Pentium (2.5–3.5 V, 75–200 MHz), the Pentium MMX (166–233 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ball Grid Array

A ball grid array (BGA) is a type of surface-mount packaging (a chip carrier) used for integrated circuits. BGA packages are used to permanently mount devices such as microprocessors. A BGA can provide more interconnection pins than can be put on a dual in-line or flat package. The whole bottom surface of the device can be used, instead of just the perimeter. The traces connecting the package's leads to the wires or balls which connect the die to package are also on average shorter than with a perimeter-only type, leading to better performance at high speeds. BGAs were introduced in the 1990s and became popular by 2001. Soldering of BGA devices requires precise control and is usually done by automated processes such as in computer-controlled automatic reflow ovens. Description The BGA is descended from the pin grid array (PGA), which is a package with one face covered (or partly covered) with pins in a grid pattern which, in operation, conduct electrical signals between ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CPU Caches

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (MMU) ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Branch Predictor

In computer architecture, a branch predictor is a digital circuit that tries to guess which way a branch (e.g., an if–then–else structure) will go before this is known definitively. The purpose of the branch predictor is to improve the flow in the instruction pipeline. Branch predictors play a critical role in achieving high performance in many modern pipelined microprocessor architectures such as x86. Two-way branching is usually implemented with a conditional jump instruction. A conditional jump can either be "taken" and jump to a different place in program memory, or it can be "not taken" and continue execution immediately after the conditional jump. It is not known for certain whether a conditional jump will be taken or not taken until the condition has been calculated and the conditional jump has passed the execution stage in the instruction pipeline (see fig. 1). Without branch prediction, the processor would have to wait until the conditional jump instruction ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Data Dependency

A data dependency in computer science is a situation in which a program statement (instruction) refers to the data of a preceding statement. In compiler theory, the technique used to discover data dependencies among statements (or instructions) is called dependence analysis. There are three types of dependencies: data, name, and control. Data dependencies Assuming statement S_1 and S_2, S_2 depends on S_1 if: :\left (S_1) \cap O(S_2)\right\cup \left (S_1) \cap I(S_2)\right\cup \left (S_1) \cap O(S_2)\right\neq \varnothing where: * I(S_i) is the set of memory locations read by * O(S_j) is the set of memory locations written by and * there is a feasible run-time execution path from S_1 to This Condition is called Bernstein Condition, named by A. J. Bernstein. Three cases exist: * Anti-dependence: I(S_1) \cap O(S_2) \neq \varnothing, S_1 \rightarrow S_2 and S_1 reads something before S_2 overwrites it * Flow (data) dependence: O(S_1) \cap I(S_2) \neq \varnothing, S_1 \right ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel Pentium II

The Pentium II brand refers to Intel's sixth-generation microarchitecture (" P6") and x86-compatible microprocessors introduced on May 7, 1997. Containing 7.5 million transistors (27.4 million in the case of the mobile Dixon with 256 KB L2 cache), the Pentium II featured an improved version of the first ''P6''-generation core of the Pentium Pro, which contained 5.5 million transistors. However, its L2 cache subsystem was a downgrade when compared to the Pentium Pros. It is a single-core microprocessor. In 1998, Intel stratified the Pentium II family by releasing the Pentium II-based Celeron line of processors for low-end workstations and the Pentium II Xeon line for servers and high-end workstations. The Celeron was characterized by a reduced or omitted (in some cases present but disabled) on-die full-speed L2 cache and a 66 MT/s FSB. The Xeon was characterized by a range of full-speed L2 cache (from 512 KB to 2048 KB), a 100 MT/s FSB, a different physical ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD K6-2

The K6-2 is an x86 microprocessor introduced by AMD on May 28, 1998, and available in speeds ranging from 266 to 550 MHz. An enhancement of the original K6, the K6-2 introduced AMD's 3DNow! SIMD instruction set, featured a larger 64 KiB Level 1 cache (32 KiB instruction and 32 KiB data), and an upgraded system-bus interface called Super Socket 7, which was backward compatible with older Socket 7 motherboards. It was manufactured using a 0.25 micrometre process, ran at 2.2 volts, and had 9.3 million transistors. History The K6-2 was designed as a competitor to Intel's flagship processor, the significantly more expensive Pentium II. Performance of the two chips was similar: the previous K6 tended to be faster for general-purpose computing, while the Intel part was faster in x87 floating-point applications. To battle the Pentium 2's dominance on floating point calculations the K6-2 was the first CPU to introduce a floating point SIMD instruction set (dubbed ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Celeron

Celeron is Intel's brand name for low-end IA-32 and x86-64 computer microprocessor models targeted at low-cost personal computers. Celeron processors are compatible with IA-32 software. They typically offer less performance per clock speed compared to flagship Intel CPU lines, such as the Pentium or Core brands. Celeron branded processors often have less cache or intentionally disabled advanced features, with variable impact on performance. While some Celeron designs have achieved strong performance for their segment, most of the Celeron line has exhibited noticeably degraded performance. This has been the primary justification for the higher cost of other Intel CPU brands versus the Celeron range. Introduced in April 1998, the first Celeron-branded CPU was based on the Pentium II. Subsequent Celeron-branded CPUs were based on the Pentium III, Pentium 4, Pentium M, and Intel Core. In September 2022, Intel announced that the Celeron brand, along with Pentium, will be replac ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

.jpg)

_(JPG).jpg)