|

AMD K6-2

The K6-2 is an x86 microprocessor introduced by AMD on May 28, 1998, and available in speeds ranging from 266 to 550 MHz. An enhancement of the original K6, the K6-2 introduced AMD's 3DNow! SIMD instruction set and an upgraded system-bus interface called Super Socket 7, which was backward compatible with older Socket 7 motherboards. It was manufactured using a 250 nanometer process, ran at 2.2 volts, and had 9.3 million transistors. History The K6-2 was designed as a competitor to Intel's flagship processor, the significantly more expensive Pentium II. Performance of the two chips was similar: the previous K6 tended to be faster for general-purpose computing, while the Intel part was faster in x87 floating-point applications. To battle the Pentium II's dominance on floating point calculations the K6-2 was the first CPU to introduce a floating point SIMD instruction set (dubbed 3DNow! by AMD), which significantly boosted performance. However programs needed to be specifically ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

AMD K6

The K6 microprocessor was launched by AMD in 1997. The main advantage of this particular microprocessor is that it was designed to fit into existing desktop designs for Pentium-branded CPUs. It was marketed as a product that could perform as well as its Intel Pentium II equivalent but at a significantly lower price. The K6 had a considerable impact on the PC market and presented Intel with serious competition. Background The AMD K6 is a superscalar P5 Pentium-class microprocessor, manufactured by AMD, which superseded the K5. The AMD K6 is based on the Nx686 microprocessor that NexGen was designing when it was acquired by AMD. Despite the name implying a design evolving from the K5, it is in fact a totally different design that was created by the NexGen team, including chief processor architect Greg Favor, and adapted after the AMD purchase. The K6 processor included a feedback dynamic instruction reordering mechanism, MMX instructions, and a floating-point unit (FPU). It ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

SIMD

Single instruction, multiple data (SIMD) is a type of parallel computer, parallel processing in Flynn's taxonomy. SIMD describes computers with multiple processing elements that perform the same operation on multiple data points simultaneously. SIMD can be internal (part of the hardware design) and it can be directly accessible through an instruction set architecture (ISA), but it should not be confused with an ISA. Such machines exploit Data parallelism, data level parallelism, but not Concurrent computing, concurrency: there are simultaneous (parallel) computations, but each unit performs exactly the same instruction at any given moment (just with different data). A simple example is to add many pairs of numbers together, all of the SIMD units are performing an addition, but each one has different pairs of values to add. SIMD is particularly applicable to common tasks such as adjusting the contrast in a digital image or adjusting the volume of digital audio. Most modern Cen ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Front-side Bus

The front-side bus (FSB) is a computer communication interface ( bus) that was often used in Intel-chip-based computers during the 1990s and 2000s. The EV6 bus served the same function for competing AMD CPUs. Both typically carry data between the central processing unit (CPU) and a memory controller hub, known as the northbridge. Depending on the implementation, some computers may also have a back-side bus that connects the CPU to the cache. This bus and the cache connected to it are faster than accessing the system memory (or RAM) via the front-side bus. The speed of the front side bus is often used as an important measure of the performance of a computer. The original front-side bus architecture was replaced by HyperTransport, Intel QuickPath Interconnect, and Direct Media Interface, followed by Intel Ultra Path Interconnect and AMD's Infinity Fabric. History The term came into use by Intel Corporation about the time the Pentium Pro and Pentium II products were announ ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

CPUID

In the x86 architecture, the CPUID instruction (identified by a CPUID opcode) is a processor supplementary instruction (its name derived from " CPU Identification") allowing software to discover details of the processor. It was introduced by Intel in 1993 with the launch of the Pentium and SL-enhanced 486 processors. A program can use the CPUID to determine processor type and whether features such as MMX/ SSE are implemented. History Prior to the general availability of the CPUID instruction, programmers would write esoteric machine code which exploited minor differences in CPU behavior in order to determine the processor make and model. With the introduction of the 80386 processor, EDX on reset indicated the revision but this was only readable after reset and there was no standard way for applications to read the value. Outside the x86 family, developers are mostly still required to use esoteric processes (involving instruction timing or CPU fault triggers) to determine th ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

KL AMD K6-2 Chomper-XT

KL, kL, kl, or kl. may refer to: Businesses and organizations * KLM, a Dutch airline (IATA airline designator KL) * Koninklijke Landmacht, the Royal Netherlands Army * Kvenna Listin ("Women's List"), a political party in Iceland * KL FM, a Malay language radio station Places * Kaiserslautern, Germany (license plate code KL) * Kerala, India (ISO 3166-2:IN sub-code KL) * Kirkland Lake, Ontario, Canada * Kowloon, Hong Kong * Kuala Lumpur, Malaysia Science, technology, and mathematics * KL engine, version of the Mazda K engine * Klepton (kl.), a type of species in zoology * Kiloliter (kL), a unit of volume * Kullback–Leibler divergence in mathematics * KL (gene), a gene which encodes the klotho enzyme in humans Other uses * Jeep Cherokee (KL) * Kalaallisut language (ISO 639 alpha-2 language code "kl") * Kl (digraph), used in the Zulu language to write /kʟ̥ʼ/ or /kxʼ/ * Konzentrationslager, or concentration camp, abbreviated KZ or KL * '' KL: A History of the Nazi Concentratio ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Tom's Hardware

''Tom's Hardware'' is an online publication owned by Future plc and focused on technology. It was founded in 1996 by Thomas Pabst. It provides articles, news, price comparisons, videos and reviews on computer hardware and high technology. The site features coverage on CPUs, motherboards, RAM, PC cases, graphic cards, display technology, power supplies and displays, storage, smartphones, tablets, gaming, consoles, and computer peripherals. ''Tom's Hardware'' has a forum and featured blogs. History ''Tom's Hardware'' was founded in 1996 as ''Tom's Hardware Guide'' in Canada by Thomas Pabst. It started using the domain tomshardware.com in September 1997 and was followed by several foreign language versions, including Italian, French, Finnish and Russian based on franchise agreements. While the initial testing labs were in Germany and California, much of ''Tom's Hardware'''s testing now occurs in New York and a facility in Ogden, Utah owned by its parent company. In April 20 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Unofficial Patch

An unofficial patch, sometimes alternatively called a community patch, is a patch for a piece of software, created by a third party such as a user community without the involvement of the original developer. Similar to an ordinary patch, it alleviates bugs or shortcomings. Unofficial patches do not usually change the intended usage of the software, in contrast to other third-party software adaptions such as mods or cracks. Motivation A common motivation for the creation of unofficial patches is missing technical support by the original software developer or provider. Reasons may include: *the software product reached its defined end-of-life and/or was superseded by a successor product ( planned obsolescence) * the software was originally designed to operate in a substantially different environment and may require improvement/optimization ( porting) * the developer has gone out of business and is not available anymore *support is not economically viable (e.g. localization f ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

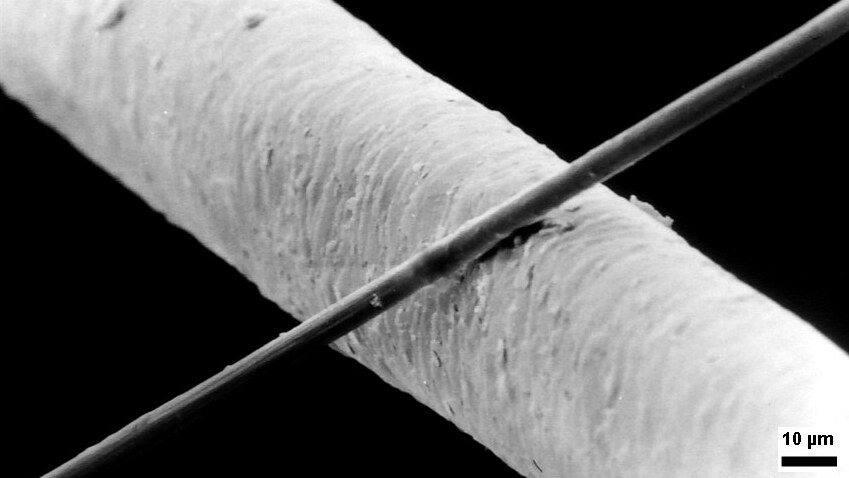

Micrometre

The micrometre (English in the Commonwealth of Nations, Commonwealth English as used by the International Bureau of Weights and Measures; SI symbol: μm) or micrometer (American English), also commonly known by the non-SI term micron, is a unit of length in the International System of Units (SI) equalling (SI standard prefix "micro-" = ); that is, one millionth of a metre (or one thousandth of a millimetre, , or about ). The nearest smaller common SI Unit, SI unit is the nanometre, equivalent to one thousandth of a micrometre, one millionth of a millimetre or one billionth of a metre (). The micrometre is a common unit of measurement for wavelengths of infrared radiation as well as sizes of biological cell (biology), cells and bacteria, and for grading wool by the diameter of the fibres. The width of a single human hair ranges from approximately 20 to . Examples Between 1 μm and 10 μm: * 1–10 μm – length of a typical bacterium * 3–8 μm – width of str ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

L2 Cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (MMU) whic ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |