|

Flow To HDL

Flow to HDL tools and methods convert flow-based system design into a hardware description language (HDL) such as VHDL or Verilog. Typically this is a method of creating designs for field-programmable gate array, application-specific integrated circuit prototyping and digital signal processing (DSP) design. Flow-based system design is well-suited to field-programmable gate array design as it is easier to specify the innate parallelism of the architecture. History The use of flow-based design tools in engineering is a reasonably new trend. Unified Modeling Language is the most widely used example for software design. The use of flow-based design tools allows for more holistic system design and faster development. C to HDL tools and flow have a similar aim, but with C or C-like programming languages. Applications Most applications are ones which take too long with existing supercomputer architectures. These include bioinformatics, CFD, financial processing and oil and gas s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Hardware Description Language

In computer engineering, a hardware description language (HDL) is a specialized computer language used to describe the structure and behavior of electronic circuits, usually to design application-specific integrated circuits (ASICs) and to program field-programmable gate arrays (FPGAs). A hardware description language enables a precise, Formal language, formal description of an electronic circuit that allows for the automated analysis and Electronic circuit simulation, simulation of the circuit. It also allows for the Logic synthesis, synthesis of an HDL description into a netlist (a specification of physical electronic components and how they are connected together), which can then be Place and route, placed and routed to produce the Mask set, set of masks used to create an integrated circuit. A hardware description language looks much like a programming language such as C (programming language), C or ALGOL; it is a textual description consisting of expressions, statements and c ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Electronic Design Automation

Electronic design automation (EDA), also referred to as electronic computer-aided design (ECAD), is a category of software tools for designing Electronics, electronic systems such as integrated circuits and printed circuit boards. The tools work together in a Design flow (EDA), design flow that chip designers use to design and analyze entire semiconductor chips. Since a modern semiconductor chip can have billions of components, EDA tools are essential for their design; this article in particular describes EDA specifically with respect to integrated circuits (ICs). History Early days The earliest electronic design automation is attributed to IBM with the documentation of its IBM 700/7000 series, 700 series computers in the 1950s. Prior to the development of EDA, integrated circuits were designed by hand and manually laid out. Some advanced shops used geometric software to generate tapes for a Gerber format, Gerber photoplotter, responsible for generating a monochromatic ex ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

SystemC

SystemC is a set of C++ classes and macros which provide an event-driven simulation interface (see also discrete event simulation). These facilities enable a designer to ''simulate'' concurrent processes, each described using plain C++ syntax. SystemC processes can communicate in a ''simulated'' real-time environment, using signals of all the datatypes offered by C++, some additional ones offered by the SystemC library, as well as user defined. In certain respects, SystemC deliberately mimics the hardware description languages VHDL and Verilog, but is more aptly described as a ''system-level modeling language''. SystemC is applied to system-level modeling, architectural exploration, performance modeling, software development, functional verification, and high-level synthesis. SystemC is often associated with electronic system-level (ESL) design, and with transaction-level modeling (TLM). Language specification SystemC is defined and promoted by the Open SystemC Initiativ ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

SpecC

SpecC is a System Description Language (SDL), or System-level Design Language (SLDL), and is an extension of the ANSI C programming language. It is used to aid the design and specification of digital embedded systems, providing improved productivity whilst retaining the ability to change a design at functional and specification level, unlike HDLs like Verilog and VHDL. An architectural model can be created which allows other tools to directly map the design onto silicon or FPGA. The main aim is for the reuse, exchange and integration of IP at various levels of abstraction. The language and design methodology were created by Rainer Dömer and Daniel Gajski at the Centre for Embedded Computer Systems at University of California, Irvine in 2001. Similar projects and design methodologies include SystemC, an SDL based on C++. Although this rival language has seen much more widespread industry usage (although SpecC is popular in Japan), SpecC retains simplicity whilst also providing ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Ruby (hardware Description Language)

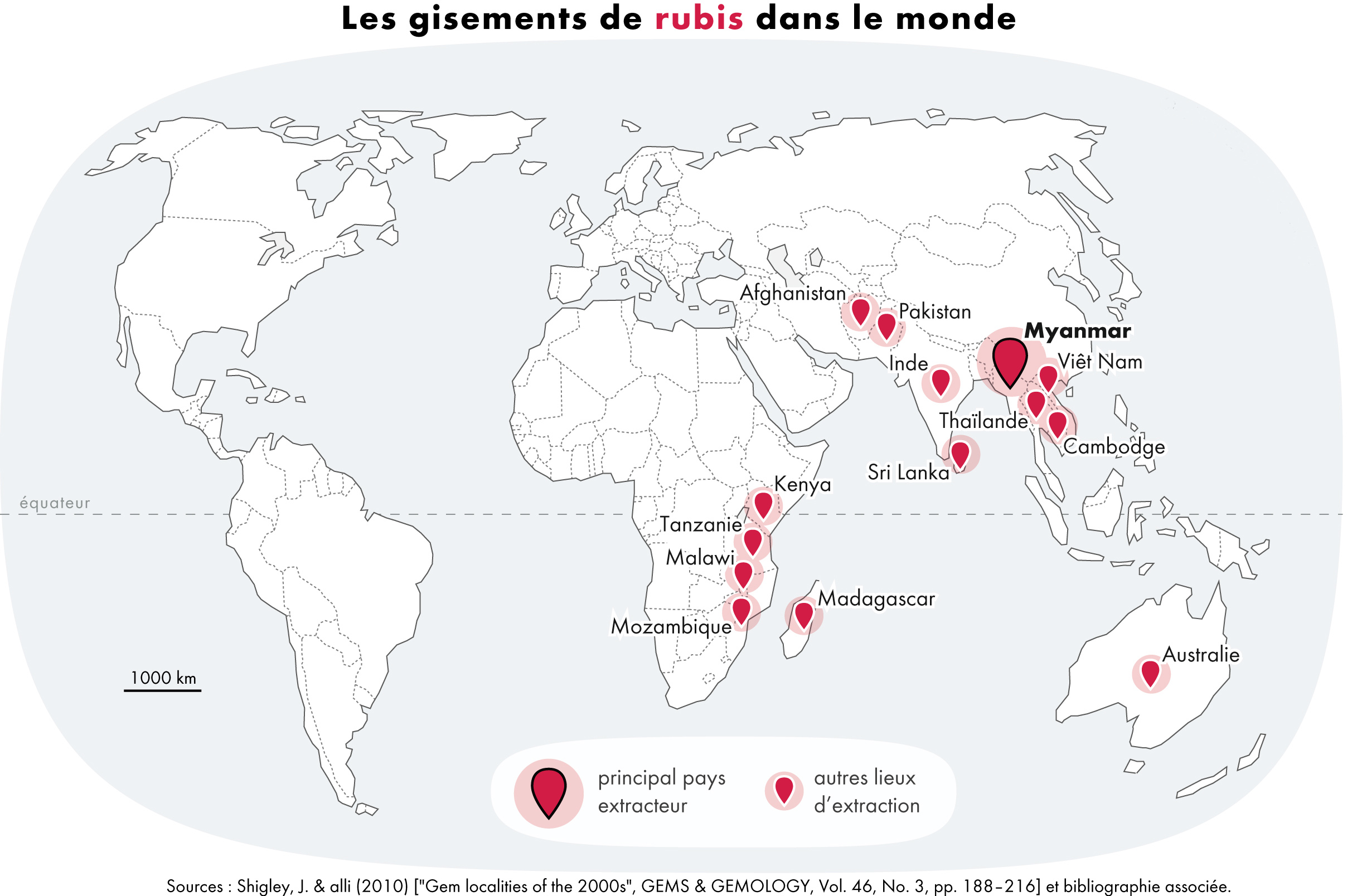

Ruby is a pinkish-red-to-blood-red-colored gemstone, a variety of the mineral corundum (aluminium oxide). Ruby is one of the most popular traditional jewelry gems and is very durable. Other varieties of gem-quality corundum are called sapphires; given that the rest of the corundum species are called as such, rubies are sometimes referred to as "red sapphires". Ruby is one of the traditional cardinal gems, alongside amethyst, sapphire, emerald, and diamond. The word ''ruby'' comes from ''ruber'', Latin for red. The color of a ruby is due to the presence of chromium. Some gemstones that are popularly or historically called rubies, such as the Black Prince's Ruby in the British Imperial State Crown, are actually spinels. These were once known as "Balas rubies". The quality of a ruby is determined by its color, cut, and clarity, which, along with carat weight, affect its value. The brightest and most valuable shade of red, called blood-red or pigeon blood, commands a large prem ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Register Transfer Level

In digital circuit design, register-transfer level (RTL) is a design abstraction which models a synchronous digital circuit in terms of the flow of digital signals (data) between hardware registers, and the logical operations performed on those signals. Register-transfer-level abstraction is used in hardware description languages (HDLs) like Verilog and VHDL to create high-level representations of a circuit, from which lower-level representations and ultimately actual wiring can be derived. Design at the RTL level is typical practice in modern digital design. Unlike in software compiler design, where the register-transfer level is an intermediate representation and at the lowest level, the RTL level is the usual input that circuit designers operate on. In circuit synthesis, an intermediate language between the input register transfer level representation and the target netlist is sometimes used. Unlike in netlist, constructs such as cells, functions, and multi-bit registers ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Register Transfer Notation

Register Transfer Notation (or RTN) is a way of specifying the behavior of a digital synchronous circuit In digital electronics, a synchronous circuit is a digital circuit in which the changes in the state (computer science), state of memory elements are synchronized by a clock signal. In a sequential logic, sequential digital logic circuit, data .... It is said to be a specification language for this reason. Register Transfer Languages (or RTL, where the L sometimes stands for Level of abstraction) are similar to Register Transfer Notation and used to describe much the same thing, however they are of a synthesizable format and more similar to a standard computer programming language, like C. RTN may be written as either abstract or concrete. Abstract RTN is a generic notation which does not have any specific machine implementation details. In contrast, concrete RTN is a notation which does implement specifics of the machine for which it is designed. The possible locations in ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Open Source Software

Open-source software (OSS) is Software, computer software that is released under a Open-source license, license in which the copyright holder grants users the rights to use, study, change, and Software distribution, distribute the software and its source code to anyone and for any purpose. Open-source software may be developed in a collaborative, public manner. Open-source software is a prominent example of open collaboration, meaning any capable user is able to online collaboration, participate online in development, making the number of possible contributors indefinite. The ability to examine the code facilitates public trust in the software. Open-source software development can bring in diverse perspectives beyond those of a single company. A 2024 estimate of the value of open-source software to firms is $8.8 trillion, as firms would need to spend 3.5 times the amount they currently do without the use of open source software. Open-source code can be used for studying and a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

MyHDL

MyHDL is a Python-based hardware description language (HDL). Features of MyHDL include: * The ability to generate VHDL and Verilog code from a MyHDL design. * The ability to generate a testbench (Conversion of test benches) with test vectors in VHDL or Verilog, based on complex computations in Python. * The ability to convert a list of signals. * The ability to convert output verification. * The ability to do co-simulation with Verilog. * An advanced datatype system, independent of traditional datatypes. MyHDL's translator tool automatically writes conversion functions when the target language requires them. MyHDL is developed by Jan Decaluwe. Conversion examples Here, you can see some examples of conversions from MyHDL designs to VHDL and/or Verilog. A small combinatorial design The example is a small combinatorial design, more specifically the binary to Gray code converter: def bin2gray(B, G, width: int): """Gray encoder. B -- input intbv signal, binary encoded ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Lustre (programming Language)

Lustre is a formally defined, declarative, and synchronous dataflow programming language for programming reactive systems. It began as a research project in the early 1980s. A formal presentation of the language can be found in the 1991 Proceedings of the IEEE. In 1993 it progressed to practical, industrial use in a commercial product as the core language of the industrial environment SCADE, developed by Esterel Technologies. It is now used for critical control software in aircraft, helicopters, and nuclear power plants. Structure of Lustre programs A Lustre program is a series of ''node'' definitions, written as: node foo(a : bool) returns (b : bool); let b = not a; tel Where foo is the name of the node, a is the name of the single input of this node and b is the name of the single output. In this example the node foo returns the negation of its input a, which is the expected result. Inner variables Additional internal variables can be declared as follows: node Nand(X,Y ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Icarus Verilog

Icarus Verilog is an implementation of the Verilog hardware description language compiler that generates netlists in the desired format ( EDIF) and a simulator. It supports the 1995, 2001 and 2005 versions of the standard, portions of SystemVerilog, and some extensions. Icarus Verilog is available for Linux, FreeBSD, OpenSolaris, AIX, Microsoft Windows, and . Released under the GNU General Public License, Icarus Verilog is free software, an alternative to proprietary software like Cadence's Verilog-XL. As of release 0.9, Icarus is composed of a Verilog compiler (including a Verilog preprocessor) with support for plug-in backends, and a virtual machine that simulates the design. To view waveforms, a program like GTKWave can be used. Release v10.0, besides general improvements and bug fixes, added preliminary support for VHDL VHDL (Very High Speed Integrated Circuit Program, VHSIC Hardware Description Language) is a hardware description language that can model the beha ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Handel-C

Handel-C is a high-level hardware description language aimed at low-level hardware and is most commonly used in programming FPGAs. Handel-C is to hardware design what the first high-level programming languages were to programming CPUs. It is a turing-complete rich subset of the C programming language, with an emphasis on parallel computing. Unlike many other hardware design languages (HDL) that target a specific computer architecture Handel-C can be compiled to a number of HDLs and then synthesised to the corresponding hardware. This frees developers to concentrate on the programming task at hand rather than the idiosyncrasies of a specific design language and architecture. Additional features Handel-C's subset of C includes all common C language features necessary to describe complex algorithms. Like many embedded C compilers, floating point data types were omitted. Floating point arithmetic is supported through external libraries that are very efficient. Parallel programs ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |