|

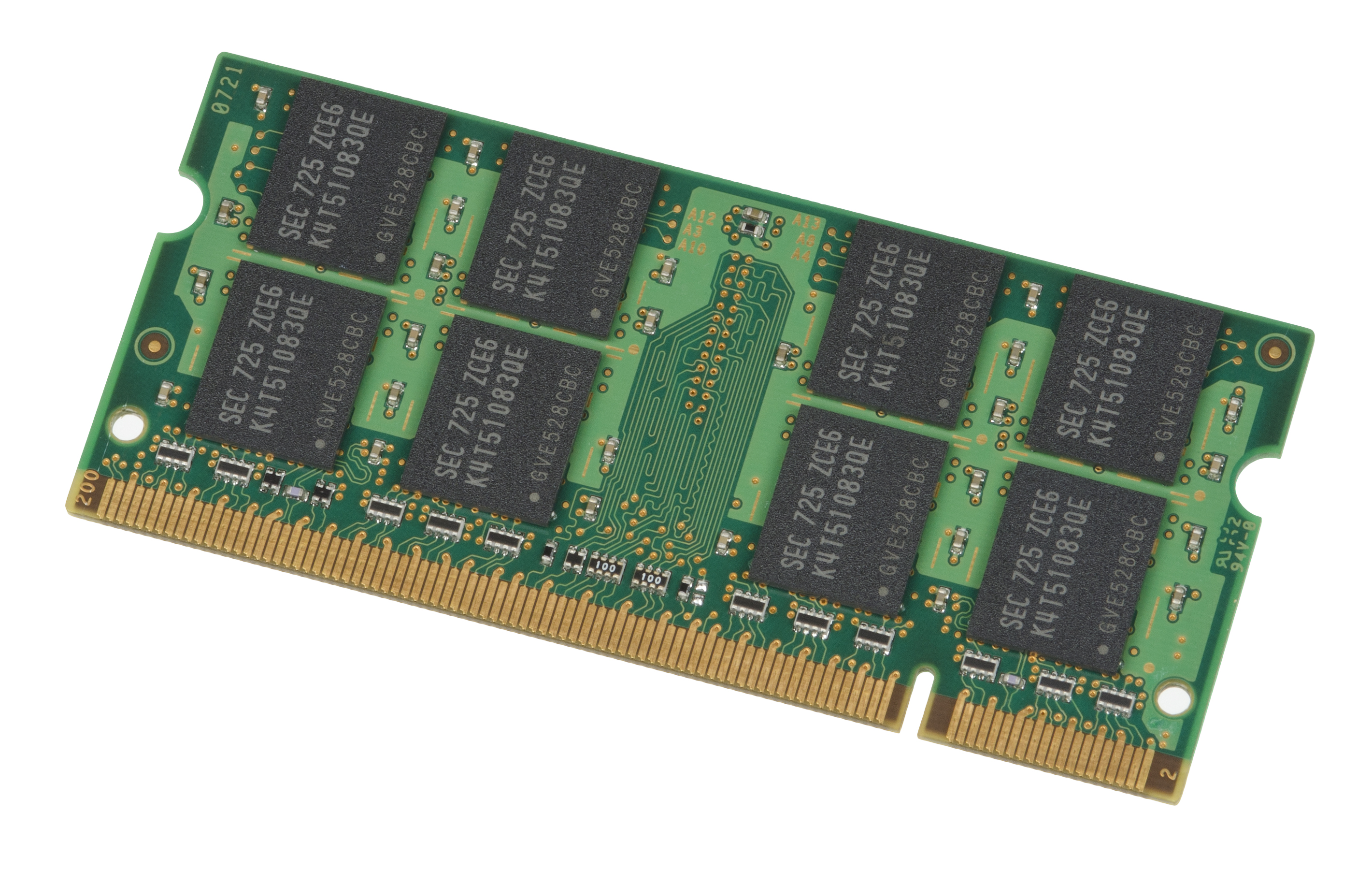

Dual In-line Memory Module

A DIMM (Dual In-line Memory Module) is a popular type of memory module used in computers. It is a printed circuit board with one or both sides (front and back) holding DRAM integrated circuit, chips and Pin (electronics), pins. The vast majority of DIMMs are manufactured in compliance with JEDEC memory standards, although there are proprietary DIMMs. DIMMs come in a variety of speeds and capacities, and are generally one of two lengths: PC, which are , and laptop (SO-DIMM), which are about half the length at . History DIMMs (Dual In-line Memory Module) were a 1990s upgrade for SIMMs (Single In-line Memory Modules) as Intel P5 (microarchitecture), P5-based Pentium processors began to gain market share. The Pentium had a 64-bit bus (computing), bus width, which would require SIMMs installed in matched pairs in order to populate the data bus. The processor would then access the two SIMMs in parallel. DIMMs were introduced to eliminate this disadvantage. The contacts on SIMMs on b ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

168 Pin And 184 Pin DIMM

Year 168 (Roman numerals, CLXVIII) was a leap year starting on Thursday of the Julian calendar. At the time, it was known as the Year of the Consulship of Apronianus and Paullus (or, less frequently, year 921 ''Ab urbe condita''). The denomination 168 for this year has been used since the early medieval period, when the Anno Domini calendar era became the prevalent method in Europe for naming years. Events By place Roman Empire * Emperor Marcus Aurelius and his adopted brother Lucius Verus leave Ancient Rome, Rome, and establish their headquarters at Aquileia. * The Roman army crosses the Alps into Pannonia, and subdues the Marcomanni at Carnuntum, north of the Danube. Asia * Emperor Ling of Han succeeds Emperor Huan of Han as the emperor of the Chinese Han dynasty, Han Dynasty; the first year of the ''Jianning'' era. Births * Cao Ren, Chinese general (d. 223) * Gu Yong, Chinese chancellor (d. 243) * Li Tong (Wenda), Li Tong, Chinese general (d. 209) Deaths * ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR SDRAM

Double Data Rate Synchronous Dynamic Random-Access Memory (DDR SDRAM) is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) class of memory integrated circuits used in computers. DDR SDRAM, also retroactively called DDR1 SDRAM, has been superseded by DDR2 SDRAM, DDR3 SDRAM, DDR4 SDRAM and DDR5 SDRAM. None of its successors are forward or backward compatible with DDR1 SDRAM, meaning DDR2, DDR3, DDR4 and DDR5 memory modules will not work on DDR1-equipped motherboards, and vice versa. Compared to single data rate ( SDR) SDRAM, the DDR SDRAM interface makes higher transfer rates possible through more strict control of the timing of the electrical data and clock signals. Implementations often have to use schemes such as phase-locked loops and self-calibration to reach the required timing accuracy. The interface uses double pumping (transferring data on both the rising and falling edges of the clock signal) to double data bus bandwidth without a cor ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

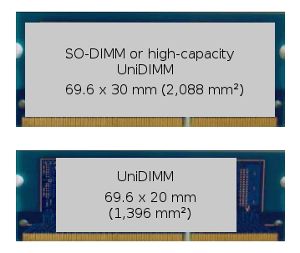

UniDIMM

UniDIMM (short for Universal DIMM) is a specification for dual in-line memory modules (DIMMs), which are printed circuit boards (PCBs) designed to carry dynamic random-access memory (DRAM) chips. UniDIMMs can be populated with either DDR3 or DDR4 chips, with no support for any additional memory control logic; as a result, the computer's memory controller must support both DDR3 and DDR4 memory standards. The UniDIMM specification was created by Intel for its Skylake microarchitecture, whose integrated memory controller (IMC) supports both DDR3 (more specifically, the DDR3L low-voltage variant) and DDR4 memory technologies. UniDIMM is a SO-DIMM form factor available in two dimensions: for the standard UniDIMM version (the same size as DDR4 SO-DIMMs), and for the low-profile version. UniDIMMs have a 260-pin edge connector, which has the same pin count as the one on DDR4 SO-DIMMs, with the keying notch in a position that prevents incompatible installation by making UniDIMMs ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR5 SDRAM

Double Data Rate 5 Synchronous Dynamic Random-Access Memory (DDR5 SDRAM) is a type of synchronous dynamic random-access memory. Compared to its predecessor DDR4 SDRAM, DDR5 was planned to reduce power consumption, while doubling bandwidth. The standard, originally targeted for 2018, was released on July 14, 2020. A new feature called Decision Feedback Equalization (DFE) enables input/output (I/O) speed scalability for higher bandwidth and performance improvement. DDR5 has about the same latency as DDR4 and DDR3. DDR5 octuples the maximum DIMM capacity from 64 GB to 512 GB. DDR5 also has higher frequencies than DDR4, up to 9600 MT/s is currently possible, 8200 MT/s translates into around 66 GB/s of bandwidth. Using liquid nitrogen 13000 MT/s speeds were achieved. Rambus announced a working DDR5 dual in-line memory module (DIMM) in September 2017. On November 15, 2018, SK Hynix announced completion of its first DDR5 RAM chip; running at 5.2 GT/s at 1.1 V ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR4 SDRAM

Double Data Rate 4 Synchronous Dynamic Random-Access Memory (DDR4 SDRAM) is a type of synchronous dynamic random-access memory with a high bandwidth (" double data rate") interface. Released to the market in 2014, it is a variant of dynamic random-access memory (DRAM), some of which have been in use since the early 1970s, and a higher-speed successor to the DDR2 and DDR3 technologies. DDR4 is not compatible with any earlier type of random-access memory (RAM) due to different signaling voltage and physical interface, besides other factors. DDR4 SDRAM was released to the public market in Q2 2014, focusing on ECC memory, while the non-ECC DDR4 modules became available in Q3 2014, accompanying the launch of Haswell-E processors that require DDR4 memory. Features The primary advantages of DDR4 over its predecessor, DDR3, include higher module density and lower voltage requirements, coupled with higher data rate transfer speeds. The DDR4 standard allows for DIMMs of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Hewlett-Packard

The Hewlett-Packard Company, commonly shortened to Hewlett-Packard ( ) or HP, was an American multinational information technology company. It was founded by Bill Hewlett and David Packard in 1939 in a one-car garage in Palo Alto, California, where the company would remain headquartered for the remainder of its lifetime; this HP Garage is now a designated landmark and marked with a plaque calling it the "Birthplace of 'Silicon Valley. HP developed and provided a wide variety of hardware components, as well as software and related services, to consumers, small and medium-sized businesses (small and medium-sized enterprises, SMBs), and fairly large companies, including customers in government sectors, until the company officially split into Hewlett Packard Enterprise and HP Inc. in 2015. HP initially produced a line of electronic test and measurement equipment. It won its first big contract in 1938 to provide the HP 200B, a variation of its first product, the HP 200A low-distor ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

FB-DIMM

A Fully Buffered DIMM (FB-DIMM) is a type of memory module used in computer systems. It is designed to improve memory performance and capacity by allowing multiple memory modules to be each connected to the memory controller using a serial interface, rather than a parallel one. Unlike the parallel bus architecture of traditional DRAMs, an FB-DIMM has a serial interface between the memory controller and the ''advanced memory buffer'' (AMB). Conventionally, data lines from the memory controller have to be connected to data lines in every Dynamic random-access memory, DRAM module, i.e. via multidrop buses. As the memory width increases together with the access speed, the signal degrades at the interface between the bus and the device. This limits the speed and memory density, so FB-DIMMs take a different approach to solve the problem. 240-pin DDR2 FB-DIMMs are neither mechanically nor electrically compatible with conventional 240-pin DDR2 DIMMs. As a result, those two DIMM types are n ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR3 SDRAM

Double Data Rate 3 Synchronous Dynamic Random-Access Memory (DDR3 SDRAM) is a type of synchronous dynamic random-access memory (SDRAM) with a high bandwidth (" double data rate") interface, and has been in use since 2007. It is the higher-speed successor to DDR and DDR2 and predecessor to DDR4 synchronous dynamic random-access memory (SDRAM) chips. DDR3 SDRAM is neither forward nor backward compatible with any earlier type of random-access memory (RAM) because of different signaling voltages, timings, and other factors. DDR3 is a DRAM interface specification. The actual DRAM arrays that store the data are similar to earlier types, with similar performance. The primary benefit of DDR3 SDRAM over its immediate predecessor DDR2 SDRAM, is its ability to transfer data at twice the rate (eight times the speed of its internal memory arrays), enabling higher bandwidth or peak data rates. The DDR3 standard permits DRAM chip capacities of up to 8 gigabits (Gbit) (so 1 gigabyte by ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR2 SDRAM

Double Data Rate 2 Synchronous Dynamic Random-Access Memory (DDR2 SDRAM) is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) interface. It is a JEDEC standard (JESD79-2); first published in September 2003. DDR2 succeeded the original DDR SDRAM specification, and was itself succeeded by DDR3 SDRAM in 2007. DDR2 DIMMs are neither forward compatible with DDR3 nor backward compatible with DDR. In addition to double pumping the data bus as in DDR SDRAM (transferring data on the rising and falling edges of the bus clock signal), DDR2 allows higher bus speed and requires lower power by running the internal clock at half the speed of the data bus. The two factors combine to produce a total of four data transfers per internal clock cycle. Since the DDR2 internal clock runs at half the DDR external clock rate, DDR2 memory operating at the same external data bus clock rate as DDR results in DDR2 being able to provide the same bandwidth but with better la ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |