|

Cache Coherency

In computer architecture, cache coherence is the uniformity of shared resource data that is stored in multiple local caches. In a cache coherent system, if multiple clients have a cached copy of the same region of a shared memory resource, all copies are the same. Without cache coherence, a change made to the region by one client may not be seen by others, and errors can result when the data used by different clients is mismatched. A cache coherence protocol is used to maintain cache coherency. The two main types are snooping and directory-based protocols. Cache coherence is of particular relevance in multiprocessing systems, where each CPU may have its own local cache of a shared memory resource. Overview In a shared memory multiprocessor system with a separate cache memory for each processor, it is possible to have many copies of shared data: one copy in the main memory and one in the local cache of each processor that requested it. When one of the copies of data is c ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

MSI Protocol

In computing, the MSI protocol - a basic Cache coherence, cache-coherence protocol - operates in multiprocessor systems. As with other cache coherency protocols, the letters of the protocol name identify the possible states in which a cache line can be. Overview In MSI, each block contained inside a cache can have one of three possible states: *Modified: The block has been modified in the CPU cache, cache. The data in the cache is then inconsistent with the backing store (e.g. Main memory, memory). A cache with a block in the "M" state has the responsibility to write the block to the backing store when it is evicted. *Shared: This block is unmodified and exists in read-only state in at least one cache. The cache can evict the data without writing it to the backing store. *Invalid: This block is either not present in the current cache or has been invalidated by a bus request, and must be fetched from memory or another CPU cache, cache if the block is to be stored in this cac ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Directory-based Coherence

Directory-based coherence is a mechanism to handle cache coherence problem in distributed shared memory (DSM) a.k.a. non-uniform memory access (NUMA). Another popular way is to use a special type of computer Bus (computing), bus between all the nodes as a "shared bus" (a.k.a. system bus). Directory-based coherence uses a special Directory (computing), directory to serve instead of the shared bus in the bus-based coherence protocols. Both of these designs use the corresponding medium (i.e. directory or bus) as a tool to facilitate the communication between different Node (networking), nodes, and to guarantee that the coherence protocol is working properly along all the communicating nodes. In directory based cache coherence, this is done by using this directory to keep track of the status of all Cache memory, cache blocks, the status of each block includes in which cache coherence "State (computer science), state" that block is, and which nodes are sharing that block at that time, whic ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Consistency Model

In computer science, a consistency model specifies a contract between the programmer and a system, wherein the system guarantees that if the programmer follows the rules for operations on memory, memory will be data consistency, consistent and the results of reading, writing, or updating memory will be predictable. Consistency models are used in Distributed computing, distributed systems like distributed shared memory systems or distributed data stores (such as filesystems, databases, optimistic replication systems or web caching). Consistency is different from coherence, which occurs in systems that are cache coherence, cached or cache-less, and is consistency of data with respect to all processors. Coherence deals with maintaining a global order in which writes to a single location or single variable are seen by all processors. Consistency deals with the ordering of operations to multiple locations with respect to all processors. High level languages, such as C++ and Java (progr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Arm Ltd

Arm Holdings plc (formerly an acronym for Advanced RISC Machines and originally Acorn RISC Machine) is a British semiconductor and software design company based in Cambridge, England, whose primary business is the design of central processing unit (CPU) cores that implement the ARM architecture family of instruction sets. It also designs other chips, provides software development tools under the DS-5, RealView and Keil brands, and provides systems and platforms, system-on-a-chip (SoC) infrastructure and software. As a "holding" company, it also holds shares of other companies. Since 2016, it has been majority owned by Japanese conglomerate SoftBank Group. While ARM CPUs first appeared in the Acorn Archimedes, a desktop computer, today's systems include mostly embedded systems, including ARM CPUs used in virtually all modern smartphones. Processors based on designs licensed from Arm, or designed by licensees of one of the ARM instruction set architectures, are used in all cl ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

System On A Chip

A system on a chip (SoC) is an integrated circuit that combines most or all key components of a computer or Electronics, electronic system onto a single microchip. Typically, an SoC includes a central processing unit (CPU) with computer memory, memory, input/output, and computer data storage#Secondary storage, data storage control functions, along with optional features like a graphics processing unit (GPU), Wi-Fi connectivity, and radio frequency processing. This high level of integration minimizes the need for separate, discrete components, thereby enhancing Performance per watt, power efficiency and simplifying device design. High-performance SoCs are often paired with dedicated memory, such as LPDDR, and flash storage chips, such as Universal Flash Storage, eUFS or eMMC, which may be stacked directly on top of the SoC in a Package on a package, package-on-package (PoP) configuration or placed nearby on the motherboard. Some SoCs also operate alongside specialized chips, such ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Ltd

Arm Holdings plc (formerly an acronym for Advanced RISC Machines and originally Acorn RISC Machine) is a British semiconductor and software design company based in Cambridge, England, whose primary business is the design of central processing unit (CPU) cores that implement the ARM architecture family of instruction sets. It also designs other chips, provides software development tools under the DS-5, RealView and Keil brands, and provides systems and platforms, system-on-a-chip (SoC) infrastructure and software. As a "holding" company, it also holds shares of other companies. Since 2016, it has been majority owned by Japanese conglomerate SoftBank Group. While ARM CPUs first appeared in the Acorn Archimedes, a desktop computer, today's systems include mostly embedded systems, including ARM CPUs used in virtually all modern smartphones. Processors based on designs licensed from Arm, or designed by licensees of one of the ARM instruction set architectures, are used in all cl ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

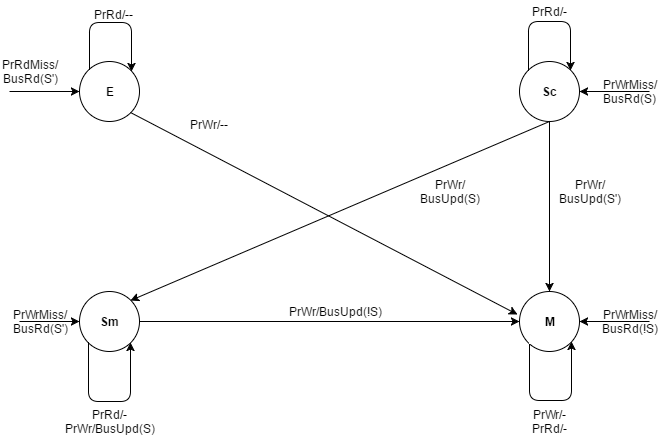

Dragon Protocol

The Dragon Protocol is an update based cache coherence protocol used in multi-processor systems. Write propagation is performed by directly updating all the cached values across multiple processors. Update based protocols such as the Dragon protocol perform efficiently when a write to a cache block is followed by several reads made by other processors, since the updated cache block is readily available across caches associated with all the processors. States Each cache block resides in one of the four states: exclusive-clean, shared-clean, shared-modified and modify. * Exclusive-clean (E): This means that the cache block was first fetched by the current processor and has not been accessed by any other processor since. * Shared clean (Sc): This means that the cache block definitely exists in multiple processor’s caches, and that the current processor is not the last one to write the block. States E and Sc are maintained separately by the protocol to prevent read-write operations ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Firefly (cache Coherence Protocol)

The Firefly cache coherence protocol is the schema used in the DEC Firefly multiprocessor workstation, developed by DEC Systems Research Center. This protocol is a 3 State Write Update Cache Coherence Protocol. Unlike the Dragon protocol, the Firefly protocol updates the Main Memory as well as the Local caches on Write Update Bus Transition. Thus the Shared Clean and Shared Modified States present in case of Dragon Protocol, are not distinguished between in case of Firefly Protocol. States In this protocol, the following states can be assigned to each block: * Valid-Exclusive(V): The cache block is valid, clean and only resides in one cache. * Shared(S): The cache block is valid, clean and may reside in multiple caches. * Dirty(D): The block is the only copy of the memory and it is dirty i.e. its value has been modified since being brought from the memory. This is the only state that generates a write-back when the block is replaced in the cache. These states correspond to the ' ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Write-once (cache Coherence)

In cache coherency protocol literature, Write-Once was the first MESI protocol defined. It has the optimization of executing write-through on the first write and a write-back on all subsequent writes, reducing the overall bus traffic in consecutive writes to the computer memory. It was first described by James R. Goodman in (1983). Cache coherence protocols are an important issue in Symmetric multiprocessing systems, where each CPU maintains a cache of the memory. States In this protocol, each block in the local cache is in one of these four states: * Invalid: This block has an incoherent copy of the memory. * Valid: This block has a coherent copy of the memory. The data may be possibly shared, but its content is not modified. * Reserved: The block is the only copy of the memory, but it is still coherent. No write-back is needed if the block is replaced. * Dirty: The block is the only copy of the memory and it is incoherent. This copy was written one or more times. This is the on ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

MESIF Protocol

The MESIF protocol is a cache coherency and memory coherence protocol developed by Intel for cache coherent non-uniform memory architectures. The protocol consists of five states, Modified (M), Exclusive (E), Shared (S), Invalid (I) and Forward (F). The M, E, S and I states are the same as in the MESI protocol. The F state is a specialized form of the S state, and indicates that a cache should act as a designated responder for any requests for the given line. The protocol ensures that, if any cache holds a line in the S state, at most one (other) cache holds it in the F state. In a system of caches employing the MESI protocol, a cache line request that is received by multiple caches holding a line in the S state will be serviced inefficiently. It may either be satisfied from (slow) main memory, or ''all'' the sharing caches could respond, bombarding the requestor with redundant responses. In a system of caches employing the MESIF protocol, a cache line request will be responded t ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |