|

Whiskey Lake (microarchitecture)

Whiskey Lake is Intel's codename for a family of third-generation 14nm Skylake low-power mobile processors. Intel announced Whiskey Lake on August 28, 2018. Changes * 14++ nm process, same as Coffee Lake * Increased turbo clocks (300–600 MHz) * 14 nm PCH * Native USB 3.1 gen 2 support (10 Gbit/s) * Integrated Wi-Fi 802.11ac 160 MHz / WiFi 5 and Bluetooth 5.0 * Intel Optane Memory support List of Whiskey Lake CPUs Mobile processors The TDP for these CPUs is 15 W, but is configurable. Core i5-8365U and i7-8665U support Intel vPro Technology Pentium Gold and Celeron CPUs lack AVX2 Advanced Vector Extensions (AVX, also known as Gesher New Instructions and then Sandy Bridge New Instructions) are SIMD extensions to the x86 instruction set architecture for microprocessors from Intel and Advanced Micro Devices (AMD). They w ... support. References {{IntelProcessorRoadmap Intel microarchitectures Intel x86 microprocessors X86 micr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

14 Nanometer

The "14 nanometer process" refers to a marketing term for the MOSFET technology node that is the successor to the "22nm" (or "20nm") node. The "14nm" was so named by the International Technology Roadmap for Semiconductors (ITRS). Until about 2011, the node following "22nm" was expected to be "16nm". All "14nm" nodes use FinFET (fin field-effect transistor) technology, a type of multi-gate MOSFET technology that is a non-planar evolution of planar silicon CMOS technology. Since at least 1997, "process nodes" have been named purely on a marketing basis, and have no relation to the dimensions on the integrated circuit; neither gate length, metal pitch or gate pitch on a "14nm" device is fourteen nanometers. For example, TSMC and Samsung's "10 nm" processes are somewhere between Intel's "14 nm" and "10 nm" processes in transistor density, and TSMC's " 7 nm" processes are dimensionally similar to Intel's "10 nm" process. Samsung Electronics taped out a "1 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Advanced Vector Extensions 2

Advanced Vector Extensions (AVX, also known as Gesher New Instructions and then Sandy Bridge New Instructions) are SIMD extensions to the x86 instruction set architecture for microprocessors from Intel and Advanced Micro Devices (AMD). They were proposed by Intel in March 2008 and first supported by Intel with the Sandy Bridge microarchitecture shipping in Q1 2011 and later by AMD with the Bulldozer microarchitecture shipping in Q4 2011. AVX provides new features, new instructions, and a new coding scheme. AVX2 (also known as Haswell New Instructions) expands most integer commands to 256 bits and introduces new instructions. They were first supported by Intel with the Haswell microarchitecture, which shipped in 2013. AVX-512 expands AVX to 512-bit support using a new EVEX prefix encoding proposed by Intel in July 2013 and first supported by Intel with the Knights Landing co-processor, which shipped in 2016. In conventional processors, AVX-512 was introduced with Skylake serve ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

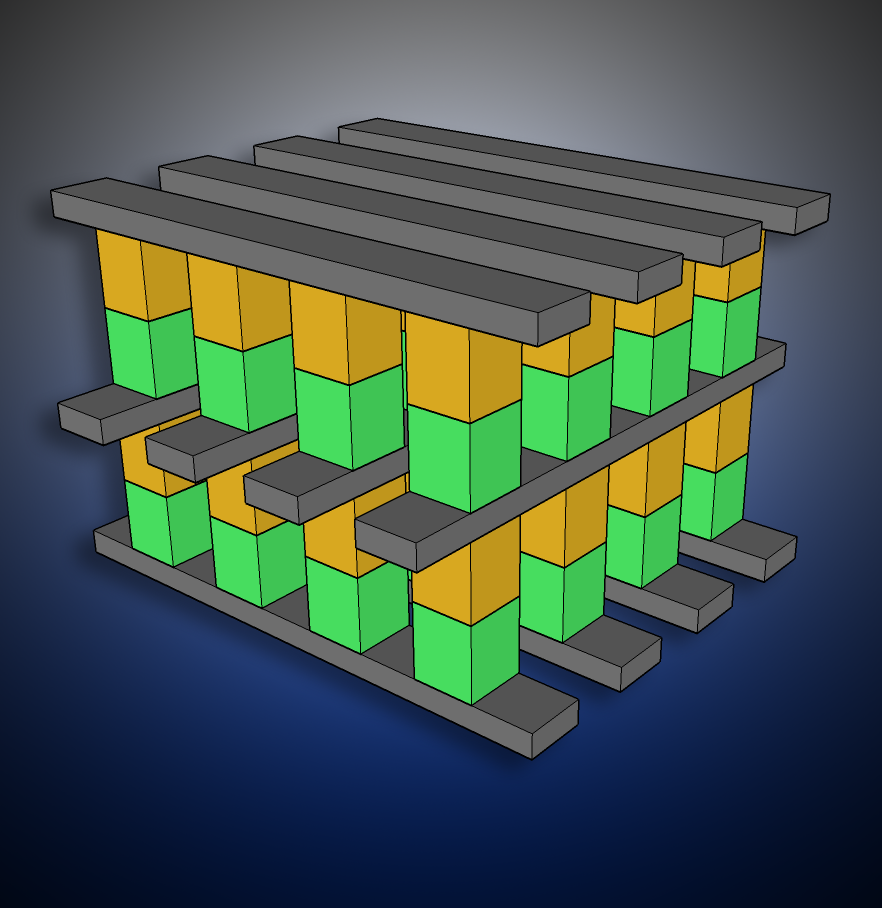

3D XPoint

3D XPoint (pronounced ''three-D cross point'') was a discontinued non-volatile memory (NVM) technology developed jointly by Intel and Micron Technology. It was announced in July 2015 and was available on the open market under the brand name Optane (Intel) from April 2017 to July 2022. Bit storage is based on a change of bulk resistance, in conjunction with a stackable cross-grid data access array, using a technology known as Ovonic Threshold Switch (OTS). Initial prices were less than dynamic random-access memory (DRAM) but more than flash memory. As a non-volatile memory, 3D XPoint had a number of features that distinguish it from other currently available RAM and NVRAM. Although the first generations of 3D XPoint were not especially large or fast, 3D XPoint was used to create some of the fastest SSDs available as of 2019, with small-write latency. As the memory was inherently fast, and byte-addressable, techniques such as read-modify-write and caching used to enhance tra ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Bluetooth

Bluetooth is a short-range wireless technology standard that is used for exchanging data between fixed and mobile devices over short distances and building personal area networks (PANs). In the most widely used mode, transmission power is limited to 2.5 milliwatts, giving it a very short range of up to . It employs Ultra high frequency, UHF radio waves in the ISM bands, from 2.402GHz to 2.48GHz. It is mainly used as an alternative to wired connections to exchange files between nearby portable devices and connect cell phones and music players with wireless headphones, wireless speakers, HIFI systems, car audio and wireless transmission between TVs and soundbars. Bluetooth is managed by the Bluetooth Special Interest Group (SIG), which has more than 35,000 member companies in the areas of telecommunication, computing, networking, and consumer electronics. The Institute of Electrical and Electronics Engineers, IEEE standardized Bluetooth as IEEE 802.15.1 but no longer maintains ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Platform Controller Hub

The Platform Controller Hub (PCH) is a family of Intel's single-chip chipsets, first introduced in 2009. It is the successor to the Intel Hub Architecture, which used two chipsa northbridge and southbridge, and first appeared in the Intel 5 Series. The PCH controls certain data paths and support functions used in conjunction with Intel CPUs. These include clocking (the system clock), Flexible Display Interface (FDI) and Direct Media Interface (DMI), although FDI is used only when the chipset is required to support a processor with integrated graphics. As such, I/O functions are reassigned between this new central hub and the CPU compared to the previous architecture: some northbridge functions, the memory controller and PCIe lanes, were integrated into the CPU while the PCH took over the remaining functions in addition to the traditional roles of the southbridge. AMD has its equivalent for the PCH, known simply as a chipset since the release of the Zen architecture in 2017. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

List Of Intel Codenames

Intel has historically named integrated circuit (IC) development projects after geographical names of towns, rivers or mountains near the location of the Intel facility responsible for the IC. Many of these are in the American West, particularly in Oregon (where most of Intel's CPU projects are designed; see famous codenames). As Intel's development activities have expanded, this nomenclature has expanded to Israel and India, and some older codenames refer to celestial bodies. The following table lists known Intel codenames along with a brief explanation of their meaning and their likely namesake, and the year of their earliest known public appearance. Most processors after a certain date were named after cities that could be found on a map of the United States. This was done for trademark considerations. Banias was the last of the non-US city names. Gesher was renamed to Sandy Bridge to comply with the new rule. Dothan is a city both in Israel and in Alabama. See also * Li ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Comet Lake

Comet Lake is Intel's codename for its 10th generation Core processors. They are manufactured using Intel's third 14 nm Skylake process revision, succeeding the Whiskey Lake U-series mobile processor and Coffee Lake desktop processor families. Intel announced low-power mobile Comet Lake-U CPUs on August 21, 2019, H-series mobile CPUs on April 2, 2020, desktop Comet Lake-S CPUs April 30, 2020, and Xeon W-1200 series workstation CPUs on May 13, 2020. Comet Lake processors and Ice Lake 10 nm processors are together branded as the Intel "10th Generation Core" family. In March 2021, Intel officially launched Comet Lake-Refresh Core i3 and Pentium CPUs on the same day as the 11th Gen Core Rocket Lake launch. The low-power mobile Comet Lake-U Core and Celeron 5205U CPUs were discontinued on July 7, 2021. Generational changes All Comet Lake CPUs feature an updated Platform Controller Hub with CNVio2 controller with Wi-Fi 6 and external AX201 CRF module support. Comet Lake-S ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ice Lake (microprocessor)

Ice Lake is Intel's List of Intel codenames, codename for the 10th generation Intel Core mobile and 3rd generation Xeon Scalable server processors based on the Sunny Cove (microarchitecture), Sunny Cove microarchitecture. Ice Lake represents an Architecture step in Intel's process–architecture–optimization model. Produced on the second generation of Intel's 10 nanometer, 10 nm process, 10 nm+, Ice Lake is Intel's second microarchitecture to be manufactured on the 10 nm process, following the limited launch of Cannon Lake (microarchitecture), Cannon Lake in 2018. However, Intel altered their naming scheme in 2020 for the 10 nm process. In this new naming scheme, Ice Lake's manufacturing process is called simply 10 nm, without any appended pluses. Ice Lake CPUs are sold together with the 14 nm Comet Lake CPUs as Intel's "10th Generation Core" product family. There are no Ice Lake desktop or high-power mobile processors; Comet Lake fulfills this ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Kaby Lake Refresh

Kaby Lake is Intel's List of Intel codenames, codename for its seventh generation Intel Core, Core microprocessor family announced on August 30, 2016. Like the preceding Skylake (microarchitecture), Skylake, Kaby Lake is produced using a 14 nanometer Semiconductor device fabrication, manufacturing process technology. Breaking with Intel's previous "Tick–tock model, tick–tock" manufacturing and design model, Kaby Lake represents the optimized step of the newer Process–architecture–optimization model, process–architecture–optimization model. Kaby Lake began shipping to manufacturers and Original equipment manufacturer, OEMs in the second quarter of 2016, with its desktop chips officially launched in January 2017. In August 2017, Intel announced Kaby Lake Refresh (Kaby Lake R) marketed as the 8th generation mobile CPUs, breaking the long cycle where architectures matched the corresponding generations of CPUs and meanwhile also supporting Windows 11. Skylake was anticipate ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel VT-d

x86 virtualization is the use of hardware-assisted virtualization capabilities on an x86/x86-64 CPU. In the late 1990s x86 virtualization was achieved by complex software techniques, necessary to compensate for the processor's lack of hardware-assisted virtualization capabilities while attaining reasonable performance. In 2005 and 2006, both Intel (VT-x) and AMD (AMD-V) introduced limited hardware virtualization support that allowed simpler virtualization software but offered very few speed benefits. Greater hardware support, which allowed substantial speed improvements, came with later processor models. Software-based virtualization The following discussion focuses only on virtualization of the x86 architecture protected mode. In protected mode the operating system kernel runs at a higher privilege such as ring 0, and applications at a lower privilege such as ring 3. In software-based virtualization, a host OS has direct access to hardware while the guest OSs have limited acc ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |