|

TILEPro64

TILE''Pro''64 is a VLIW ISA multicore processor ( Tile processor) manufactured by Tilera. It consists of a cache-coherent mesh network of 64 "tiles", where each tile houses a general purpose processor, cache, and a non-blocking router, which the tile uses to communicate with the other tiles on the processor. The short-pipeline, in-order, three-issue cores implement a VLIW instruction set. Each core has a register file and three functional units: two integer arithmetic logic units and a load-store unit. Each of the cores ("tile") has its own L1 and L2 caches plus an overall virtual L3 cache which is an aggregate of all the L2 caches. A core is able to run a full operating system on its own or multiple cores can be used to run a symmetrical multi-processing operating system. TILE''Pro''64 has four DDR2 controllers at up to 800MT/s, two 10-gigabit Ethernet XAUI interfaces, two four-lane PCIe interfaces, and a "flexible" input/output interface, which can be software-configured to ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

TILEPro64 TileBlock

TILE''Pro''64 is a VLIW ISA multicore processor ( Tile processor) manufactured by Tilera. It consists of a cache-coherent mesh network of 64 "tiles", where each tile houses a general purpose processor, cache, and a non-blocking router, which the tile uses to communicate with the other tiles on the processor. The short-pipeline, in-order, three-issue cores implement a VLIW instruction set. Each core has a register file and three functional units: two integer arithmetic logic units and a load-store unit. Each of the cores ("tile") has its own L1 and L2 caches plus an overall virtual L3 cache which is an aggregate of all the L2 caches. A core is able to run a full operating system on its own or multiple cores can be used to run a symmetrical multi-processing operating system. TILE''Pro''64 has four DDR2 controllers at up to 800MT/s, two 10-gigabit Ethernet XAUI interfaces, two four-lane PCIe interfaces, and a "flexible" input/output interface, which can be software-configured to ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Tilera

Tilera Corporation was a fabless semiconductor company focusing on manycore embedded processor design. The company shipped multiple processors, including the TILE64, TILE''Pro''64, and the TILE''Pro''36, TILE-Gx72, TILE-Gx36, TILE-Gx16 and TILE-Gx9. After a series of company acquisitions. Tilera's intellectual property was eventually acquired by Mellanox, which now ships products that descend from the original Tilera designs. History In 1990, Anant Agarwal led a team of researchers at Massachusetts Institute of Technology to develop scalable multi-processor system built out of large numbers of single chip processors. Alewife machines integrated both shared memory and user-level message passing for inter-node communications. In 1997, Agarwal proposed a follow-on project using a mesh technology to connect multiple cores. The follow-on project, named RAW, commenced in 1997, and was supported by DARPA/NSF's funding of tens of millions, resulting in the first 16-processor tiles m ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Tile Processor

Tile processors for computer hardware, are multicore or manycore chips that contain one-dimensional, or more commonly, two-dimensional arrays of identical tiles. Each tile comprises a compute unit (or a processing engine or CPU), caches and a switch. Tiles can be viewed as adding a switch to each core, where a core comprises a compute unit and caches. In a typical Tile Processor configuration, the switches in each of the tiles are connected to each other using one or more mesh networks. doi:10.1109/MM.2007.89 The Tilera TILE''Pro''64, for example, contains 64 tiles. Each of the tiles comprises a CPU, L1 and L2 caches, and switches for several mesh networks. Other processors in a tile configuration include SEAforth24, Kilocore KC256, XMOS xCORE microcontrollers, and some massively parallel processor array A massively parallel processor array, also known as a multi purpose processor array (MPPA) is a type of integrated circuit which has a massively parallel array of hundreds ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Tilera TILEPro64 BlockDiagram

Tilera Corporation was a fabless semiconductor company focusing on manycore embedded processor design. The company shipped multiple processors, including the TILE64, TILE''Pro''64, and the TILE''Pro''36, TILE-Gx72, TILE-Gx36, TILE-Gx16 and TILE-Gx9. After a series of company acquisitions. Tilera's intellectual property was eventually acquired by Mellanox, which now ships products that descend from the original Tilera designs. History In 1990, Anant Agarwal led a team of researchers at Massachusetts Institute of Technology to develop scalable multi-processor system built out of large numbers of single chip processors. Alewife machines integrated both shared memory and user-level message passing for inter-node communications. In 1997, Agarwal proposed a follow-on project using a mesh technology to connect multiple cores. The follow-on project, named RAW, commenced in 1997, and was supported by DARPA/NSF's funding of tens of millions, resulting in the first 16-processor tiles m ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

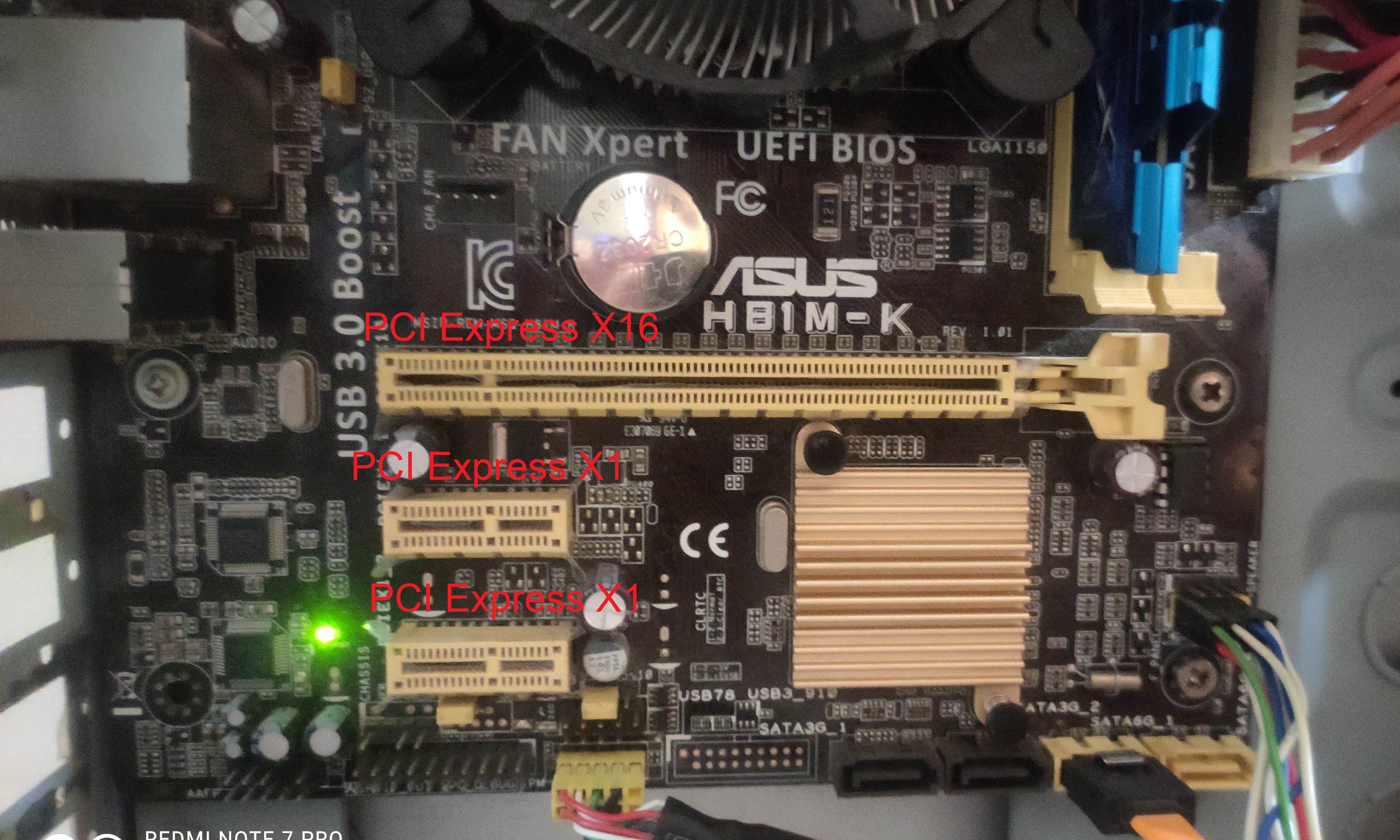

PCIe

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common motherboard interface for personal computers' graphics cards, hard disk drive host adapters, SSDs, Wi-Fi and Ethernet hardware connections. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism (Advanced Error Reporting, AER), and native hot-swap functionality. More recent revisions of the PCIe standard provide hardware support for I/O virtualization. The PCI Express electrical interface is measured by the number of simultaneous lanes. (A lane is a single send/receive line of data. The analogy is a highway with traffic in both directions.) T ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Manycore Processors

Manycore processors are special kinds of multi-core processors designed for a high degree of parallel processing, containing numerous simpler, independent processor cores (from a few tens of cores to thousands or more). Manycore processors are used extensively in embedded computers and high-performance computing. Contrast with multicore architecture Manycore processors are distinct from multi-core processors in being optimized from the outset for a higher degree of explicit parallelism, and for higher throughput (or lower power consumption) at the expense of latency and lower single-thread performance. The broader category of multi-core processors, by contrast, are usually designed to efficiently run ''both'' parallel ''and'' serial code, and therefore place more emphasis on high single-thread performance (e.g. devoting more silicon to out of order execution, deeper pipelines, more superscalar execution units, and larger, more general caches), and shared memory. These techniqu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

6WIND

6WIND is a virtual networking software company delivering disaggregated and cloud-native solutions to CSPs and enterprises globally. The company is privately held and headquartered in the West Paris area, in Montigny-le-Bretonneux. 6WIND has a global presence with offices in the US and APAC. The company provides virtualized networking software which is deployed in bare-metal or in virtual machines on COTS servers in public & private clouds. Their solutions are disaggregated and containerized based on the cloud-native architecture. History 6WIND was founded in 2000 as a spin-out from Thales Group (previously Thomson-CSF), a provider of electronics for aerospace, defense and security. A 3.75 million euro investment from Sofinnova Partners and others was announced in 2004, and 5 million euros in 2004. Partners include Red Hat, VMware and Wind River Systems.EETimes" Wind River, 6Wind partner on multicore CPUs" January 14, 2008. Equipment vendors that provide boards and systems util ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

TILE64

TILE64 is a VLIW ISA multicore processor manufactured by Tilera. It consists of a mesh network of 64 "tiles", where each tile houses a general purpose processor, cache, and a non-blocking router, which the tile uses to communicate with the other tiles on the processor. The short-pipeline, in-order, three-issue cores implement a MIPS-inspired VLIW instruction set. Each core has a register file and three functional units: two integer arithmetic logic units and a load-store unit. Each of the cores ("tile") has its own L1 and L2 caches plus an overall virtual L3 cache which is an aggregate of all the L2 caches. A core is able to run a full operating system on its own or multiple cores can be used to run a symmetrical multi-processing operating system. TILE64 has four DDR2 controllers, two 10-gigabit Ethernet interfaces, two four-lane PCIe interfaces, and a "flexible" input/output interface, which can be software-configured to handle a number of protocols. The processor is fa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

RGMII

The media-independent interface (MII) was originally defined as a standard interface to connect a Fast Ethernet (i.e., ) media access control (MAC) block to a PHY chip. The MII is standardized by IEEE 802.3u and connects different types of PHYs to MACs. Being ''media independent'' means that different types of PHY devices for connecting to different media (i.e. twisted pair, fiber optic, etc.) can be used without redesigning or replacing the MAC hardware. Thus any MAC may be used with any PHY, independent of the network signal transmission media. The MII can be used to connect a MAC to an external PHY using a pluggable connector, or directly to a PHY chip on the same PCB. On a PC the CNR connector Type B carries MII signals. Network data on the interface is framed using the IEEE Ethernet standard. As such it consists of a preamble, start frame delimiter, Ethernet headers, protocol-specific data and a cyclic redundancy check (CRC). The original MII transfers network data usin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

XAUI

10 Gigabit Attachment Unit Interface (XAUI ) is a standard for extending the XGMII (10 Gigabit Media Independent Interface) between the MAC and PHY layer of 10 Gigabit Ethernet (10GbE) defined in Clause 47 of the IEEE 802.3 standard. The name is a concatenation of the Roman numeral X, meaning ten, and the initials of "Attachment Unit Interface". The purpose of the XGMII Extender, which is composed of an XGXS (XGMII Extender Sublayer) at the MAC end, an XGXS at the PHY end and a XAUI between them, is to extend the operational distance of the XGMII and to reduce the number of interface signals. Applications include extending the physical separation possible between MAC and PHY components in a 10 Gigabit Ethernet system distributed across a circuit board. Operation XGMII Extender has the following characteristics: * Simple signal mapping to the XGMII * Independent transmit and receive data paths * Four lanes conveying the XGMII 32-bit data and control * Differential signaling with ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PCI Express

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common motherboard interface for personal computers' graphics cards, hard disk drive host adapters, SSDs, Wi-Fi and Ethernet hardware connections. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism (Advanced Error Reporting, AER), and native hot-swap functionality. More recent revisions of the PCIe standard provide hardware support for I/O virtualization. The PCI Express electrical interface is measured by the number of simultaneous lanes. (A lane is a single send/receive line of data. The analogy is a highway with traffic in both directions. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Memory Controller

The memory controller is a digital circuit that manages the flow of data going to and from the computer's main memory. A memory controller can be a separate chip or integrated into another chip, such as being placed on the same die or as an integral part of a microprocessor; in the latter case, it is usually called an integrated memory controller (IMC). A memory controller is sometimes also called a memory chip controller (MCC) or a memory controller unit (MCU). A common form of memory controller is the memory management unit (MMU) which in many operating systems implements virtual addressing. History Most modern desktop or workstation microprocessors use an ''integrated memory controller'' (IMC), including microprocessors from Intel, AMD, and those built around the ARM architecture. Prior to K8 (circa 2003), AMD microprocessors had a memory controller implemented on their motherboard's northbridge. In K8 and later, AMD employed an integrated memory controller. Likewis ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

_connector_on_sun_ultra_1.jpg)