|

ST200 Family

The ST200 is a family of very long instruction word (VLIW) processor cores based on technology jointly developed by Hewlett-Packard Laboratories and STMicroelectronics under the name Lx. The main application of the ST200 family is embedded media processing. Lx architecture The Lx architecture is closer to the original VLIW architecture defined by the Trace processor series from Multiflow than to the EPIC architectures exemplified by the IA-64. Precisely, the Lx is a symmetric clustered architecture, where clusters communicate through explicit send and receive instructions. Each cluster executes up to 4 instructions per cycle with a maximum of one control instruction (goto, jump, call, return), one memory instruction (load, store, pre-fetch), and two multiply instructions per cycle. All arithmetic instructions operate on integer values with operands belonging either to the general register file (64 x 32-bit) or to the branch register file (8 x 1-bit). General register $r0 always re ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Very Long Instruction Word

Very long instruction word (VLIW) refers to instruction set architectures designed to exploit instruction level parallelism (ILP). Whereas conventional central processing units (CPU, processor) mostly allow programs to specify instructions to execute in sequence only, a VLIW processor allows programs to explicitly specify instructions to execute in parallel. This design is intended to allow higher performance without the complexity inherent in some other designs. Overview The traditional means to improve performance in processors include dividing instructions into substeps so the instructions can be executed partly at the same time (termed ''pipelining''), dispatching individual instructions to be executed independently, in different parts of the processor (''superscalar architectures''), and even executing instructions in an order different from the program (''out-of-order execution''). These methods all complicate hardware (larger circuits, higher cost and energy use) because ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Hewlett-Packard

The Hewlett-Packard Company, commonly shortened to Hewlett-Packard ( ) or HP, was an American multinational information technology company headquartered in Palo Alto, California. HP developed and provided a wide variety of hardware components, as well as software and related services to consumers, small and medium-sized businesses ( SMBs), and large enterprises, including customers in the government, health, and education sectors. The company was founded in a one-car garage in Palo Alto by Bill Hewlett and David Packard in 1939, and initially produced a line of electronic test and measurement equipment. The HP Garage at 367 Addison Avenue is now designated an official California Historical Landmark, and is marked with a plaque calling it the "Birthplace of 'Silicon Valley'". The company won its first big contract in 1938 to provide test and measurement instruments for Walt Disney's production of the animated film ''Fantasia'', which allowed Hewlett and Packard to formally esta ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

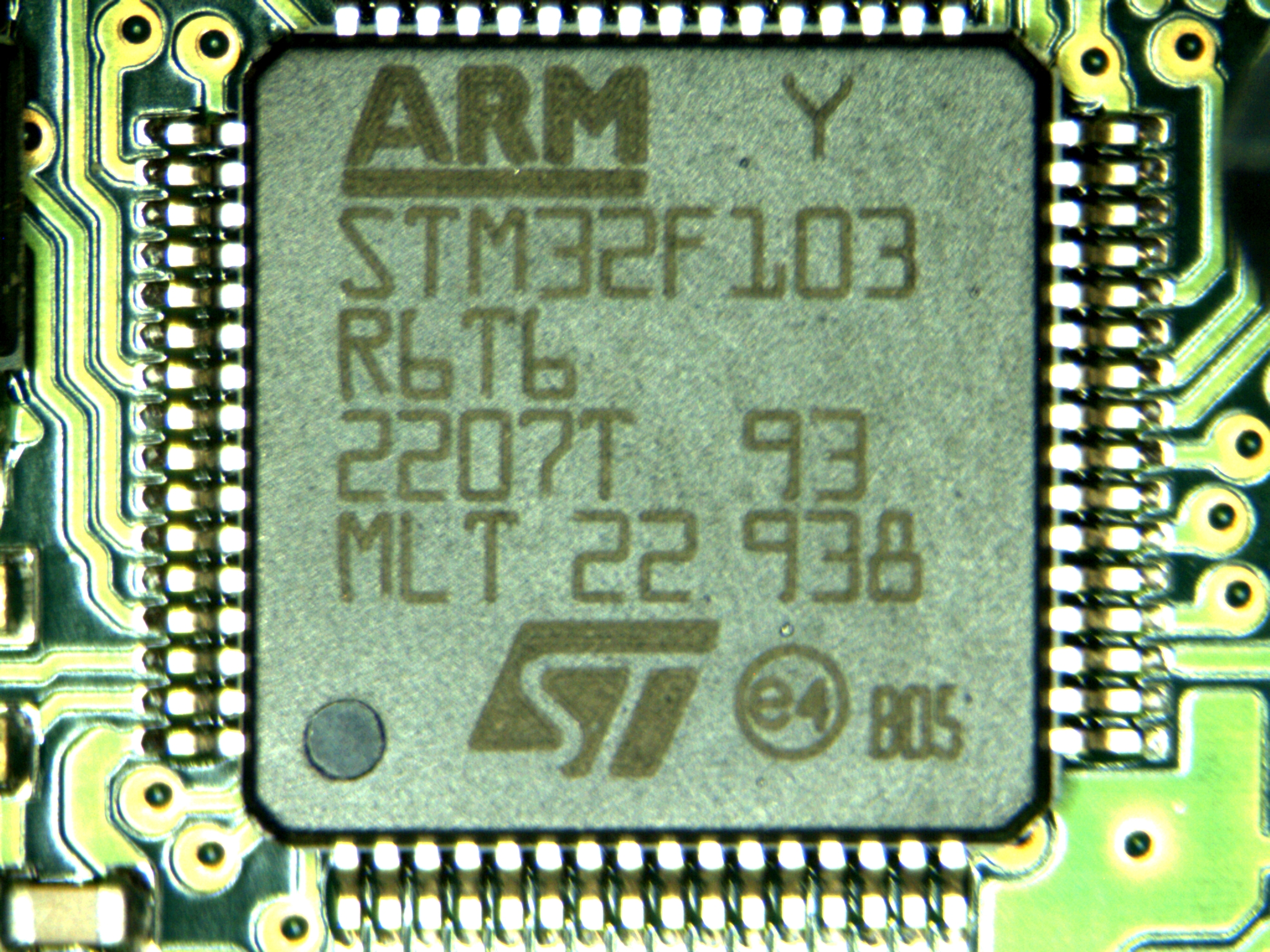

STMicroelectronics

STMicroelectronics N.V. commonly referred as ST or STMicro is a Dutch multinational corporation and technology company of French-Italian origin headquartered in Plan-les-Ouates near Geneva, Switzerland and listed on the French stock market. ST is the largest European semiconductor contract manufacturing and design company. The company resulted from the merger of two government-owned semiconductor companies in 1987: Thomson Semiconducteurs of France and SGS Microelettronica of Italy. History ST was formed in 1987 by the merger of two government-owned semiconductor companies: Italian SGS Microelettronica (where SGS stands for ''Società Generale Semiconduttori'', "Semiconductors' General Company"), and French Thomson Semiconducteurs, the semiconductor arm of Thomson. SGS Microelettronica originated in 1972 from a previous merger of two companies: * ATES (Aquila Tubi e Semiconduttori), a vacuum tube and semiconductor maker headquartered in L'Aquila, the regional capital of the r ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Multiflow

{{no references, date=June 2019 Multiflow Computer, Inc., founded in April, 1984 near New Haven, Connecticut, USA, was a manufacturer and seller of minisupercomputer hardware and software embodying the VLIW design style. Multiflow, incorporated in Delaware, ended operations in March, 1990, after selling about 125 VLIW minisupercomputers in the United States, Europe, and Japan. While Multiflow's commercial success was small and short-lived, its technical success and the dissemination of its technology and people had a great effect on the future of computer science and the computer industry. Multiflow's computers were arguably the most novel ever to be broadly sold, programmed, and used like conventional computers. (Other novel computers either required novel programming, or represented more incremental steps beyond existing computers.) Along with Cydrome, an attached-VLIW minisupercomputer company that had less commercial success, Multiflow demonstrated that the VLIW design style wa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Explicitly Parallel Instruction Computing

Explicitly parallel instruction computing (EPIC) is a term coined in 1997 by the HP–Intel alliance to describe a computing paradigm that researchers had been investigating since the early 1980s. This paradigm is also called ''Independence'' architectures. It was the basis for Intel and HP development of the Intel Itanium architecture, and HP later asserted that "EPIC" was merely an old term for the Itanium architecture. EPIC permits microprocessors to execute software instructions in parallel by using the compiler, rather than complex on-die circuitry, to control parallel instruction execution. This was intended to allow simple performance scaling without resorting to higher clock frequencies. Roots in VLIW By 1989, researchers at HP recognized that reduced instruction set computer (RISC) architectures were reaching a limit at one instruction per cycle. They began an investigation into a new architecture, later named EPIC. The basis for the research was VLIW, in which multip ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IA-64

IA-64 (Intel Itanium architecture) is the instruction set architecture (ISA) of the Itanium family of 64-bit Intel microprocessors. The basic ISA specification originated at Hewlett-Packard (HP), and was subsequently implemented by Intel in collaboration with HP. The first Itanium processor, codenamed ''Merced'', was released in 2001. The Itanium architecture is based on explicit instruction-level parallelism, in which the compiler decides which instructions to execute in parallel. This contrasts with superscalar architectures, which depend on the processor to manage instruction dependencies at runtime. In all Itanium models, up to and including '' Tukwila'', cores execute up to six instructions per clock cycle. In 2008, Itanium was the fourth-most deployed microprocessor architecture for enterprise-class systems, behind x86-64, Power ISA, and SPARC. History Development: 1989–2000 In 1989, HP began to become concerned that reduced instruction set computing (RISC) archite ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Hazard (computer Architecture)

In the domain of central processing unit (CPU) design, hazards are problems with the instruction pipeline in CPU microarchitectures when the next instruction cannot execute in the following clock cycle, and can potentially lead to incorrect computation results. Three common types of hazards are data hazards, structural hazards, and control hazards (branching hazards). There are several methods used to deal with hazards, including pipeline stalls/pipeline bubbling, operand forwarding, and in the case of out-of-order execution, the scoreboarding method and the Tomasulo algorithm. Background Instructions in a pipelined processor are performed in several stages, so that at any given time several instructions are being processed in the various stages of the pipeline, such as fetch and execute. There are many different instruction pipeline microarchitectures, and instructions may be executed out-of-order. A hazard occurs when two or more of these simultaneous (possibly out of or ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Memory Management Unit

A memory management unit (MMU), sometimes called paged memory management unit (PMMU), is a computer hardware unit having all memory references passed through itself, primarily performing the translation of virtual memory addresses to physical addresses. An MMU effectively performs virtual memory management, handling at the same time memory protection, cache control, bus arbitration and, in simpler computer architectures (especially 8-bit systems), bank switching. Overview Modern MMUs typically divide the virtual address space (the range of addresses used by the processor) into pages, each having a size which is a power of 2, usually a few kilobytes, but they may be much larger. The bottom bits of the address (the offset within a page) are left unchanged. The upper address bits are the virtual page numbers. Page table entries Most MMUs use an in-memory table of items called a "page table", containing one "page table entry" (PTE) per page, to map virtual page numbers to ph ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

System-on-a-chip

A system on a chip or system-on-chip (SoC ; pl. ''SoCs'' ) is an integrated circuit that integrates most or all components of a computer or other electronic system. These components almost always include a central processing unit (CPU), memory interfaces, on-chip input/output devices, input/output interfaces, and secondary storage interfaces, often alongside other components such as radio modems and a graphics processing unit (GPU) – all on a single substrate or microchip. It may contain digital, analog, mixed-signal, and often radio frequency signal processing functions (otherwise it is considered only an application processor). Higher-performance SoCs are often paired with dedicated and physically separate memory and secondary storage (such as LPDDR and eUFS or eMMC, respectively) chips, that may be layered on top of the SoC in what's known as a package on package (PoP) configuration, or be placed close to the SoC. Additionally, SoCs may use separate wireless modems. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Trace Scheduling

Trace scheduling is an optimization technique developed by Josh Fisher used in compilers for computer programs. A compiler often can, by rearranging its generated machine instructions for faster execution, improve program performance. It increases ILP (Instruction Level Parallelism) along the important execution path by statically predicting frequent execution path. Trace scheduling is one of many known techniques for doing so. A trace is a sequence of instructions, including branches but not including loops, that is executed for some input data. Trace scheduling uses a basic block scheduling method to schedule the instructions in each entire trace, beginning with the trace with the highest frequency. It then adds compensation code at the entry and exit of each trace to compensate for any effects that out-of-order execution may have had. This can result in large increases in code sizes and poor or erratic performance if program's behavior varies significantly with the input. Tra ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Open64

Open64 is a free, open-source, optimizing compiler for the Itanium and x86-64 microprocessor architectures. It derives from the SGI compilers for the MIPS R10000 processor, called ''MIPSPro''. It was initially released in 2000 as GNU GPL software under the name Pro64. The following year, University of Delaware adopted the project and renamed the compiler to Open64. It now mostly serves as a research platform for compiler and computer architecture research groups. Open64 supports Fortran 77/95 and C/C++, as well as the shared memory programming model OpenMP. It can conduct high-quality interprocedural analysis, data-flow analysis, data dependence analysis, and array region analysis. Development has ceased, although other projects can use the project's source. The infrastructure Its major components are the frontend for C/C++ (using GCC) and Fortran 77/90 (using the CraySoft front-end and libraries), Interprocedural analysis (IPA), loop nest optimizer (LNO), global optimizer ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GNU Compiler Collection

The GNU Compiler Collection (GCC) is an optimizing compiler produced by the GNU Project supporting various programming languages, hardware architectures and operating systems. The Free Software Foundation (FSF) distributes GCC as free software under the GNU General Public License (GNU GPL). GCC is a key component of the GNU toolchain and the standard compiler for most projects related to GNU and the Linux kernel. With roughly 15 million lines of code in 2019, GCC is one of the biggest free programs in existence. It has played an important role in the growth of free software, as both a tool and an example. When it was first released in 1987 by Richard Stallman, GCC 1.0 was named the GNU C Compiler since it only handled the C programming language. It was extended to compile C++ in December of that year. Front ends were later developed for Objective-C, Objective-C++, Fortran, Ada, D and Go, among others. The OpenMP and OpenACC specifications are also supported in the C and C ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |