|

RISC Architectures

In computer engineering, a reduced instruction set computer (RISC) is a computer designed to simplify the individual instructions given to the computer to accomplish tasks. Compared to the instructions given to a complex instruction set computer (CISC), a RISC computer might require more instructions (more code) in order to accomplish a task because the individual instructions are written in simpler code. The goal is to offset the need to process more instructions by increasing the speed of each instruction, in particular by implementing an instruction pipeline, which may be simpler given simpler instructions. The key operational concept of the RISC computer is that each instruction performs only one function (e.g. copy a value from memory to a register). The RISC computer usually has many (16 or 32) high-speed, general-purpose registers with a load/store architecture in which the code for the register-register instructions (for performing arithmetic and tests) are separate fr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

KL Sun UltraSparc

KL, kL, kl, or kl. may refer to: Businesses and organizations * KLM, a Dutch airline (IATA airline designator KL) * Koninklijke Landmacht, the Royal Netherlands Army * Kvenna Listin ("Women's List"), a political party in Iceland * KL FM, a Malay language radio station Places * Kaiserslautern, Germany (license plate code KL) * Kerala, India (ISO 3166-2:IN subcode KL) * Kirkland Lake, Ontario, Canada * Kowloon, Hong Kong * Kuala Lumpur, Malaysia Science, technology, and mathematics * KL engine, version of the Mazda K engine * Klepton (kl.), a type of species in zoology * Kiloliter (kL), a unit of volume * Kullback–Leibler divergence in mathematics * KL (gene), a gene which encodes the klotho enzyme in humans Other uses * Jeep Cherokee (KL) * Kalaallisut language (ISO 639 alpha-2 language code "kl") * Kl (digraph), used in the Zulu language to write /kʟ̥ʼ/ or /kxʼ/ * Konzentrationslager, or concentration camp, abbreviated KZ or KL * ''KL – A History of the Nazi Concentratio ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Laser Printer

Laser printing is an electrostatic digital printing process. It produces high-quality text and graphics (and moderate-quality photographs) by repeatedly passing a laser beam back and forth over a negatively-charged cylinder called a "drum" to define a differentially-charged image. The drum then selectively collects electrically-charged powdered ink (toner), and transfers the image to paper, which is then heated to permanently fuse the text, imagery, or both, to the paper. As with digital photocopiers, laser printers employ a xerographic printing process. Laser printing differs from traditional xerography as implemented in analog photocopiers in that in the latter, the image is formed by reflecting light off an existing document onto the exposed drum. Invented at Xerox PARC in the 1970s, laser printers were introduced for the office and then home markets in subsequent years by IBM, Canon, Xerox, Apple, Hewlett-Packard and many others. Over the decades, quality and speed have in ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

RISC-V

RISC-V (pronounced "risk-five" where five refers to the number of generations of RISC architecture that were developed at the University of California, Berkeley since 1981) is an open standard instruction set architecture (ISA) based on established RISC principles. Unlike most other ISA designs, RISC-V is provided under open source licenses that do not require fees to use. A number of companies are offering or have announced RISC-V hardware, open source operating systems with RISC-V support are available, and the instruction set is supported in several popular software toolchains. As a RISC architecture, the RISC-V ISA is a load–store architecture. Its floating-point instructions use IEEE 754 floating-point. Notable features of the RISC-V ISA include instruction bit field locations chosen to simplify the use of multiplexers in a CPU, a design that is architecturally neutral, and most-significant bits of immediate values placed at a fixed location to speed sign extension. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PA-RISC

PA-RISC is an instruction set architecture (ISA) developed by Hewlett-Packard. As the name implies, it is a reduced instruction set computer (RISC) architecture, where the PA stands for Precision Architecture. The design is also referred to as HP/PA for Hewlett Packard Precision Architecture. The architecture was introduced on 26 February 1986, when the HP 3000 Series 930 and HP 9000 Model 840 computers were launched featuring the first implementation, the TS1. PA-RISC has been succeeded by the Itanium (originally IA-64) ISA, jointly developed by HP and Intel. HP stopped selling PA-RISC-based HP 9000 systems at the end of 2008 but supported servers running PA-RISC chips until 2013. History In the late 1980s, HP was building four series of computers, all based on CISC CPUs. One line was the IBM PC compatible Intel i286-based Vectra Series, started in 1986. All others were non-Intel systems. One of them was the HP Series 300 of Motorola 68000-based workstations, another Serie ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Motorola 88000

The 88000 (m88k for short) is a RISC instruction set architecture developed by Motorola during the 1980s. The MC88100 arrived on the market in 1988, some two years after the competing SPARC and MIPS. Due to the late start and extensive delays releasing the second-generation MC88110, the m88k achieved very limited success outside of the MVME platform and embedded controller environments. When Motorola joined the AIM alliance in 1991 to develop the PowerPC, further development of the 88000 ended. History Background Motorola entered the 1980s in a position of strength; their recently-introduced Motorola 68000 easily outperformed any other microprocessor on the market, and its 32-bit architecture was naturally suited to the emerging Unix workstation market. Intel was not moving aggressively into the 32-bit space, and the companies that did, notably National Semiconductor, botched their releases and left Motorola in control of everything that was not Intel. At the time, Intel held a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

LoongArch

Loongson () is the name of a family of general-purpose, MIPS architecture-compatible microprocessors, as well as the name of the Chinese fabless company (Loongson Technology) that develops them. The processors are alternately called Godson processors, which are described as its academic name. History The ''Godson'' processors, based on MIPS architecture, were initially developed at the ''Institute of Computing Technology'' (ICT), Chinese Academy of Sciences (CAS). The chief architect was Professor . The development of the first Loongson chip was started in 2001. The aim of the Godson project was to develop "high performance general-purpose microprocessors in China", and to become technologically self-sufficient as part of the Made in China 2025 plan. The development was supported by funding via the 10th and 11th Five-Year Plans. In 2010 the company was commercialised as a separate entity, and in April 2010 ''Loongson Technology Corporation Limited'' was formally established ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

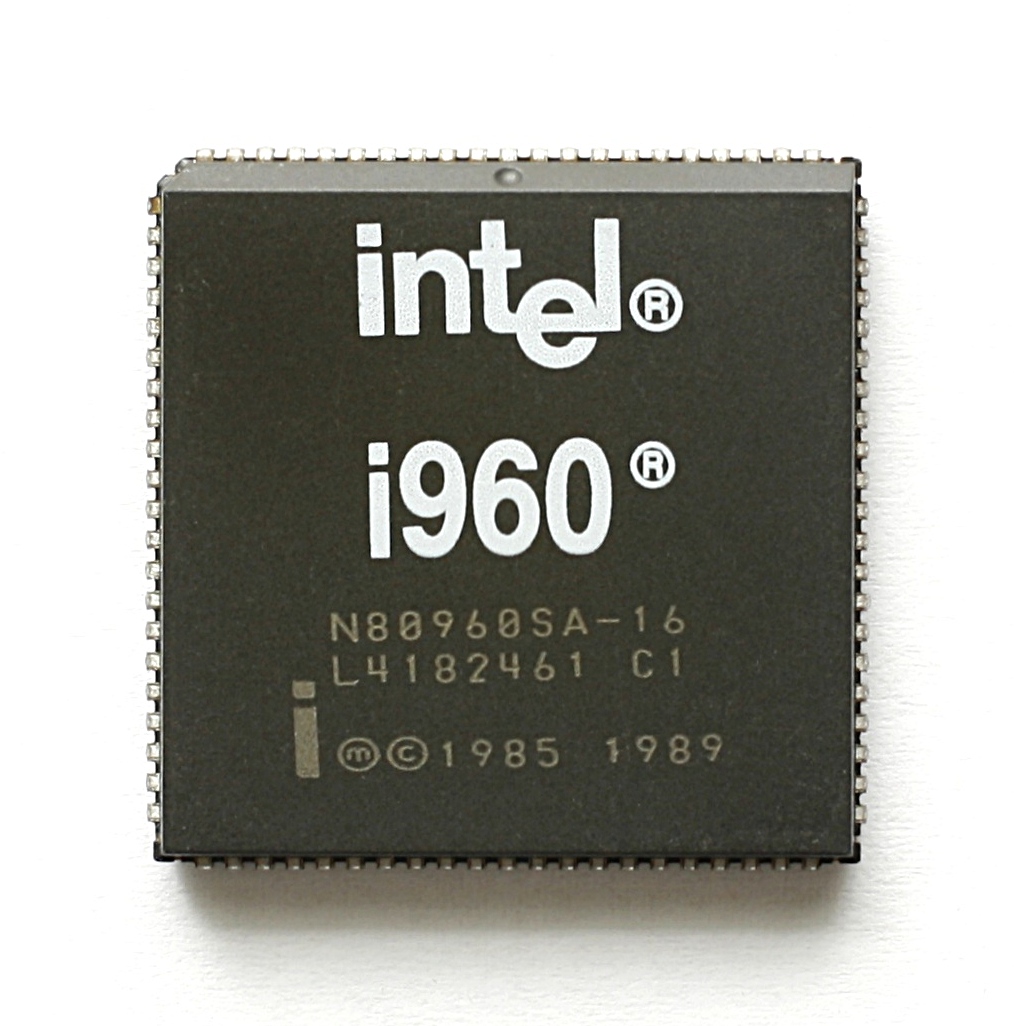

Intel I960

Intel's i960 (or 80960) was a RISC-based microprocessor design that became popular during the early 1990s as an embedded microcontroller. It became a best-selling CPU in that segment, along with the competing AMD 29000. In spite of its success, Intel stopped marketing the i960 in the late 1990s, as a result of a settlement with DEC whereby Intel received the rights to produce the StrongARM CPU. The processor continues to be used for a few military applications. Origin The i960 design was begun in response to the failure of Intel's iAPX 432 design of the early 1980s. The iAPX 432 was intended to directly support high-level languages that supported tagged, protected, garbage-collected memory—such as Ada and Lisp—in hardware. Because of its instruction-set complexity, its multi-chip implementation, and design flaws, the iAPX 432 was very slow in comparison to other processors of its time. In 1984, Intel and Siemens started a joint project, ultimately called BiiN, to cr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel I860

The Intel i860 (also known as 80860) is a RISC microprocessor design introduced by Intel in 1989. It is one of Intel's first attempts at an entirely new, high-end instruction set architecture since the failed Intel iAPX 432 from the beginning of the 1980s. It was the world's first million-transistor chip. It was released with considerable fanfare, slightly obscuring the earlier Intel i960, which was successful in some niches of embedded systems, and which many considered to be a better design. The i860 never achieved commercial success and the project was terminated in the mid-1990s. Implementations The first implementation of the i860 architecture is the i860 XR microprocessor (code-named N10), which ran at 25, 33, or 40 MHz. The second-generation i860 XP microprocessor (code named N11) added 4 Mbyte pages, larger on-chip caches, second level cache support, faster buses, and hardware support for bus snooping, for cache consistency in multiprocessor systems. A process ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Blackfin

The Blackfin is a family of 16-/32-bit microprocessors developed, manufactured and marketed by Analog Devices. The processors have built-in, fixed-point digital signal processor (DSP) functionality supplied by 16-bit multiply–accumulates (MACs), accompanied on-chip by a microcontroller. It was designed for a unified low-power processor architecture that can run operating systems while simultaneously handling complex numeric tasks such as real-time H.264 video encoding. Architecture details Blackfin processors use a 32-bit RISC microcontroller programming model on a SIMD architecture, which was co-developed by Intel and Analog Devices, as MSA (Micro Signal Architecture). The architecture was announced in December 2000, and first demonstrated at the Embedded Systems Conference in June, 2001. It incorporates aspects of ADI's older SHARC architecture and Intel's XScale architecture into a single core, combining digital signal processing (DSP) and microcontroller functionality ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Atmel AVR

AVR is a family of microcontrollers developed since 1996 by Atmel, acquired by Microchip Technology in 2016. These are modified Harvard architecture 8-bit Reduced instruction set computer, RISC single-chip microcontrollers. AVR was one of the first microcontroller families to use on-chip flash memory for program storage, as opposed to Programmable read-only memory, one-time programmable ROM, EPROM, or EEPROM used by other microcontrollers at the time. AVR microcontrollers find many applications as embedded systems. They are especially common in hobbyist and educational embedded applications, popularized by their inclusion in many of the Arduino line of open hardware development boards. History The AVR architecture was conceived by two students at the Norwegian Institute of Technology (NTH), Alf-Egil Bogen and Vegard Wollan.Archived aGhostarchiveand thWayback Machine Atmel says that the name AVR is not an acronym and does not stand for anything in particular. The creators of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Architecture

ARM (stylised in lowercase as arm, formerly an acronym for Advanced RISC Machines and originally Acorn RISC Machine) is a family of reduced instruction set computer (RISC) instruction set architectures for computer processors, configured for various environments. Arm Ltd. develops the architectures and licenses them to other companies, who design their own products that implement one or more of those architectures, including system on a chip (SoC) and system on module (SOM) designs, that incorporate different components such as memory, interfaces, and radios. It also designs cores that implement these instruction set architectures and licenses these designs to many companies that incorporate those core designs into their own products. There have been several generations of the ARM design. The original ARM1 used a 32-bit internal structure but had a 26-bit address space that limited it to 64 MB of main memory. This limitation was removed in the ARMv3 series, which ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD Am29000

The AMD Am29000, commonly shortened to 29k, is a family of 32-bit RISC microprocessors and microcontrollers developed and fabricated by Advanced Micro Devices (AMD). Based on the seminal Berkeley RISC, the 29k added a number of significant improvements. They were, for a time, the most popular RISC chips on the market, widely used in laser printers from a variety of manufacturers. Developed since 1984-1985, announced in March 1987 and released in May 1988, the initial Am29000 was followed by several versions, ending with the Am29040 in 1995. The 29050 was notable for being early to feature a floating point unit capable of executing one multiply–add operation per cycle. AMD was designing a superscalar version until late 1995, when AMD dropped the development of the 29k because the design team was transferred to support the PC (x86) side of the business. What remained of AMD's embedded business was realigned towards the embedded 186 family of 80186 derivatives. By then the major ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

_(cropped)_ADSP-BF526_BBCZ-4A.jpg)