|

Romley

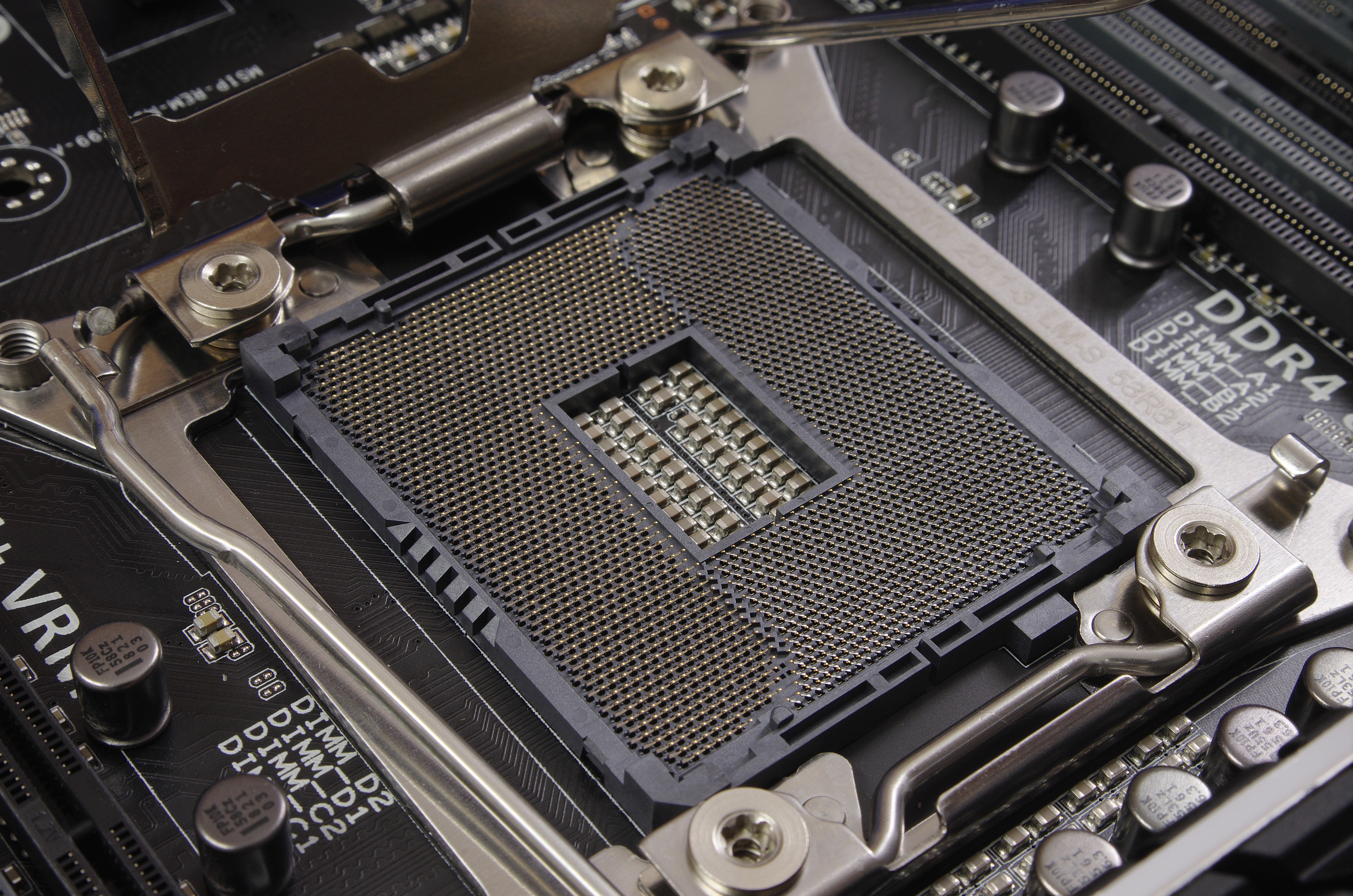

LGA 2011, also called ''Socket R'', is a CPU socket by Intel released on November 14, 2011. It launched along with LGA 1356 to replace its predecessor, LGA 1366 (Socket B) and LGA 1567. While LGA 1356 was designed for dual-processor or low-end servers, LGA 2011 was designed for high-end desktops and high-performance servers. The socket has 2011 protruding pins that touch contact points on the underside of the processor. The LGA 2011 socket uses QPI to connect the CPU to additional CPUs. DMI 2.0 is used to connect the processor to the PCH. The memory controller and 40 PCI Express (PCIe) lanes are integrated on the CPU. On a secondary processor an extra ×4 PCIe interface replaces the DMI interface. As with its predecessor LGA 1366, there is no provisioning for integrated graphics. This socket supports four DDR3 or DDR4 SDRAM memory channels with up to three unbuffered or registered DIMMs per channel, as well as up to 40 PCI Express 2.0 or 3.0 lanes. LGA ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

LGA 1356

LGA 1356, also called Socket B2, is an Intel microprocessor socket released in Q1 2012 with 1356 Land Grid Array pins. It launched alongside LGA 2011 to replace its predecessor, LGA 1366 (Socket B) and LGA 1567. It's compatible with Intel Sandy Bridge-EN (also known as Romley-EN) and Ivy Bridge-EN microprocessors. Description LGA 1356 has 1356 protruding pins to make contact with the pads on the processor. Processors of LGA 1356 and LGA 1366 sockets are not compatible with each other since they have different socket notches. While LGA 2011 was designed for high-end desktops and high-performance servers, LGA 1356 was designed for the dual-processor and low-end segment of the server market. It supports 64-bit wide DDR3 triple channel memory, and equipped with 1 Intel QPI connection and 24 PCI Express lanes. Meanwhile LGA 2011 supports quad channel memory, 2 QPI connections and 40 PCIe lanes. Socket LGA 1155, desktop socket of the same generation supports dual channel memory. E ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel QuickPath Interconnect

The Intel QuickPath Interconnect (QPI) is a point-to-point microprocessor, processor electrical connection, interconnect developed by Intel which replaced the front-side bus (FSB) in Xeon, Itanium, and certain desktop platforms starting in 2008. It increased the scalability and available bandwidth. Prior to the name's announcement, Intel referred to it as Common System Interface (CSI). Earlier incarnations were known as Yet Another Protocol (YAP) and YAP+. QPI 1.1 is a significantly revamped version introduced with Sandy Bridge-EP (Romley platform). QPI was replaced by Intel Ultra Path Interconnect (UPI) in Skylake (microarchitecture), Skylake-SP Xeon processors based on LGA 3647 socket. Background Although sometimes called a "bus", QPI is a point-to-point interconnect. It was designed to compete with HyperTransport that had been used by Advanced Micro Devices (AMD) since around 2003. Intel developed QPI at its Massachusetts Microprocessor Design Center (MMDC) by members of what ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Platform Controller Hub

The Platform Controller Hub (PCH) is a family of Intel's single-chip chipsets, first introduced in 2009. It is the successor to the Intel Hub Architecture, which used two chips - a Northbridge (computing), northbridge and Southbridge (computing), southbridge, and first appeared in the Intel 5 Series. The PCH controls certain data paths and support functions used in conjunction with Intel CPUs. These include clocking (the system clock), Flexible Display Interface (FDI) and Direct Media Interface (DMI), although FDI is used only when the chipset is required to support a processor with integrated graphics. As such, I/O functions are reassigned between this new central hub and the CPU compared to the previous architecture: some northbridge functions, the memory controller and PCI Express, PCIe lanes, were integrated into the CPU while the PCH took over the remaining functions in addition to the traditional roles of the southbridge. AMD has its equivalent for the PCH, known simply as a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Flip-chip

Flip chip, also known as controlled collapse chip connection or its abbreviation, C4, is a method for interconnecting dies such as semiconductor devices, IC chips, integrated passive devices and microelectromechanical systems (MEMS), to external circuitry with solder bumps that have been deposited onto the chip pads. The technique was developed by General Electric's Light Military Electronics Department, Utica, New York. The solder bumps are deposited on the chip pads on the top side of the wafer during the final wafer processing step. In order to mount the chip to external circuitry (e.g., a circuit board or another chip or wafer), it is flipped over so that its top side faces down, and aligned so that its pads align with matching pads on the external circuit, and then the solder is reflowed to complete the interconnect. This is in contrast to wire bonding, in which the chip is mounted upright and fine wires are welded onto the chip pads and lead frame contacts to interconnect ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Haswell-EP

Xeon ( ) is a brand of x86 microprocessors designed, manufactured, and marketed by Intel, targeted at the non-consumer workstation, server, and embedded system markets. It was introduced in June 1998. Xeon processors are based on the same architecture as regular desktop-grade CPUs, but have advanced features such as support for ECC memory, higher core counts, more PCI Express lanes, support for larger amounts of RAM, larger cache memory and extra provision for enterprise-grade reliability, availability and serviceability (RAS) features responsible for handling hardware exceptions through the Machine Check Architecture. They are often capable of safely continuing execution where a normal processor cannot due to these extra RAS features, depending on the type and severity of the machine-check exception (MCE). Some also support multi-socket systems with two, four, or eight sockets through use of the Ultra Path Interconnect (UPI) bus. Overview The ''Xeon'' brand has been maint ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Haswell-E

Haswell is the List of Intel codenames, codename for a Central processing unit, processor microarchitecture developed by Intel as the "fourth-generation core" successor to the Ivy Bridge (microarchitecture), Ivy Bridge (which is a die shrink/Tick–tock model, tick of the Sandy Bridge, Sandy Bridge microarchitecture). Intel officially announced CPUs based on this microarchitecture on June 4, 2013, at Computex Taipei 2013, while a working Haswell chip was demonstrated at the 2011 Intel Developer Forum. With Haswell, which uses a 22 nanometer, 22 nm process, Intel also introduced low-power processors designed for convertible or "hybrid" ultrabooks, designated by the "U" suffix. Haswell CPUs are used in conjunction with the Intel 8 Series chipsets, Intel 9 Series chipsets, and Intel Xeon chipsets#Haswell-based Xeon chipsets, Intel C220 series chipsets. At least one Haswell-based processor is still being sold as of 2022, the Pentium G3420. Design The Haswell archite ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Xeon E7 V3

Xeon ( ) is a brand of x86 microprocessors designed, manufactured, and marketed by Intel, targeted at the non-consumer workstation, server, and embedded system markets. It was introduced in June 1998. Xeon processors are based on the same architecture as regular desktop-grade CPUs, but have advanced features such as support for ECC memory, higher core counts, more PCI Express lanes, support for larger amounts of RAM, larger cache memory and extra provision for enterprise-grade reliability, availability and serviceability (RAS) features responsible for handling hardware exceptions through the Machine Check Architecture. They are often capable of safely continuing execution where a normal processor cannot due to these extra RAS features, depending on the type and severity of the machine-check exception (MCE). Some also support multi-socket systems with two, four, or eight sockets through use of the Ultra Path Interconnect (UPI) bus. Overview The ''Xeon'' brand has been maint ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Xeon E7 V2

Xeon ( ) is a brand of x86 microprocessors designed, manufactured, and marketed by Intel, targeted at the non-consumer workstation, server, and embedded system markets. It was introduced in June 1998. Xeon processors are based on the same architecture as regular desktop-grade CPUs, but have advanced features such as support for ECC memory, higher core counts, more PCI Express lanes, support for larger amounts of RAM, larger cache memory and extra provision for enterprise-grade reliability, availability and serviceability (RAS) features responsible for handling hardware exceptions through the Machine Check Architecture. They are often capable of safely continuing execution where a normal processor cannot due to these extra RAS features, depending on the type and severity of the machine-check exception (MCE). Some also support multi-socket systems with two, four, or eight sockets through use of the Ultra Path Interconnect (UPI) bus. Overview The ''Xeon'' brand has been main ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Windows Server 2003

Windows Server 2003 is the sixth version of Windows Server operating system produced by Microsoft. It is part of the Windows NT family of operating systems and was released to manufacturing on March 28, 2003 and generally available on April 24, 2003. Windows Server 2003 is the successor to the Server editions of Windows 2000 and the predecessor to Windows Server 2008. An updated version, Windows Server 2003 R2, was released to manufacturing on December 6, 2005. Windows Server 2003 is based on the consumer operating system, Windows XP. Windows Server 2003's kernel has also been used in Windows XP 64-bit Edition and Windows XP Professional x64 Edition, and was the starting point for the development of Windows Vista. Overview Windows Server 2003 is the follow-up to Windows 2000 Server, incorporating compatibility and other features from Windows XP. Unlike Windows 2000, Windows Server 2003's default installation has none of the server components enabled, to reduce the attack surface ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Windows XP

Windows XP is a major release of Microsoft's Windows NT operating system. It was released to manufacturing on August 24, 2001, and later to retail on October 25, 2001. It is a direct upgrade to its predecessors, Windows 2000 for high-end and business users and Windows Me for home users, available for any devices running Windows NT 4.0, Windows 98, Windows 2000 and Windows Me that meet the new Windows XP system requirements. Development of Windows XP began in the late 1990s under the codename "Neptune", built on the Windows NT kernel explicitly intended for mainstream consumer use. An updated version of Windows 2000 was also initially planned for the business market. However, in January 2000, both projects were scrapped in favor of a single OS codenamed "Whistler", which would serve as a single platform for both consumer and business markets. As a result, Windows XP is the first consumer edition of Windows not based on the Windows 95 kernel and MS-DOS. Windows XP removed suppo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ivy Bridge (microarchitecture)

Ivy Bridge is the codename for Intel's 22 nm microarchitecture used in the third generation of the Intel Core processors (Core i7, i5, i3). Ivy Bridge is a die shrink to 22 nm process based on FinFET ("3D") Tri-Gate transistors, from the former generation's 32 nm Sandy Bridge microarchitecture—also known as tick–tock model. The name is also applied more broadly to the Xeon and Core i7 Ivy Bridge-E series of processors released in 2013. Ivy Bridge processors are backward compatible with the Sandy Bridge platform, but such systems might require a firmware update (vendor specific). In 2011, Intel released the 7-series Panther Point chipsets with integrated USB 3.0 and SATA 3.0 to complement Ivy Bridge. Volume production of Ivy Bridge chips began in the third quarter of 2011. Quad-core and dual-core-mobile models launched on April 29, 2012 and May 31, 2012 respectively. Core i3 desktop processors, as well as the first 22 nm Pentium, wer ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PCI Express 3

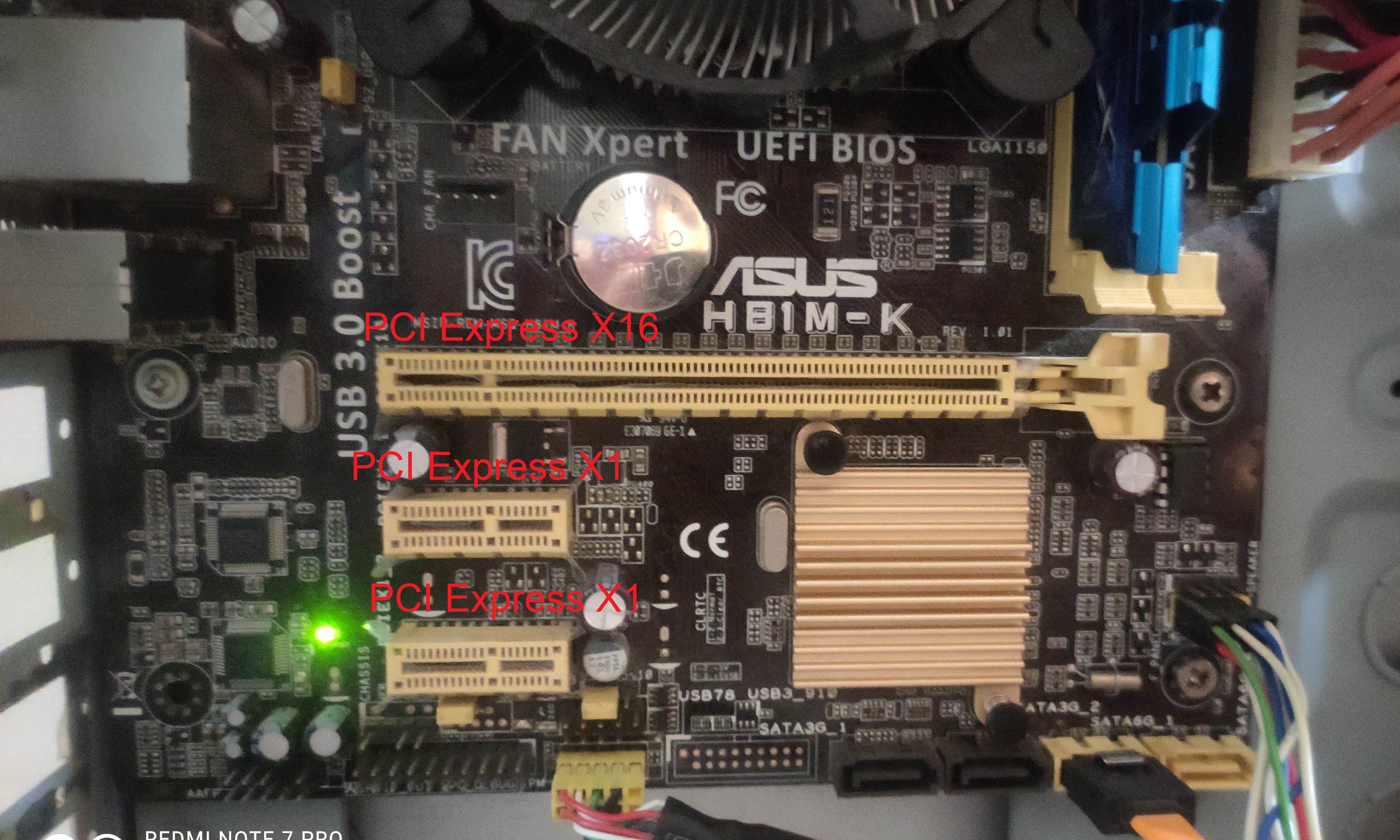

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common motherboard interface for personal computers' graphics cards, hard disk drive host adapters, SSDs, Wi-Fi and Ethernet hardware connections. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism (Advanced Error Reporting, AER), and native hot-swap functionality. More recent revisions of the PCIe standard provide hardware support for I/O virtualization. The PCI Express electrical interface is measured by the number of simultaneous lanes. (A lane is a single send/receive line of data. The analogy is a highway with traffic in both directions. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |