|

RAM Parity

RAM parity checking is the storing of a redundant parity bit representing the parity (odd or even) of a small amount of computer data (typically one byte) stored in random-access memory, and the subsequent comparison of the stored and the computed parity to detect whether a data error has occurred. The parity bit was originally stored in additional individual memory chips; with the introduction of plug-in DIMM, SIMM, etc. modules, they became available in non-parity and parity (with an extra bit per byte, storing 9 bits for every 8 bits of actual data) versions. History Early computers sometimes required the use of parity RAM, and parity-checking could not be disabled. A parity error typically caused the machine to halt, with loss of unsaved data; this is usually a better option than saving corrupt data. ''Logic parity RAM'', also known as fake parity RAM, is non-parity RAM that can be used in computers that require parity RAM. Logic parity RAM recalculates an always-valid par ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Redundancy (engineering)

In engineering and systems theory, redundancy is the intentional duplication of critical components or functions of a system with the goal of increasing reliability of the system, usually in the form of a backup or fail-safe, or to improve actual system performance, such as in the case of GNSS receivers, or multi-threaded computer processing. In many safety-critical systems, such as fly-by-wire and hydraulic systems in aircraft, some parts of the control system may be triplicated, which is formally termed triple modular redundancy (TMR). An error in one component may then be out-voted by the other two. In a triply redundant system, the system has three sub components, all three of which must fail before the system fails. Since each one rarely fails, and the sub components are designed to preclude common failure modes (which can then be modelled as independent failure), the probability of all three failing is calculated to be extraordinarily small; it is often outweighed ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Go/no Go

A go/no-go test is a two-step verification process that uses two boundary conditions, or a binary classification. The test is passed only when the ''go'' condition has been met and also the ''no-go'' condition has failed. The test gives no information as to the degree of conformance to, or deviation from the boundary conditions. These tests can be used for statistical process control purposes. There are specific SPC tools that use parameter based measurements (e.g., P-charts) for determining the stability of a process. It has uses in engineering, psychology, military, and manufacturing. For example, a rocket launch status check involves a go/no-go test. Uses Engineering In engineering the test is traditionally used only to check noncritical parameters where the manufacturing process is believed to be stable and well controlled, and the tolerances are wide compared to the distribution of the parameter. For example, the preceding launch status checks before a Space Shuttle l ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Mitsubishi

The is a group of autonomous Japanese multinational companies in a variety of industries. Founded by Yatarō Iwasaki in 1870, the Mitsubishi Group traces its origins to the Mitsubishi zaibatsu, a unified company that existed from 1870 to 1946. The company, along with other major zaibatsu, was disbanded during the occupation of Japan following World War II by the order of the Allies. Despite the dissolution, the former constituent companies continue to share the Mitsubishi brand and trademark. While the group of companies engages in limited business cooperation, most notably through monthly "Friday Conference" executive meetings, they remain formally independent and are not under common control. The three main entities ('' gosanke'') are Mitsubishi UFJ Financial Group (the largest bank in Japan), Mitsubishi Corporation (a general trading company), and Mitsubishi Heavy Industries (a diversified manufacturing company). A 2020 estimate concluded that all the Mitsubishi compani ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Toshiba

is a Japanese multinational electronics company headquartered in Minato, Tokyo. Its diversified products and services include power, industrial and social infrastructure systems, elevators and escalators, electronic components, semiconductors, hard disk drives, printers, batteries, lighting, as well as IT solutions such as quantum cryptography. It was formerly also one of the biggest manufacturers of personal computers, consumer electronics, home appliances, and medical equipment. The Toshiba name is derived from its former name, Tokyo Shibaura Denki K.K. which in turn was a 1939 merger between Shibaura Seisaku-sho (founded in 1875) and Tokyo Denki (founded in 1890). The company name was officially changed to Toshiba Corporation in 1978. A technology company with a long history and sprawling businesses, Toshiba is a household name in Japan and has long been viewed as a symbol of the country's technological prowess post-World War II. As a semiconductor company and the i ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Wang Laboratories

Wang Laboratories, Inc., was an American computer company founded in 1951 by An Wang and G. Y. Chu. The company was successively headquartered in Cambridge, Massachusetts (1954–1963), Tewksbury, Massachusetts (1963–1976), Lowell, Massachusetts (1976–1995), and finally Billerica, Massachusetts. At its peak in the 1980s, Wang Laboratories had annual revenues of US$3 billion and employed over 33,000 people. It was one of the leading companies during the time of the Massachusetts Miracle. The company was directed by An Wang, who was described as an "indispensable leader" and played a personal role in setting business and product strategy until his death in 1990. The company went through transitions between different product lines, beginning with typesetters, calculators, and word processors, then adding computers, copiers, and laser printers. Wang Laboratories filed for bankruptcy protection in August 1992. After emerging from bankruptcy, the company changed its name to Wa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Error Correction

In information theory and coding theory with applications in computer science and telecommunications, error detection and correction (EDAC) or error control are techniques that enable reliable delivery of digital data over unreliable communication channels. Many communication channels are subject to channel noise, and thus errors may be introduced during transmission from the source to a receiver. Error detection techniques allow detecting such errors, while error correction enables reconstruction of the original data in many cases. Definitions ''Error detection'' is the detection of errors caused by noise or other impairments during transmission from the transmitter to the receiver. ''Error correction'' is the detection of errors and reconstruction of the original, error-free data. History In classical antiquity, copyists of the Hebrew Bible were paid for their work according to the number of stichs (lines of verse). As the prose books of the Bible were hardly ever w ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

DDR SDRAM

Double Data Rate Synchronous Dynamic Random-Access Memory (DDR SDRAM) is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) class of memory integrated circuits used in computers. DDR SDRAM, also retroactively called DDR1 SDRAM, has been superseded by DDR2 SDRAM, DDR3 SDRAM, DDR4 SDRAM and DDR5 SDRAM. None of its successors are forward or backward compatible with DDR1 SDRAM, meaning DDR2, DDR3, DDR4 and DDR5 memory modules will not work on DDR1-equipped motherboards, and vice versa. Compared to single data rate ( SDR) SDRAM, the DDR SDRAM interface makes higher transfer rates possible through more strict control of the timing of the electrical data and clock signals. Implementations often have to use schemes such as phase-locked loops and self-calibration to reach the required timing accuracy. The interface uses double pumping (transferring data on both the rising and falling edges of the clock signal) to double data bus bandwidth without a cor ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

SDRAM

Synchronous dynamic random-access memory (synchronous dynamic RAM or SDRAM) is any DRAM where the operation of its external pin interface is coordinated by an externally supplied clock signal. DRAM integrated circuits (ICs) produced from the early 1970s to the early 1990s used an ''asynchronous'' interface, in which input control signals have a direct effect on internal functions delayed only by the trip across its semiconductor pathways. SDRAM has a ''synchronous'' interface, whereby changes on control inputs are recognised after a rising edge of its clock input. In SDRAM families standardized by JEDEC, the clock signal controls the stepping of an internal finite-state machine that responds to incoming commands. These commands can be pipelined to improve performance, with previously started operations completing while new commands are received. The memory is divided into several equally sized but independent sections called ''banks'', allowing the device to operate on a memor ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Parity Error

A parity bit, or check bit, is a bit added to a string of binary code. Parity bits are a simple form of error detecting code. Parity bits are generally applied to the smallest units of a communication protocol, typically 8-bit octets (bytes), although they can also be applied separately to an entire message string of bits. The parity bit ensures that the total number of 1-bits in the string is even or odd. Accordingly, there are two variants of parity bits: even parity bit and odd parity bit. In the case of even parity, for a given set of bits, the bits whose value is 1 are counted. If that count is odd, the parity bit value is set to 1, making the total count of occurrences of 1s in the whole set (including the parity bit) an even number. If the count of 1s in a given set of bits is already even, the parity bit's value is 0. In the case of odd parity, the coding is reversed. For a given set of bits, if the count of bits with a value of 1 is even, the parity bit value is set ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Dynamic Random-access Memory

Dynamics (from Greek language, Greek δυναμικός ''dynamikos'' "powerful", from δύναμις ''dynamis'' "power (other), power") or dynamic may refer to: Physics and engineering * Dynamics (mechanics), the study of forces and their effect on motion Brands and enterprises * Dynamic (record label), an Italian record label in Genoa Mathematics * Dynamical system, a concept describing a point's time dependency ** Topological dynamics, the study of dynamical systems from the viewpoint of general topology * Symbolic dynamics, a method to model dynamical systems Social science * Group dynamics, the study of social group processes especially * Population dynamics, in life sciences, the changes in the composition of a population * Psychodynamics, the study of psychological forces driving human behavior * Social dynamics, the ability of a society to react to changes * Spiral Dynamics, a social development theory Other uses * Dynamics (music), the softness or loudn ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

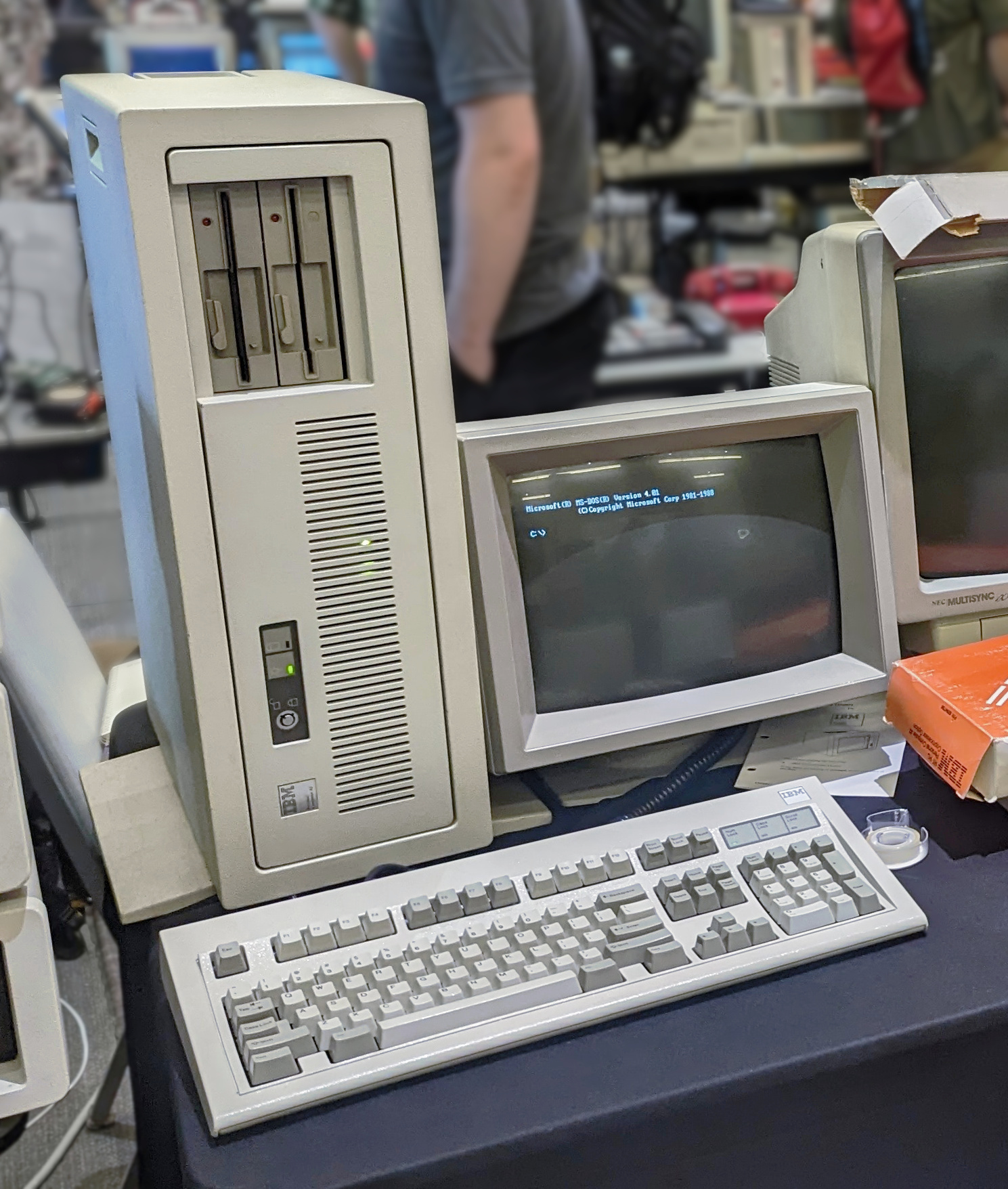

IBM PC/AT

The IBM Personal Computer AT (model 5170, abbreviated as IBM AT or PC/AT) was released in 1984 as the fourth model in the IBM Personal Computer line, following the IBM PC/XT and its IBM Portable PC variant. It was designed around the Intel 80286 microprocessor. Name IBM did not specify an expanded form of ''AT'' on the machine, press releases, brochures or documentation, but some sources expand the term as ''Advanced Technology'', including at least one internal IBM document. History IBM's 1984 introduction of the AT was seen as an unusual move for the company, which typically waited for competitors to release new products before producing its own models. At $4,000–6,000, it was only slightly more expensive than considerably slower IBM models. The announcement surprised rival executives, who admitted that matching IBM's prices would be difficult. No major competitor showed a comparable computer at COMDEX Las Vegas that year. Features The AT is IBM PC compatible, with t ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Google

Google LLC (, ) is an American multinational corporation and technology company focusing on online advertising, search engine technology, cloud computing, computer software, quantum computing, e-commerce, consumer electronics, and artificial intelligence (AI). It has been referred to as "the most powerful company in the world" by the BBC and is one of the world's List of most valuable brands, most valuable brands. Google's parent company, Alphabet Inc., is one of the five Big Tech companies alongside Amazon (company), Amazon, Apple Inc., Apple, Meta Platforms, Meta, and Microsoft. Google was founded on September 4, 1998, by American computer scientists Larry Page and Sergey Brin. Together, they own about 14% of its publicly listed shares and control 56% of its stockholder voting power through super-voting stock. The company went public company, public via an initial public offering (IPO) in 2004. In 2015, Google was reorganized as a wholly owned subsidiary of Alphabet Inc. Go ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |