|

R14000

The R10000, code-named "T5", is a RISC microprocessor implementation of the MIPS IV instruction set architecture (ISA) developed by MIPS Technologies, Inc. (MTI), then a division of Silicon Graphics, Inc. (SGI). The chief designers are Chris Rowen and Kenneth C. Yeager. The R10000 microarchitecture is known as ANDES, an abbreviation for Architecture with Non-sequential Dynamic Execution Scheduling. The R10000 largely replaces the R8000 in the high-end and the R4400 elsewhere. MTI was a fabless semiconductor company; the R10000 was fabricated by NEC and Toshiba. Previous fabricators of MIPS microprocessors such as Integrated Device Technology (IDT) and three others did not fabricate the R10000 as it was more expensive to do so than the R4000 and R4400. History The R10000 was introduced in January 1996 at clock frequencies of 175 MHz and 195 MHz. A 150 MHz version was introduced in the O2 product line in 1997, but discontinued shortly after due to customer pref ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Silicon Graphics

Silicon Graphics, Inc. (stylized as SiliconGraphics before 1999, later rebranded SGI, historically known as Silicon Graphics Computer Systems or SGCS) was an American high-performance computing manufacturer, producing computer hardware and software. Founded in Mountain View, California in November 1981 by Jim Clark, its initial market was 3D graphics computer workstations, but its products, strategies and market positions developed significantly over time. Early systems were based on the Geometry Engine that Clark and Marc Hannah had developed at Stanford University, and were derived from Clark's broader background in computer graphics. The Geometry Engine was the first very-large-scale integration (VLSI) implementation of a geometry pipeline, specialized hardware that accelerated the "inner-loop" geometric computations needed to display three-dimensional images. For much of its history, the company focused on 3D imaging and was a major supplier of both hardware and software ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SGI Origin 2000

The SGI Origin 2000 is a family of mid-range and high-end server computers developed and manufactured by Silicon Graphics (SGI). They were introduced in 1996 to succeed the SGI Challenge and POWER Challenge. At the time of introduction, these ran the IRIX operating system, originally version 6.4 and later, 6.5. A variant of the Origin 2000 with graphics capability is known as the Onyx2. An entry-level variant based on the same architecture but with a different hardware implementation is known as the Origin 200. The Origin 2000 was succeeded by the Origin 3000 in July 2000, and was discontinued on June 30, 2002. Models The family was announced on October 7, 1996. The project was code named ''Lego'', and also known as SN0, to indicate the first in a series of scalable node architectures, contrasting with previous symmetric multiprocessor architectures in the SGI Challenge series. The Origin 2100 is mostly the same as the other models except that it is not upgradeable to other ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

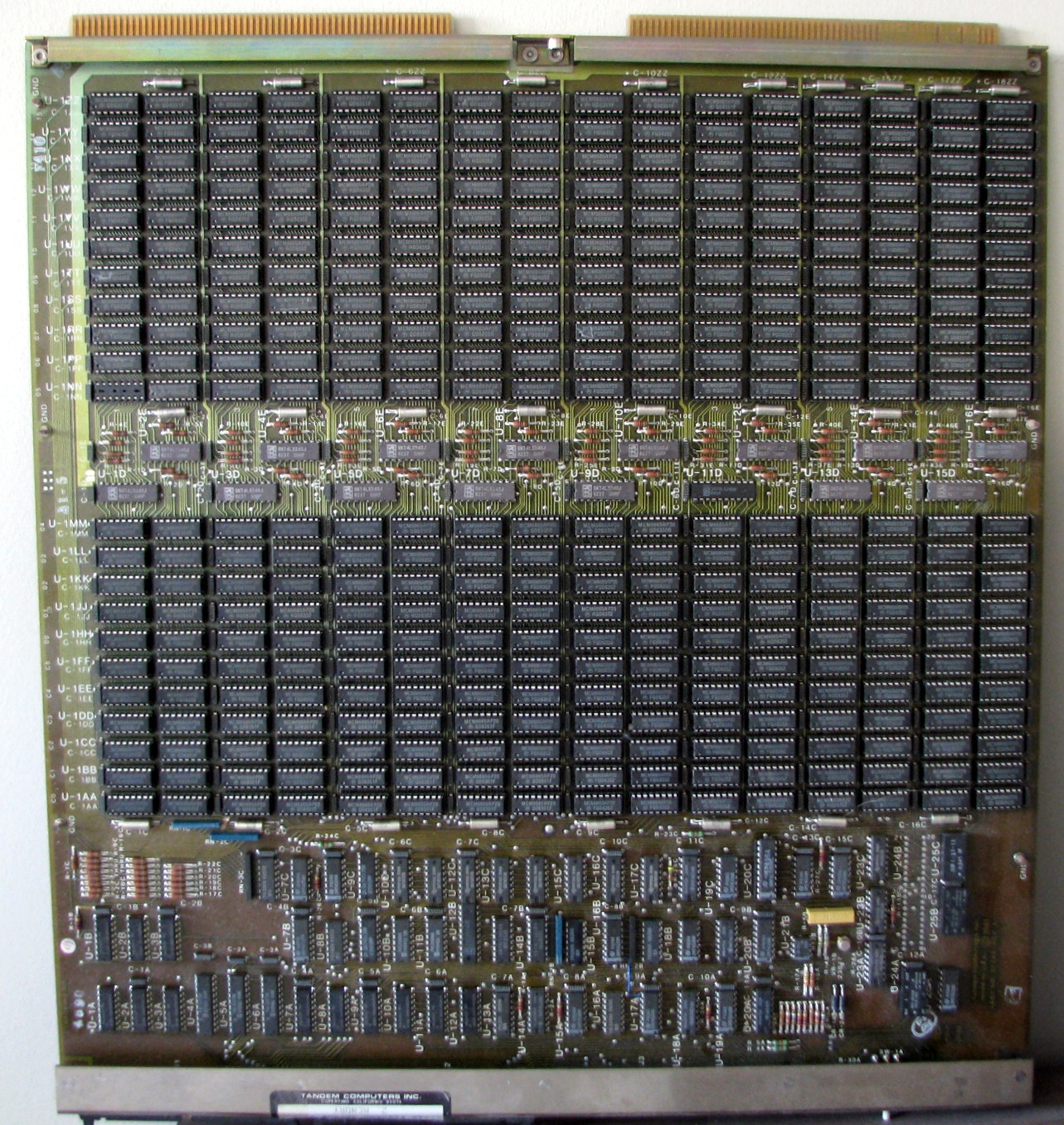

Tandem Computers

Tandem Computers, Inc. was the dominant manufacturer of fault-tolerant computer systems for Automated teller machine, ATM networks, banks, stock exchanges, telephone switching centers, and other similar commercial transaction processing applications requiring maximum uptime and zero data loss. The company was founded by Jimmy Treybig in 1974 in Cupertino, California. It remained independent until 1997, when it became a server division within Compaq. It is now a server division within Hewlett Packard Enterprise, following Hewlett-Packard's acquisition of Compaq and the split of Hewlett Packard into HP Inc. and Hewlett Packard Enterprise. Tandem's NonStop (server computers), NonStop systems use a number of independent identical processors and redundant storage devices and controllers to provide automatic high-speed "failover" in the case of a hardware or software failure. To contain the scope of failures and of corrupted data, these multi-computer systems have no shared central comp ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SGI Onyx2

SGI Onyx2, code name Kego, is a family of visualization systems developed and manufactured by SGI, introduced in 1996 to succeed the Onyx. The Onyx2's basic system architecture is based on the Origin 2000 servers, but with the inclusion of graphics hardware. In 2000, the Onyx2 was succeeded by the Onyx 3000, and it was discontinued on June 27, 2003. These systems run either IRIX 6.4 or 6.5. Models Microprocessor The Onyx2 uses the MIPS R10000 microprocessor clocked at 150, 175, 180 and 195 MHz, later increased to 250 MHz, courtesy of a process shrink from 0.35 to 0.25 micrometers. Later 300 and 400 MHz R12000, and 500 MHz R14000 CPUs were made available. Graphics subsystem At the time of their introduction, the Onyx2 could be configured with the Reality, InfiniteReality InfiniteReality refers to a 3D graphics hardware architecture and a family of graphics systems that implemented the aforementioned hardware architecture that was developed and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

KL NEC VR10000

KL, kL, kl, or kl. may refer to: Businesses and organizations * KLM, a Dutch airline (IATA airline designator KL) * Koninklijke Landmacht, the Royal Netherlands Army * Kvenna Listin ("Women's List"), a political party in Iceland * KL FM, a Malay language radio station Places * Kaiserslautern, Germany (license plate code KL) * Kerala, India (ISO 3166-2:IN subcode KL) * Kirkland Lake, Ontario, Canada * Kowloon, Hong Kong * Kuala Lumpur, Malaysia Science, technology, and mathematics * KL engine, version of the Mazda K engine * Klepton (kl.), a type of species in zoology * Kiloliter (kL), a unit of volume * Kullback–Leibler divergence in mathematics * KL (gene), a gene which encodes the klotho enzyme in humans Other uses * Jeep Cherokee (KL) * Kalaallisut language (ISO 639 alpha-2 language code "kl") * Kl (digraph), used in the Zulu language to write /kʟ̥ʼ/ or /kxʼ/ * Konzentrationslager, or concentration camp, abbreviated KZ or KL * ''KL – A History of the Nazi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SGI Challenge

The Challenge, code-named ''Eveready'' (deskside models) and ''Terminator'' (rackmount models), is a family of server computers and supercomputers developed and manufactured by Silicon Graphics in the early to mid-1990s that succeeded the earlier Power Series systems (not to be confused with IBM Power Systems). The Challenge was later succeeded by the NUMAlink-based Origin 200 and Origin 2000 in 1996. Models There are three distinctive models of the Challenge. The first model, simply known as the "Challenge" used the 64-bit R4400. With the introduction of the R8000, the Challenge was upgraded to support more processors and memory as well as featuring support for this new processor. Such systems are known as the "POWER Challenge". During the final years of the Challenge architecture's useful life, the line was upgraded to support R10000 microprocessors. Older Challenge systems using the R10000 were known as the "Challenge 10000", while the newer POWER Challenge systems using th ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CPU Cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (MMU) w ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Scalar Processor

Scalar processors are a class of computer processors that process only one data item at a time. Typical data items include integers and floating point numbers. Classification A scalar processor is classified as a single instruction, single data (SISD) processor in Flynn's taxonomy. The Intel 486 is an example of a scalar processor. It is to be contrasted with a vector processor where a single instruction operates simultaneously on multiple data items (and thus is referred to as a single instruction, multiple data (SIMD) processor). The difference is analogous to the difference between scalar and vector arithmetic. The term ''scalar'' in computing dates to the 1970 and 1980s when vector processors were first introduced. It was originally used to distinguish the older designs from the new vector processors. Superscalar processor A superscalar processor (such as the Intel P5) may execute more than one instruction during a clock cycle by simultaneously dispatching multiple inst ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Out-of-order Execution

In computer engineering, out-of-order execution (or more formally dynamic execution) is a paradigm used in most high-performance central processing units to make use of instruction cycles that would otherwise be wasted. In this paradigm, a processor executes instructions in an order governed by the availability of input data and execution units, rather than by their original order in a program. In doing so, the processor can avoid being idle while waiting for the preceding instruction to complete and can, in the meantime, process the next instructions that are able to run immediately and independently. History Out-of-order execution is a restricted form of data flow computation, which was a major research area in computer architecture in the 1970s and early 1980s. The first machine to use out-of-order execution was the CDC 6600 (1964), designed by James E. Thornton, which uses a scoreboard to avoid conflicts. It permits an instruction to execute if its source operand (read) a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Register Renaming

In computer architecture, register renaming is a technique that abstracts logical registers from physical registers. Every logical register has a set of physical registers associated with it. When a machine language instruction refers to a particular logical register, the processor transposes this name to one specific physical register on the fly. The physical registers are opaque and cannot be referenced directly but only via the canonical names. This technique is used to eliminate false data dependencies arising from the reuse of registers by successive instructions that do not have any real data dependencies between them. The elimination of these false data dependencies reveals more instruction-level parallelism in an instruction stream, which can be exploited by various and complementary techniques such as superscalar and out-of-order execution for better performance. Problem approach In a register machine, programs are composed of instructions which operate on values. The ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Superscalar

A superscalar processor is a CPU that implements a form of parallelism called instruction-level parallelism within a single processor. In contrast to a scalar processor, which can execute at most one single instruction per clock cycle, a superscalar processor can execute more than one instruction during a clock cycle by simultaneously dispatching multiple instructions to different execution units on the processor. It therefore allows more throughput (the number of instructions that can be executed in a unit of time) than would otherwise be possible at a given clock rate. Each execution unit is not a separate processor (or a core if the processor is a multi-core processor), but an execution resource within a single CPU such as an arithmetic logic unit. In Flynn's taxonomy, a single-core superscalar processor is classified as an SISD processor (single instruction stream, single data stream), though a single-core superscalar processor that supports short vector operations could ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

NEC VR10000 Late Die

is a Japanese multinational information technology and electronics corporation, headquartered in Minato, Tokyo. The company was known as the Nippon Electric Company, Limited, before rebranding in 1983 as NEC. It provides IT and network solutions, including cloud computing, artificial intelligence (AI), Internet of things (IoT) platform, and telecommunications equipment and software to business enterprises, communications services providers and to government agencies, and has also been the biggest PC vendor in Japan since the 1980s when it launched the PC-8000 series. NEC was the world's fourth-largest PC manufacturer by 1990. Its semiconductors business unit was the world's largest semiconductor company by annual revenue from 1985 to 1992, the second largest in 1995, one of the top three in 2000, and one of the top 10 in 2006. NEC spun off its semiconductor business to Renesas Electronics and Elpida Memory. Once Japan's major electronics company, NEC has largely withdrawn from ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |