|

PowerPC E5500

The PowerPC e5500 is a 64-bit Power ISA-based microprocessor core from Freescale Semiconductor. The core implements most of the core of the Power ISA v.2.06 with hypervisor support, but not AltiVec. It has a four issue, seven-stage out-of-order pipeline with a double precision FPU, three Integer units, 32/32 KB data and instruction L1 caches, 512 KB private L2 cache per core and up to 2 MB shared L3 cache. Speeds range up to 2.5 GHz, and the core is designed to be highly configurable via the CoreNet fabric and meet the specific needs of embedded applications with features like multi-core operation and interface for auxiliary application processing units (APU). Design The e5500 is based on the e500mc core and adds some new instructions introduced in the Power ISA 2.06 specification, namely some byte- and bit-level acceleration; Parity, Population count, Bit permute and Compare byte. The FPU is taken straight from the PowerPC e600 core, which is a classic fully pipeli ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

64-bit

In computer architecture, 64-bit integers, memory addresses, or other data units are those that are 64 bits wide. Also, 64-bit CPUs and ALUs are those that are based on processor registers, address buses, or data buses of that size. A computer that uses such a processor is a 64-bit computer. From the software perspective, 64-bit computing means the use of machine code with 64-bit virtual memory addresses. However, not all 64-bit instruction sets support full 64-bit virtual memory addresses; x86-64 and ARMv8, for example, support only 48 bits of virtual address, with the remaining 16 bits of the virtual address required to be all 0's or all 1's, and several 64-bit instruction sets support fewer than 64 bits of physical memory address. The term ''64-bit'' also describes a generation of computers in which 64-bit processors are the norm. 64 bits is a word size that defines certain classes of computer architecture, buses, memory, and CPUs and, by extension, the software that ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PowerPC E500

The PowerPC e500 is a 32-bit microprocessor core from Freescale Semiconductor. The core is compatible with the older PowerPC Book E specification as well as the Power ISA v.2.03. It has a dual issue, seven-stage pipeline with FPUs (from version 2 onwards), 32/32 KiB data and instruction L1 caches and 256, 512 or 1024 KiB L2 frontside cache. Speeds range from 533 MHz up to 1.5 GHz, and the core is designed to be highly configurable and meet the specific needs of embedded applications with features like multi-core operation interface for auxiliary application processing units (APU). e500 powers the high-performance PowerQUICC III system on a chip (SoC) network processors and they all share a common naming scheme, ''MPC85xx''. Freescale's new QorIQ is the evolutionary step from PowerQUICC III and will also be based on e500 cores. Versions There are three versions of the e500 core, namely the original ''e500v1'', the ''e500v2'' and the ''e500mc''. A 6 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PowerPC Microprocessors

PowerPC (with the backronym Performance Optimization With Enhanced RISC – Performance Computing, sometimes abbreviated as PPC) is a reduced instruction set computer (RISC) instruction set architecture (ISA) created by the 1991 Apple– IBM–Motorola alliance, known as AIM. PowerPC, as an evolving instruction set, has been named Power ISA since 2006, while the old name lives on as a trademark for some implementations of Power Architecture–based processors. PowerPC was the cornerstone of AIM's PReP and Common Hardware Reference Platform (CHRP) initiatives in the 1990s. Originally intended for personal computers, the architecture is well known for being used by Apple's Power Macintosh, PowerBook, iMac, iBook, eMac, Mac Mini, and Xserve lines from 1994 until 2005, when Apple migrated to Intel's x86. It has since become a niche in personal computers, but remains popular for embedded and high-performance processors. Its use in 7th generation of video game consoles ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

RAD5500

The RAD5500 is a radiation-hardened 64-bit processor core design created by BAE Systems Electronics, Intelligence & Support based on the PowerPC e5500 designed by IBM and Freescale Semiconductor. Successor of the RAD750, the RAD5500 processor platform is for use in high radiation environments experienced on board satellites and spacecraft. The RAD5500 core supports VPX high speed connectors, DDR2/DDR3 memory, serialize/deserialize (SerDes), and SpaceWire IO. Processors The RAD5500 core is based on those of the Freescale Semiconductor e5500-based QorIQ system-on-chip. The RAD5510, RAD5515, RAD5545, and RADSPEED-HB (host bridge) are four system on a chip processors implemented with RAD5500 cores produced with 45 nm SOI technology from the IBM Trusted Foundry. RAD5510 and RAD5515 The RAD5510 and RAD5515 processors employ a single RAD5500 core and are intended for medium processing capability in environments that require low power consumption (11.5 and 13.7 watts respe ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PowerPC E6500

The PowerPC e6500 is a multithreaded 64-bit Power ISA-based microprocessor core from Freescale Semiconductor (now part of NXP). e6500 will power the entire range of QorIQ AMP Series system on a chip (SoC) processors which share the common naming scheme: "Txxxx". Hard samples, manufactured on a 28 nm process, available in early 2012 with full production later in 2012. Design It has a revised memory subsystem compared to the previous e5500 core with four cores combined into a CPU Cluster, sharing a large L2 cache and the e6500 cores supports up to eight CPU Clusters for very large multiprocessing implementations. The core is the first multithreaded core designed by Freescale and reintroduces an enhanced version of AltiVec to their products. The multithreading allows for two virtual cores per hard core and is organized as 2x2-way superscalar. One virtual core in an e6500 can often perform better than an entire e5500 core since Freescale essentially duplicated a lot of l ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PowerPC E700

The PowerPC e700 or NG-64 (Next Generation 64-bit) were the codenames of Freescale's first 64-bit embedded RISC- processor cores. In 2004 Freescale announced a new high performance core. Not much was known about it. It would be a multi core, multithreaded design using CoreNet technology, shared with the e500mc core. It would be a three issue core with double precision FPU. Roadmaps showed a target frequency of 3+ GHz, manufactured on a 32 nm process and that the chips would be named on a MPC87xx scheme. Freescale released a core with similar specifications in June 2010 called the e5500. See also * PowerPC e5500 * PowerPC e500 The PowerPC e500 is a 32-bit microprocessor core from Freescale Semiconductor. The core is compatible with the older PowerPC Book E specification as well as the Power ISA v.2.03. It has a dual issue, seven-stage pipeline with FPUs (from versi ... * Motorola G5 project (Motorola's defunct 64-bit PowerPC project) External links Multi-Core Design: Ke ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Radiation Hardening

Radiation hardening is the process of making electronic components and circuits resistant to damage or malfunction caused by high levels of ionizing radiation ( particle radiation and high-energy electromagnetic radiation), especially for environments in outer space (especially beyond the low Earth orbit), around nuclear reactors and particle accelerators, or during nuclear accidents or nuclear warfare. Most semiconductor electronic components are susceptible to radiation damage, and radiation-hardened (rad-hard) components are based on their non-hardened equivalents, with some design and manufacturing variations that reduce the susceptibility to radiation damage. Due to the extensive development and testing required to produce a radiation-tolerant design of a microelectronic chip, the technology of radiation-hardened chips tends to lag behind the most recent developments. Radiation-hardened products are typically tested to one or more resultant-effects tests, including tot ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

BAE Systems

BAE Systems plc (BAE) is a British multinational arms, security, and aerospace company based in London, England. It is the largest defence contractor in Europe, and ranked the seventh-largest in the world based on applicable 2021 revenues. As of 2017, it is the biggest manufacturer in Britain. Its largest operations are in the United Kingdom and United States, where its BAE Systems Inc. subsidiary is one of the six largest suppliers to the US Department of Defense. Other major markets include Australia, Canada, Japan, India, Saudi Arabia, Turkey, Qatar, Oman and Sweden, where Saudi Arabia is regularly among its top three sources of revenue. The company was formed on 30 November 1999 by the £7.7 billion purchase of and merger with Marconi Electronic Systems (MES), the defence electronics and naval shipbuilding subsidiary of the General Electric Company plc (GEC), by British Aerospace, an aircraft, munitions and naval systems manufacturer. BAE is the successor to ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

System On A Chip

A system on a chip or system-on-chip (SoC ; pl. ''SoCs'' ) is an integrated circuit that integrates most or all components of a computer or other electronic system. These components almost always include a central processing unit (CPU), memory interfaces, on-chip input/output devices, input/output interfaces, and secondary storage interfaces, often alongside other components such as radio modems and a graphics processing unit (GPU) – all on a single substrate or microchip. It may contain digital, analog, mixed-signal, and often radio frequency signal processing functions (otherwise it is considered only an application processor). Higher-performance SoCs are often paired with dedicated and physically separate memory and secondary storage (such as LPDDR and eUFS or eMMC, respectively) chips, that may be layered on top of the SoC in what's known as a package on package (PoP) configuration, or be placed close to the SoC. Additionally, SoCs may use separate wireless ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

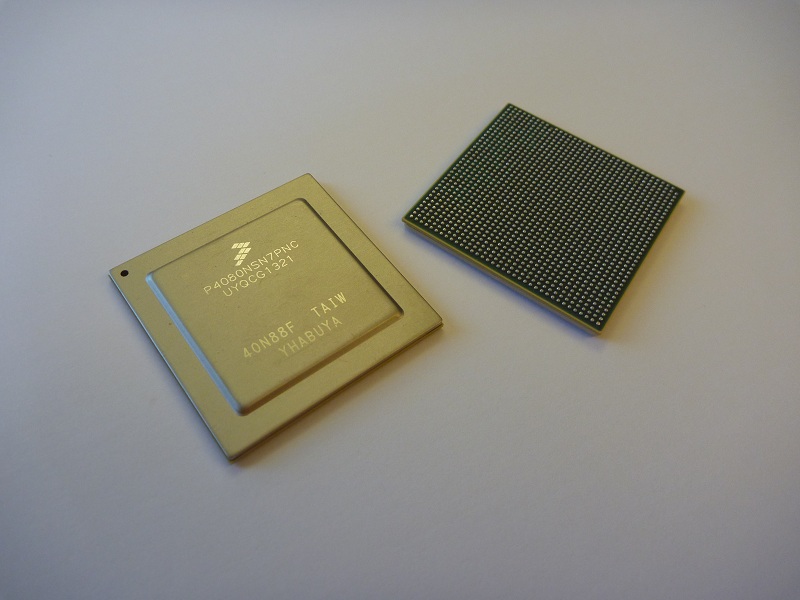

QorIQ

QorIQ is a brand of ARM-based and Power ISA-based communications microprocessors from NXP Semiconductors (formerly Freescale). It is the evolutionary step from the PowerQUICC platform, and initial products were built around one or more e500mc cores and came in five different product platforms, P1, P2, P3, P4, and P5, segmented by performance and functionality. The platform keeps software compatibility with older PowerPC products such as the PowerQUICC platform. In 2012 Freescale announced ARM-based QorIQ offerings beginning in 2013. The QorIQ brand and the P1, P2 and P4 product families were announced in June 2008. Details of P3 and P5 products were announced in 2010. QorIQ P Series processors were manufactured on a 45 nm fabrication process and was available in the end of 2008 (P1 and P2), mid-2009 (P4) and 2010 (P5). QorIQ T Series is based on a 28 nm process and is pushing a very aggressive power envelope target, capping at 30 W. These are using the e6500 core with ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Branch Predictor

In computer architecture, a branch predictor is a digital circuit that tries to guess which way a branch (e.g., an if–then–else structure) will go before this is known definitively. The purpose of the branch predictor is to improve the flow in the instruction pipeline. Branch predictors play a critical role in achieving high performance in many modern pipelined microprocessor architectures such as x86. Two-way branching is usually implemented with a conditional jump instruction. A conditional jump can either be "taken" and jump to a different place in program memory, or it can be "not taken" and continue execution immediately after the conditional jump. It is not known for certain whether a conditional jump will be taken or not taken until the condition has been calculated and the conditional jump has passed the execution stage in the instruction pipeline (see fig. 1). Without branch prediction, the processor would have to wait until the conditional jump instruction ha ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IEEE Floating Point

The IEEE Standard for Floating-Point Arithmetic (IEEE 754) is a technical standard for floating-point arithmetic established in 1985 by the Institute of Electrical and Electronics Engineers (IEEE). The standard addressed many problems found in the diverse floating-point implementations that made them difficult to use reliably and portably. Many hardware floating-point units use the IEEE 754 standard. The standard defines: * ''arithmetic formats:'' sets of binary and decimal floating-point data, which consist of finite numbers (including signed zeros and subnormal numbers), infinities, and special "not a number" values ( NaNs) * ''interchange formats:'' encodings (bit strings) that may be used to exchange floating-point data in an efficient and compact form * ''rounding rules:'' properties to be satisfied when rounding numbers during arithmetic and conversions * ''operations:'' arithmetic and other operations (such as trigonometric functions) on arithmetic formats * ''e ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |