|

PWRficient

PWRficient is a microprocessor series by P.A. Semi where the PA6T-1682M was the only one that became an actual product. PWRficient processors comply with the 64-bit Power ISA, and are designed for high performance and extreme power efficiency. The processors are highly modular and can be combined to multi-core system-on-a-chip (SoC) designs, combining CPU, northbridge, and southbridge functionality on a single processor die. Details The PA6T is the first and only processor core from P.A. Semi, in two distinct product lines: 16xxM dual core and 13xxM/E single core. The PA6T lines differed in L2 cache size, memory controllers, communication functionality, and cryptography offloading features. P.A. Semi planned up to 16 cores. The PA6T is the first Power ISA core designed from scratch in the previous ten years outside the AIM alliance, which included IBM, Motorola, Freescale, and Apple Inc. Since Texas Instruments was an investors in P.A. Semi, it was suggested that its fabrica ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Apple Silicon

Apple silicon is a series of system on a chip (SoC) and system in a package (SiP) processors designed by Apple Inc., mainly using the ARM architecture. It is the basis of most new Mac computers as well as iPhone, iPad, iPod Touch, Apple TV, and Apple Watch, and of products such as AirPods, HomePod, HomePod Mini, and AirTag. Apple announced its plan to switch Mac computers from Intel processors to Apple silicon at WWDC 2020 on June 22, 2020. The first Macs built with the Apple M1 processor were unveiled on November 10, 2020. In 2022, the newest Mac models were built with Apple silicon; only older models of the Mac Mini and the Mac Pro still use Intel Core and Xeon processors respectively. Apple fully controls the integration of Apple silicon chips with the company's hardware and software products. Johny Srouji is in charge of Apple's silicon design. Manufacturing of the chips is outsourced to semiconductor contract manufacturers such as Samsung and TSMC. A s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Power ISA

Power ISA is a reduced instruction set computer (RISC) instruction set architecture (ISA) currently developed by the OpenPOWER Foundation, led by IBM. It was originally developed by IBM and the now-defunct Power.org industry group. Power ISA is an evolution of the PowerPC ISA, created by the mergers of the core PowerPC ISA and the optional Book E for embedded applications. The merger of these two components in 2006 was led by Power.org founders IBM and Freescale Semiconductor. The ISA is divided into several ''categories'' which are described in a certain ''Book''. Processors implement a set of these categories as required for their task. Different classes of processors are required to implement certain categories, for example a server-class processor includes the categories: ''Base'', ''Server'', ''Floating-Point'', ''64-Bit'', etc. All processors implement the Base category. Power ISA is a RISC load/store architecture. It has multiple sets of registers: * ''32'' × 32-bi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Microprocessor

A microprocessor is a computer processor where the data processing logic and control is included on a single integrated circuit, or a small number of integrated circuits. The microprocessor contains the arithmetic, logic, and control circuitry required to perform the functions of a computer's central processing unit. The integrated circuit is capable of interpreting and executing program instructions and performing arithmetic operations. The microprocessor is a multipurpose, Clock signal, clock-driven, Processor register, register-based, digital integrated circuit that accepts binary code, binary data as input, processes it according to instruction (computing), instructions stored in its computer memory, memory, and provides results (also in binary form) as output. Microprocessors contain both combinational logic and sequential logic, sequential digital logic, and operate on numbers and symbols represented in the binary number system. The integration of a whole CPU onto a s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

MOESI Protocol

(For a detailed description see Cache coherency protocols (examples)) In computing, MOESI is a full cache coherency protocol that encompasses all of the possible states commonly used in other protocols. In addition to the four common MESI protocol states, there is a fifth "Owned" state representing data that is both modified and shared. This avoids the need to write modified data back to main memory before sharing it. While the data must still be written back eventually, the write-back may be deferred. In order for this to be possible, direct cache-to-cache transfers of data must be possible, so a cache with the data in the modified state can supply that data to another reader without transferring it to memory. As discussed in AMD64 Architecture Programmer's Manual Vol. 2 System Programming''', each cache line is in one of five states: ;Modified: This cache has the only valid copy of the cache line, and has made changes to that copy. ;Owned:This cache is one of several with ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DDR2 SDRAM

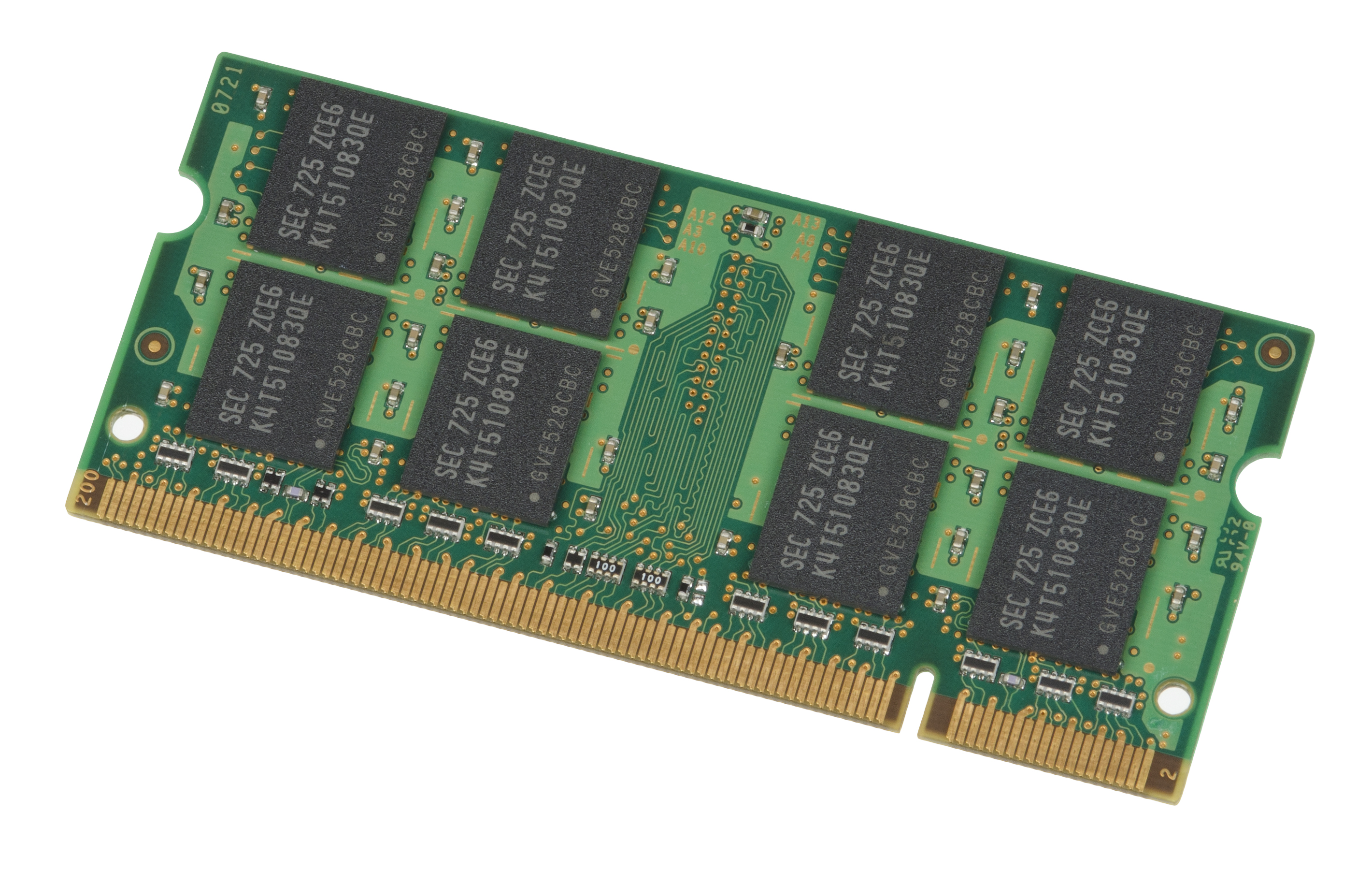

Double Data Rate 2 Synchronous Dynamic Random-Access Memory (DDR2 SDRAM) is a double data rate (DDR) synchronous dynamic random-access memory (SDRAM) interface. It superseded the original DDR SDRAM specification, and was itself superseded by DDR3 SDRAM (launched in 2007). DDR2 DIMMs are neither forward compatible with DDR3 nor backward compatible with DDR. In addition to double pumping the data bus as in DDR SDRAM (transferring data on the rising and falling edges of the bus clock signal), DDR2 allows higher bus speed and requires lower power by running the internal clock at half the speed of the data bus. The two factors combine to produce a total of four data transfers per internal clock cycle. Since the DDR2 internal clock runs at half the DDR external clock rate, DDR2 memory operating at the same external data bus clock rate as DDR results in DDR2 being able to provide the same bandwidth but with better latency. Alternatively, DDR2 memory operating at twice the external d ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Symmetric Multiprocessing

Symmetric multiprocessing or shared-memory multiprocessing (SMP) involves a multiprocessor computer hardware and software architecture where two or more identical processors are connected to a single, shared main memory, have full access to all input and output devices, and are controlled by a single operating system instance that treats all processors equally, reserving none for special purposes. Most multiprocessor systems today use an SMP architecture. In the case of multi-core processors, the SMP architecture applies to the cores, treating them as separate processors. Professor John D. Kubiatowicz considers traditionally SMP systems to contain processors without caches. Culler and Pal-Singh in their 1998 book "Parallel Computer Architecture: A Hardware/Software Approach" mention: "The term SMP is widely used but causes a bit of confusion. ..The more precise description of what is intended by SMP is a shared memory multiprocessor where the cost of accessing a memory locatio ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Hardware-assisted Virtualization

In computing, hardware-assisted virtualization is a platform virtualization approach that enables efficient full virtualization using help from hardware capabilities, primarily from the host processors. A full virtualization is used to emulate a complete hardware environment, or virtual machine, in which an unmodified guest operating system (using the same instruction set as the host machine) effectively executes in complete isolation. Hardware-assisted virtualization was added to x86 processors (Intel VT-x, AMD-V or VIA VT) in 2005, 2006 and 2010 (respectively). Hardware-assisted virtualization is also known as accelerated virtualization; Xen calls it hardware virtual machine (HVM), and Virtual Iron calls it native virtualization. History Hardware-assisted virtualization first appeared on the IBM System/370 in 1972, for use with VM/370, the first virtual machine operating system. With the increasing demand for high-definition computer graphics (e.g. CAD), virtualizatio ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Hypervisor

A hypervisor (also known as a virtual machine monitor, VMM, or virtualizer) is a type of computer software, firmware or hardware that creates and runs virtual machines. A computer on which a hypervisor runs one or more virtual machines is called a ''host machine'', and each virtual machine is called a ''guest machine''. The hypervisor presents the guest operating systems with a virtual operating platform and manages the execution of the guest operating systems. Unlike an emulator, the guest executes most instructions on the native hardware. Multiple instances of a variety of operating systems may share the virtualized hardware resources: for example, Linux, Windows, and macOS instances can all run on a single physical x86 machine. This contrasts with operating-system–level virtualization, where all instances (usually called ''containers'') must share a single kernel, though the guest operating systems can differ in user space, such as different Linux distributions with the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Floating Point Unit

Floating may refer to: * a type of dental work performed on horse teeth * use of an isolation tank * the guitar-playing technique where chords are sustained rather than scratched * ''Floating'' (play), by Hugh Hughes * Floating (psychological phenomenon), slipping into altered states * Floating exchange rate, a market-valued currency * Floating voltage, and floating ground, a voltage or ground in an electric circuit that is not connected to the Earth or another reference voltage * Floating point, a representation in computing of rational numbers most commonly associated with the IEEE 754 standard * ''Floating'' (film), a 1997 American drama film Albums and songs * ''Floating'' (Eloy album) (1974) * ''Floating'' (Ketil Bjørnstad album) (2005) * ''Floating'' (EP), a 1991 EP by Bill Callahan * "Floating" (The Moody Blues song) (1969) * "Floating" (Megan Rochell song) (2006) * "Floating" (Jape song) (2004) * "Floating", a song by Jolin Tsai from the 2000 album ''Don't Sto ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Double Precision

Double-precision floating-point format (sometimes called FP64 or float64) is a floating-point number format, usually occupying 64 bits in computer memory; it represents a wide dynamic range of numeric values by using a floating radix point. Floating point is used to represent fractional values, or when a wider range is needed than is provided by fixed point (of the same bit width), even if at the cost of precision. Double precision may be chosen when the range or precision of single precision would be insufficient. In the IEEE 754-2008 standard, the 64-bit base-2 format is officially referred to as binary64; it was called double in IEEE 754-1985. IEEE 754 specifies additional floating-point formats, including 32-bit base-2 ''single precision'' and, more recently, base-10 representations. One of the first programming languages to provide single- and double-precision floating-point data types was Fortran. Before the widespread adoption of IEEE 754-1985, the representation a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Execution Unit

In computer engineering, an execution unit (E-unit or EU) is a part of the central processing unit (CPU) that performs the operations and calculations as instructed by the computer program. It may have its own internal control sequence unit (not to be confused with the CPU's main control unit), some registers, and other internal units such as an arithmetic logic unit (ALU), address generation unit (AGU), floating-point unit (FPU), load-store unit (LSU), branch execution unit (BEU) or some smaller and more specific components. archived on the |