|

PS2 Vector Unit

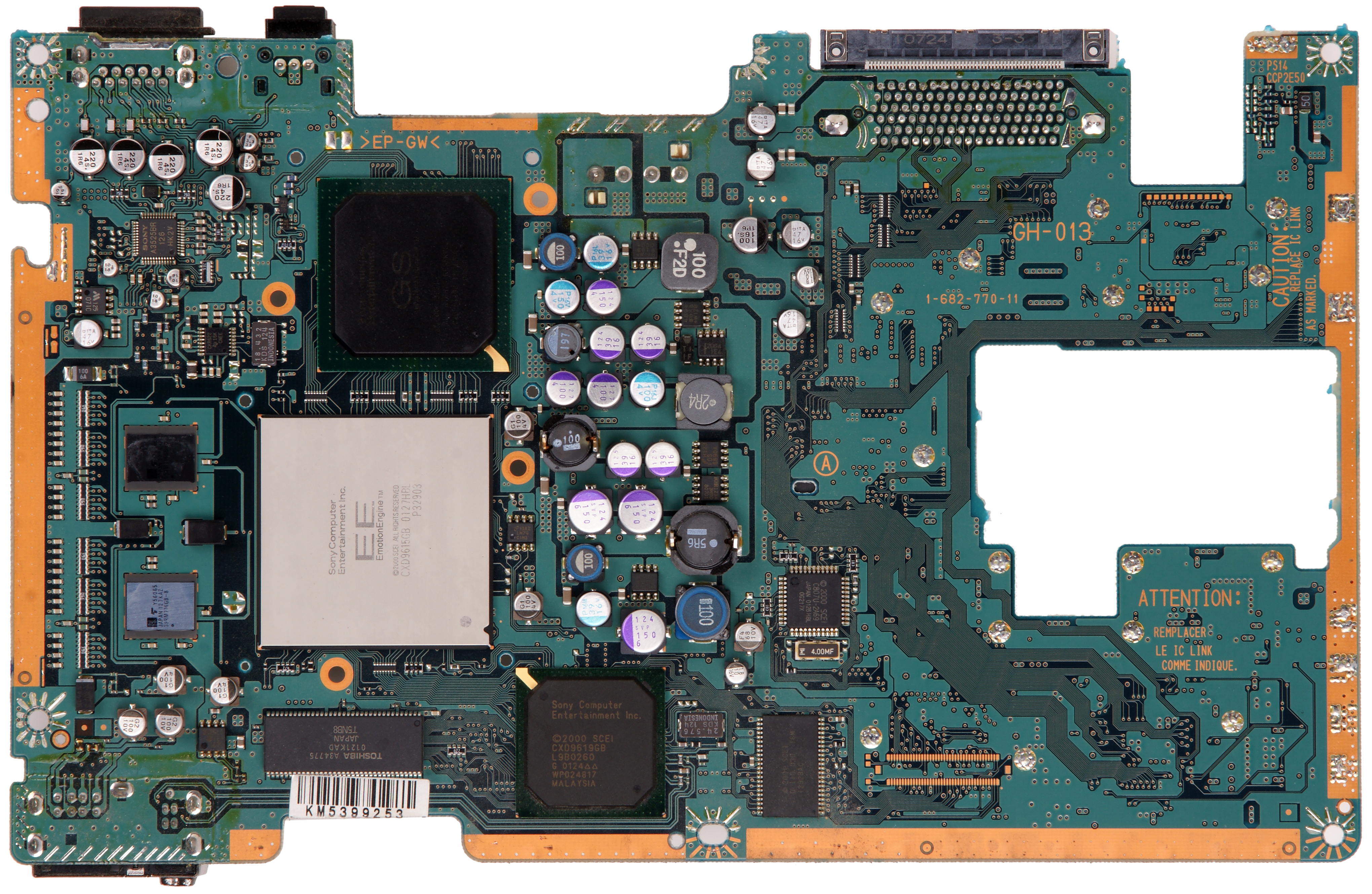

The Emotion Engine is a central processing unit developed and manufactured by Sony Computer Entertainment and Toshiba for use in the PlayStation 2 video game console. It was also used in early PlayStation 3 models sold in Japan and North America (Model Numbers CECHAxx & CECHBxx) to provide PlayStation 2 game support. Mass production of the Emotion Engine began in 1999 and ended in late 2012 with the discontinuation of the PlayStation 2. Description The Emotion Engine consists of eight separate "units", each performing a specific task, integrated onto the same die. These units are: a CPU core, two Vector Processing Units (VPU), a 10-channel DMA unit, a memory controller, and an Image Processing Unit (IPU). There are three interfaces: an input output interface to the I/O processor, a graphics interface (GIF) to the graphics synthesizer, and a memory interface to the system memory. The CPU core is tightly coupled to the first VPU, VPU0. Together, they are responsible for ex ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Sony EmotionEngine CXD9615GB Top

is a Japanese multinational conglomerate headquartered at Sony City in Minato, Tokyo, Japan. The Sony Group encompasses various businesses, including Sony Corporation (electronics), Sony Semiconductor Solutions (imaging and sensing), Sony Entertainment (including Sony Pictures and Sony Music Group), Sony Interactive Entertainment (video games), Sony Financial Group, and others. Sony was founded in 1946 as by Masaru Ibuka and Akio Morita. In 1958, the company adopted the name Initially an electronics firm, it gained early recognition for products such as the TR-55 transistor radio and the CV-2000 home video tape recorder, contributing significantly to Japan's post-war economic recovery. After Ibuka's retirement in the 1970s, Morita served as chairman until 1994, overseeing Sony's rise as a global brand recognized for innovation in consumer electronics. Landmark products included the Trinitron color television, the Walkman portable audio player, and the co-developmen ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Graphics Synthesizer

The PlayStation 2 technical specifications describe the various components of the PlayStation 2 (PS2) video game console. Overview The sixth-generation hardware of the PlayStation 2 video game console consists of various components. At the heart of the console's configuration is its central processing unit (CPU), a custom RISC processor known as the Emotion Engine which operates at 294.912 MHz (299 MHz in later consoles). The CPU heavily relies on its integration with two vector processing units, known as VPU0 and VPU1, the Graphics Synthesizer, and a floating-point unit (FPU) in order to render 3D graphics. Other components, such as the system's DVD-ROM optical drive and DualShock 2 controller, provide the software and user control input. PlayStation 2 software is distributed on CD-ROM and DVD-ROM. In addition, the console can play audio CDs and DVD movies, and is backwards compatible with original PlayStation games. This is accomplished through the inclusion of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Floating-point Unit

A floating-point unit (FPU), numeric processing unit (NPU), colloquially math coprocessor, is a part of a computer system specially designed to carry out operations on floating-point numbers. Typical operations are addition, subtraction, multiplication, division, and square root. Modern designs generally include a fused multiply-add instruction, which was found to be very common in real-world code. Some FPUs can also perform various transcendental functions such as exponential or trigonometric calculations, but the accuracy can be low, so some systems prefer to compute these functions in software. Floating-point operations were originally handled in software in early computers. Over time, manufacturers began to provide standardized floating-point libraries as part of their software collections. Some machines, those dedicated to scientific processing, would include specialized hardware to perform some of these tasks with much greater speed. The introduction of microcode in ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Load–store Unit

In computer engineering, a load–store unit (LSU) is a specialized execution unit responsible for executing all load and store instructions, generating virtual addresses of load and store operations and loading data from memory or storing it back to memory from registers.''Memory Systems: Cache, DRAM, Disk'' by Bruce Jacob, Spencer Ng, David Wang 2007 page 298 The load–store unit usually includes a queue which acts as a waiting area for memory instructions, and the unit itself operates independently of other processor units. Load–store units may also be used in vector processing, and in such cases the term "load–store vector" may be used.''Computer Architecture: A Quantitative Approach'' by John L. Hennessy, David A. Patterson 2011 pages 293-295 Some load–store units are also capable of executing simple fixed-point and/or integer operations. See also * Address-generation unit * Arithmetic–logic unit * Floating-point unit A floating-point unit (FPU), numeric proc ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Arithmetic Logic Unit

In computing, an arithmetic logic unit (ALU) is a Combinational logic, combinational digital circuit that performs arithmetic and bitwise operations on integer binary numbers. This is in contrast to a floating-point unit (FPU), which operates on floating point numbers. It is a fundamental building block of many types of computing circuits, including the central processing unit (CPU) of computers, FPUs, and graphics processing units (GPUs). The inputs to an ALU are the data to be operated on, called operands, and a code indicating the operation to be performed (opcode); the ALU's output is the result of the performed operation. In many designs, the ALU also has status inputs or outputs, or both, which convey information about a previous operation or the current operation, respectively, between the ALU and external status registers. Signals An ALU has a variety of input and output net (electronics), nets, which are the electrical conductors used to convey Digital signal (electroni ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Floating-point

In computing, floating-point arithmetic (FP) is arithmetic on subsets of real numbers formed by a ''significand'' (a Sign (mathematics), signed sequence of a fixed number of digits in some Radix, base) multiplied by an integer power of that base. Numbers of this form are called floating-point numbers. For example, the number 2469/200 is a floating-point number in base ten with five digits: 2469/200 = 12.345 = \! \underbrace_\text \! \times \! \underbrace_\text\!\!\!\!\!\!\!\overbrace^ However, 7716/625 = 12.3456 is not a floating-point number in base ten with five digits—it needs six digits. The nearest floating-point number with only five digits is 12.346. And 1/3 = 0.3333… is not a floating-point number in base ten with any finite number of digits. In practice, most floating-point systems use Binary number, base two, though base ten (decimal floating point) is also common. Floating-point arithmetic operations, such as addition and division, approximate the correspond ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Pipeline (computing)

In computing, a pipeline, also known as a data pipeline, is a set of data processing elements connected in series, where the output of one element is the input of the next one. The elements of a pipeline are often executed in parallel or in time-sliced fashion. Some amount of buffer storage is often inserted between elements. Concept and motivation Pipelining is a commonly used concept in everyday life. For example, in the assembly line of a car factory, each specific task—such as installing the engine, installing the hood, and installing the wheels—is often done by a separate work station. The stations carry out their tasks in parallel, each on a different car. Once a car has had one task performed, it moves to the next station. Variations in the time needed to complete the tasks can be accommodated by "buffering" (holding one or more cars in a space between the stations) and/or by "stalling" (temporarily halting the upstream stations), until the next station becomes avai ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Streaming SIMD Extensions

In computing, Streaming SIMD Extensions (SSE) is a single instruction, multiple data ( SIMD) instruction set extension to the x86 architecture, designed by Intel and introduced in 1999 in its Pentium III series of central processing units (CPUs) shortly after the appearance of Advanced Micro Devices (AMD's) 3DNow!. SSE contains 70 new instructions (65 unique mnemonics using 70 encodings), most of which work on single precision floating-point data. SIMD instructions can greatly increase performance when exactly the same operations are to be performed on multiple data objects. Typical applications are digital signal processing and graphics processing. Intel's first IA-32 SIMD effort was the MMX instruction set. MMX had two main problems: it re-used existing x87 floating-point registers making the CPUs unable to work on both floating-point and SIMD data at the same time, and it only worked on integers. SSE floating-point instructions operate on a new independent register s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Single Instruction, Multiple Data

Single instruction, multiple data (SIMD) is a type of parallel computer, parallel processing in Flynn's taxonomy. SIMD describes computers with multiple processing elements that perform the same operation on multiple data points simultaneously. SIMD can be internal (part of the hardware design) and it can be directly accessible through an instruction set architecture (ISA), but it should not be confused with an ISA. Such machines exploit Data parallelism, data level parallelism, but not Concurrent computing, concurrency: there are simultaneous (parallel) computations, but each unit performs exactly the same instruction at any given moment (just with different data). A simple example is to add many pairs of numbers together, all of the SIMD units are performing an addition, but each one has different pairs of values to add. SIMD is particularly applicable to common tasks such as adjusting the contrast in a digital image or adjusting the volume of digital audio. Most modern Cen ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Instruction Set Architecture

In computer science, an instruction set architecture (ISA) is an abstract model that generally defines how software controls the CPU in a computer or a family of computers. A device or program that executes instructions described by that ISA, such as a central processing unit (CPU), is called an ''implementation'' of that ISA. In general, an ISA defines the supported instructions, data types, registers, the hardware support for managing main memory, fundamental features (such as the memory consistency, addressing modes, virtual memory), and the input/output model of implementations of the ISA. An ISA specifies the behavior of machine code running on implementations of that ISA in a fashion that does not depend on the characteristics of that implementation, providing binary compatibility between implementations. This enables multiple implementations of an ISA that differ in characteristics such as performance, physical size, and monetary cost (among other things), but t ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

MIPS Architecture

MIPS (Microprocessor without Interlocked Pipelined Stages) is a family of reduced instruction set computer (RISC) instruction set architectures (ISA)Price, Charles (September 1995). ''MIPS IV Instruction Set'' (Revision 3.2), MIPS Technologies, Inc. developed by MIPS Computer Systems, now MIPS Technologies, based in the United States. There are multiple versions of MIPS, including MIPS I, II, III, IV, and V, as well as five releases of MIPS32/64 (for 32- and 64-bit implementations, respectively). The early MIPS architectures were 32-bit; 64-bit versions were developed later. As of April 2017, the current version of MIPS is MIPS32/64 Release 6. MIPS32/64 primarily differs from MIPS I–V by defining the privileged kernel mode System Control Coprocessor in addition to the user mode architecture. The MIPS architecture has several optional extensions: MIPS-3D, a simple set of floating-point SIMD instructions dedicated to 3D computer graphics; MDMX (MaDMaX), a more extensive i ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Microprocessor Report

''Microprocessor Report'' is a newsletter covering the microprocessor industry. The publication is accessible only to paying subscribers. To avoid bias, it does not take advertisements. The publication provides extensive analysis of new high-performance microprocessor chips. It also covers microprocessor design issues, microprocessor-based systems, memory and system logic chips, embedded processors, GPUs, DSPs, and intellectual property (IP) cores. History and profile ''Microprocessor Report'' was first published in 1987 by Michael Slater (engineer). Original board members included Bruce Koball, George Morrow, Brian Case, John Wakerly, Nick Tredennick, Bernard Peuto, Rich Belgard, Dennis Allison, and J H Wharton all of whom served for many years. Slater left MicroDesign Resources (MDR), at the end of 1999. Slater's company MDR, based in Sebastopol, California, originally published ''Microprocessor Report.'' MDR also hosted an annual conference, the Microprocessor Forum, and r ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |