|

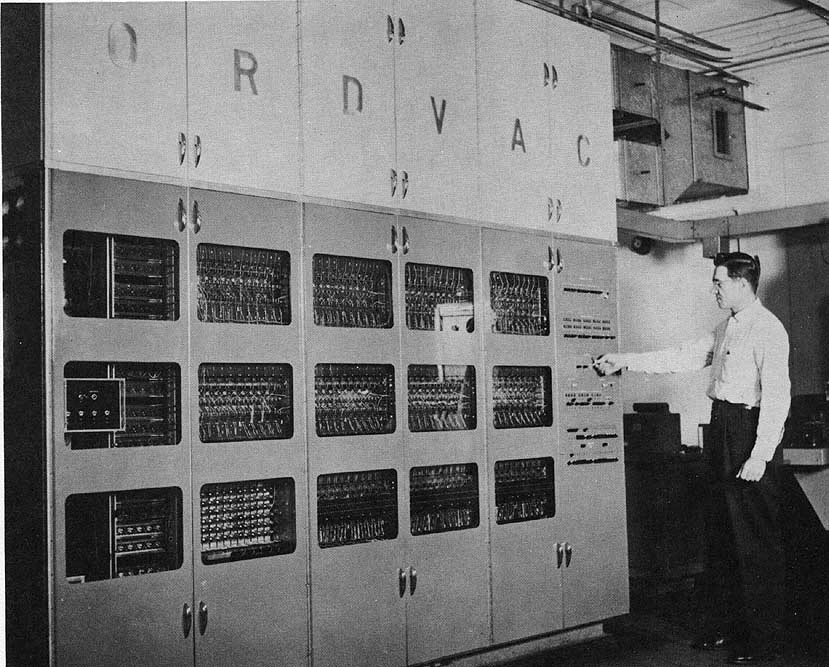

ORDVAC

The ORDVAC (''Ordnance Discrete Variable Automatic Computer)'', is an early computer built by the University of Illinois for the Ballistic Research Laboratory at Aberdeen Proving Ground. A successor to the ENIAC (along with EDVAC built earlier). It was based on the IAS architecture developed by John von Neumann, which came to be known as the von Neumann architecture. The ORDVAC was the first computer to have a compiler. ORDVAC passed its acceptance tests on March 6, 1952, at Aberdeen Proving Ground in Maryland. Its purpose was to perform ballistic trajectory calculations for the US Military. In 1992, the Ballistic Research Laboratory became a part of the U.S. Army Research Laboratory. Unlike the other computers of its era, the ORDVAC and ILLIAC I were twins and could exchange programs with each other. The later SILLIAC computer was a copy of the ORDVAC/ILLIAC series. J. P. Nash of the University of Illinois was a developer of both the ORDVAC and of the university's own identic ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

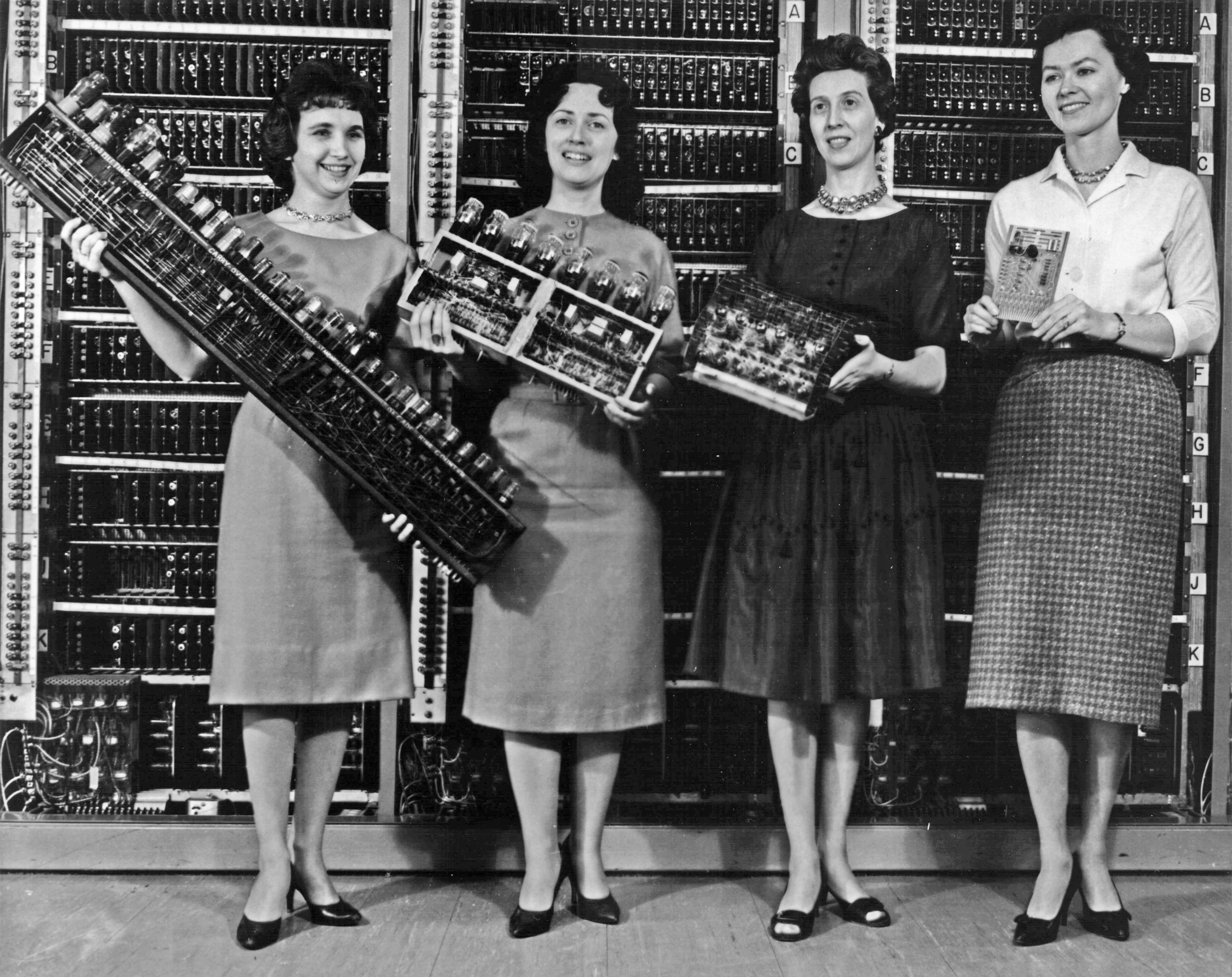

BRLESC

The BRLESC I (Ballistic Research Laboratories Electronic Scientific Computer) was one of the last of the first-generation electronic computers. It was built by the United States Army's Ballistic Research Laboratory (BRL) at Aberdeen Proving Ground with assistance from the National Bureau of Standards (now the National Institute of Standards and Technology), and was designed to take over the computational workload of EDVAC and ORDVAC, which themselves were successors of ENIAC. It began operation in 1962. The Ballistic Research Laboratory became a part of the U.S. Army Research Laboratory in 1992. BRLESC was designed primarily for scientific and military tasks requiring high precision and high computational speed, such as ballistics problems, army logistical problems, and weapons systems evaluations. It contained 1727 vacuum tubes and 853 transistors and had a memory of 4096 72-bit words. BRLESC employed punched cards, magnetic tape, and a magnetic drum as input-output devices, w ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ballistic Research Laboratory

The Ballistic Research Laboratory (BRL) was a leading U.S. Army research establishment situated at Aberdeen Proving Ground, Maryland that specialized in ballistics (interior, exterior, and terminal) as well as vulnerability and lethality analysis. BRL served as a major Army center for research and development in technologies related to weapon phenomena, armor, electronic devices, and high-speed computing. In 1992, BRL's mission, personnel, and facilities were incorporated into the newly created Army Research Laboratory (ARL), and BRL was disestablished. BRL is perhaps best known for commissioning the creation of ENIAC, the first electronic general-purpose digital computer. History Formation The history of the Ballistic Research Laboratory dates back to World War I with the Office of the Chief of Ordnance (OCO) within the U.S. Army. During the first year of U.S. involvement in the war, the OCO was responsible for supervising ballistic firings at Sandy Hook Proving Ground in ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Asynchronous Circuit

Asynchronous circuit (clockless or self-timed circuit) is a sequential digital logic circuit that does not use a global clock circuit or signal generator to synchronize its components. Instead, the components are driven by a handshaking circuit which indicates a completion of a set of instructions. Handshaking works by simple data transfer protocols. Many synchronous circuits were developed in early 1950s as part of bigger asynchronous systems (e.g. ORDVAC). Asynchronous circuits and theory surrounding is a part of several steps in integrated circuit design, a field of digital electronics engineering. Asynchronous circuits are contrasted with synchronous circuits, in which changes to the signal values in the circuit are triggered by repetitive pulses called a clock signal. Most digital devices today use synchronous circuits. However asynchronous circuits have a potential to be much faster, have a lower level of power consumption, electromagnetic interference, and better mod ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Von Neumann Architecture

The von Neumann architecture — also known as the von Neumann model or Princeton architecture — is a computer architecture based on a 1945 description by John von Neumann, and by others, in the '' First Draft of a Report on the EDVAC''. The document describes a design architecture for an electronic digital computer with these components: * A processing unit with both an arithmetic logic unit and processor registers * A control unit that includes an instruction register and a program counter * Memory that stores data and instructions * External mass storage * Input and output mechanisms.. The term "von Neumann architecture" has evolved to refer to any stored-program computer in which an instruction fetch and a data operation cannot occur at the same time (since they share a common bus). This is referred to as the von Neumann bottleneck, which often limits the performance of the corresponding system. The design of a von Neumann architecture machine is simpler than in ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ILLIAC I

The ILLIAC I (Illinois Automatic Computer), a pioneering computer in the ILLIAC series of computers built in 1952 by the University of Illinois, was the first computer built and owned entirely by a United States educational institution. Computer The project was the brainchild of Ralph Meagher and Abraham H. Taub, who both were associated with Princeton's Institute for Advanced Study before coming to the University of Illinois. The ILLIAC I became operational on September 1, 1952. It was the second of two identical computers, the first of which was ORDVAC, also built at the University of Illinois. These two machines were the first pair of machines to run the same instruction set. ILLIAC I was based on the IAS machine Von Neumann architecture as described by mathematician John von Neumann in his influential ''First Draft of a Report on the EDVAC''. Unlike most computers of its era, the ILLIAC I and ORDVAC computers were twin copies of the same design, with software compatibilit ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

List Of Vacuum Tube Computers

Vacuum-tube computers, now called first-generation computers, are programmable digital computers using vacuum-tube logic circuitry. They were preceded by systems using electromechanical relays and followed by systems built from discrete transistors. Some later computers on the list had both vacuum tubes and transistors. This list of vacuum-tube computers is sorted by date put into service: }) are identical, except input-output equipment. Both were used internally. , - , The Wegematic 1000 , , 1960 , , , Improved version of the ALWAC III-E , - , ZRA 1 , , 1960 , , , Built by VEB Carl Zeiss, Jena, German Democratic RepublicSiegmar Gerber: ''Einsatz von Zeiss-Rechnern für Forschung, Lehre und Dienstleistung in Informatik in der DDR – eine Bilanz''. GI-Edition, Bonn 2006, p. 310–318 , - , Minsk-1 , , 1960 , , , Built in Minsk , - , Odra 1001 , , 1960 , , , First computer built by Elwro, Wroclaw, Poland , - , Minsk-1 , , 1960 , , , Built in Minsk , ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IAS Machine

The IAS machine was the first electronic computer built at the Institute for Advanced Study (IAS) in Princeton, New Jersey. It is sometimes called the von Neumann machine, since the paper describing its design was edited by John von Neumann, a mathematics professor at both Princeton University and IAS. The computer was built from late 1945 until 1951 under his direction. The general organization is called von Neumann architecture, even though it was both conceived and implemented by others. The computer is in the collection of the Smithsonian National Museum of American History but is not currently on display. History Julian Bigelow was hired as chief engineer in May 1946. Hewitt Crane, Herman Goldstine, Gerald Estrin, Arthur Burks, George W. Brown (academic), George W. Brown and Willis Ware also worked on the project. The machine was in limited operation in the summer of 1951 and fully operational on June 10, 1952. It was in operation until July 15, 1958. Description The IAS ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Martin Davis (mathematician)

Martin David Davis (March 8, 1928 – January 1, 2023) was an American mathematician, known for his work on Hilbert's tenth problem.. Biography Davis's parents were Jewish immigrants to the US from Łódź, Poland, and married after they met again in New York City. Davis grew up in the Bronx, where his parents encouraged him to obtain a full education. Davis received his Ph.D. from Princeton University in 1950, where his advisor was Alonzo Church. During a research instructorship at the University of Illinois at Urbana-Champaign in the early 1950s, he joined the ''Control Systems Lab'' and became one of the early programmers of the ORDVAC. He was Professor Emeritus at New York University. Davis died on January 1, 2023, at the age of 94. Contributions Davis was the co-inventor of the Davis–Putnam algorithm and the DPLL algorithms. He is also known for his model of Post–Turing machines, and his work on Hilbert's tenth problem leading to the MRDP theorem. Awards and ho ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

History Of Computing Hardware

The history of computing hardware covers the developments from early simple devices to aid calculation to modern day computers. Before the 20th century, most calculations were done by humans. The first aids to computation were purely mechanical devices which required the operator to set up the initial values of an elementary arithmetic operation, then manipulate the device to obtain the result. Later, computers represented numbers in a continuous form (e.g. distance along a scale, rotation of a shaft, or a voltage). Numbers could also be represented in the form of digits, automatically manipulated by a mechanism. Although this approach generally required more complex mechanisms, it greatly increased the precision of results. The development of transistor technology and then the integrated circuit chip led to a series of breakthroughs, starting with transistor computers and then integrated circuit computers, causing digital computers to largely replace analog computers. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ILLIAC III

The ILLIAC III was a fine-grained SIMD pattern recognition computer built by the University of Illinois in 1966. This ILLIAC's initial task was image processing of bubble chamber experiments used to detect nuclear particles. Later it was used on biological images. The machine was destroyed in a fire, caused by a Variac shorting on one of the wooden-top benches, in 1968. It was rebuilt in the early 1970s, and the core parallel-processing element of the machine, the Pattern Articulation Unit, was successfully implemented. In spite of this and the productive exploration of other advanced concepts, such as multiple-radix arithmetic, the project was eventually abandoned. Bruce H. McCormick was the leader of the project throughout its history. File:ILLIAC III IMG 4178.jpg File:ILLIAC III IMG 4177.jpg, Printed circuits of the type used in ILLIAC III File:ILLIAC III IMG 4176.jpg, Printed circuits of the type used in ILLIAC III See also * ORDVAC * ILLIAC I * ILLIAC II * ILLIAC IV The ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ILLIAC II

The ILLIAC II was a revolutionary super-computer built by the University of Illinois that became operational in 1962. Description The concept, proposed in 1958, pioneered Emitter-coupled logic (ECL) circuitry, pipelining, and transistor memory with a design goal of 100x speedup compared to ILLIAC I. ILLIAC II had 8192 words of core memory, backed up by 65,536 words of storage on magnetic drums. The core memory access time was 1.8 to 2 µs. The magnetic drum access time was 8.5ms. A "fast buffer" was also provided for storage of short loops and intermediate results (similar in concept to what is now called cache). The "fast buffer" access time was 0.25 µs. The word size was 52 bits. Floating point numbers used a format with 7 bits of exponent (power of 4) and 45 bits of mantissa. Instructions were either 26 bits or 13 bits long, allowing packing of up to 4 instructions per memory word. Rather than naming the pipeline stages, "Fetch, Decode, and Execute" (as on Stretch), ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

.jpg)