|

MTA-2

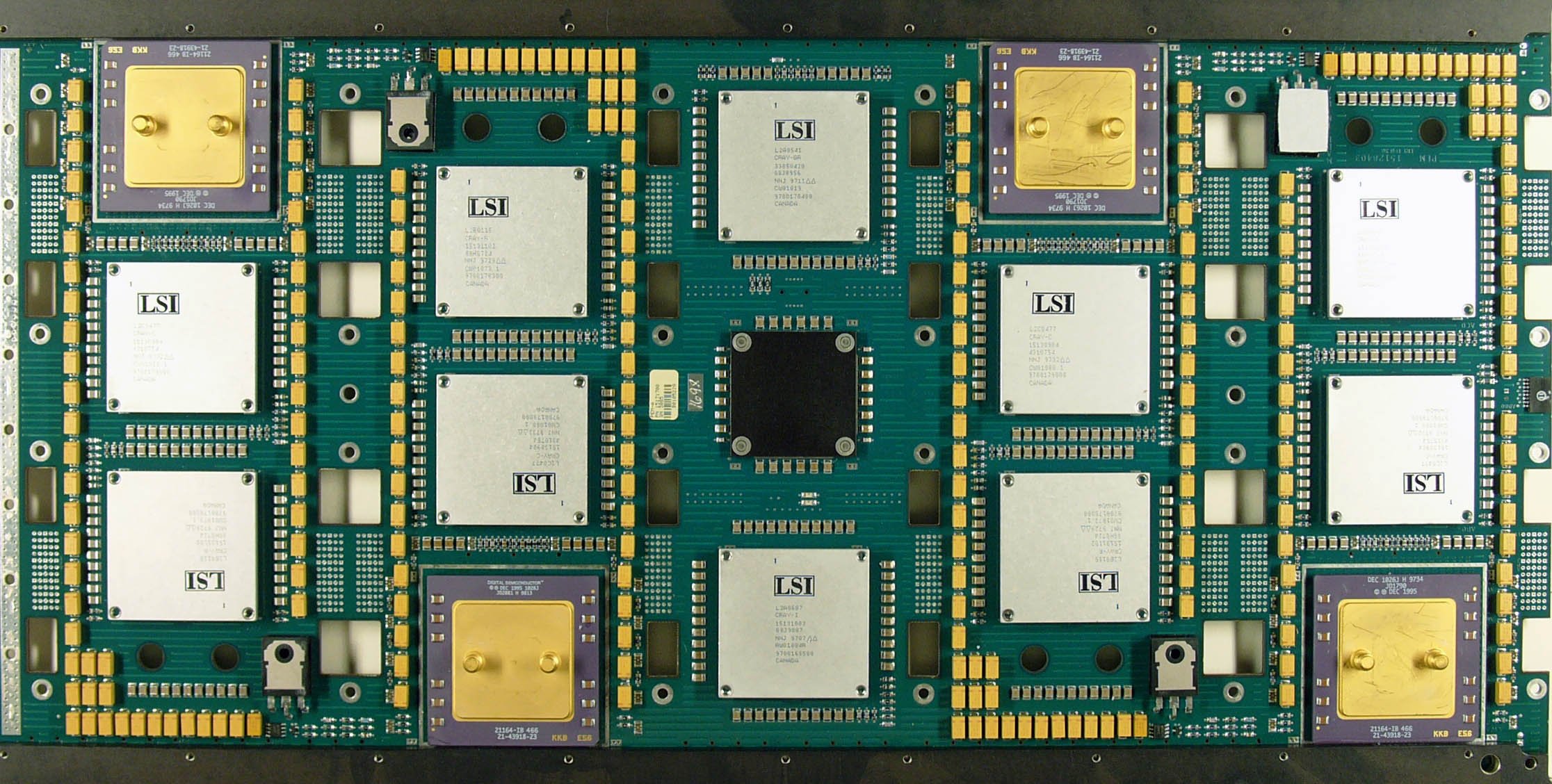

The Cray MTA-2 is a shared-memory MIMD computer marketed by Cray Inc. It is an unusual design based on the Tera computer designed by Tera Computer Company. The original Tera computer (also known as the ''MTA'') turned out to be nearly unmanufacturable due to its aggressive packaging and circuit technology. The MTA-2 was an attempt to correct these problems while maintaining essentially the same processor architecture respun in one silicon ASIC, down from some 26 gallium arsenide ASICs in the original MTA; and while regressing the network design from a 4-D torus topology to a less efficient but more scalable Cayley graph topology. The name ''Cray'' was added to the second version after Tera Computer Company bought the remains of the Cray Research division of Silicon Graphics in 2000 and renamed itself Cray Inc. The MTA-2 was not a commercial success, with only one moderately-sized 40-processor system ("Boomer") being sold to the United States Naval Research Laboratory in 2002, and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cray MTA

The Cray MTA, formerly known as the Tera MTA, is a supercomputer architecture based on thousands of independent threads, fine-grain communication and synchronization between threads, and latency tolerance for irregular computations. Each MTA processor ( CPU) has a high-performance ALU with many independent register sets, each running an independent thread. For example, the Cray MTA-2 uses 128 register sets and thus 128 threads per CPU/ALU. All MTAs to date use a barrel processor arrangement, with a thread switch on every cycle, with blocked (stalled) threads skipped to avoid wasting ALU cycles. When a thread performs a memory read, execution blocks until data returns; meanwhile, other threads continue executing. With enough threads (concurrency), there are nearly always runnable threads to "cover" for blocked threads, and the ALUs stay busy. The memory system uses full/empty bits to ensure correct ordering. For example, an array is initially written with "empty" bits, and an ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cray Inc

Cray Inc., a subsidiary of Hewlett Packard Enterprise, is an American supercomputer manufacturer headquartered in Seattle, Washington. It also manufactures systems for data storage and analytics. Several Cray supercomputer systems are listed in the TOP500, which ranks the most powerful supercomputers in the world. Cray manufactures its products in part in Chippewa Falls, Wisconsin, where its founder, Seymour Cray, was born and raised. The company also has offices in Bloomington, Minnesota (which have been converted to Hewlett Packard Enterprise offices), and numerous other sales, service, engineering, and R&D locations around the world. The company's predecessor, Cray Research, Inc. (CRI), was founded in 1972 by computer designer Seymour Cray. Seymour Cray later formed Cray Computer Corporation (CCC) in 1989, which went bankrupt in 1995. Cray Research was acquired by Silicon Graphics (SGI) in 1996. Cray Inc. was formed in 2000 when Tera Computer Company purchased the Cray Rese ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cray Products

Cray Inc., a subsidiary of Hewlett Packard Enterprise, is an American supercomputer manufacturer headquartered in Seattle, Washington. It also manufactures systems for data storage and analytics. Several Cray supercomputer systems are listed in the TOP500, which ranks the most powerful supercomputers in the world. Cray manufactures its products in part in Chippewa Falls, Wisconsin, where its founder, Seymour Cray, was born and raised. The company also has offices in Bloomington, Minnesota (which have been converted to Hewlett Packard Enterprise offices), and numerous other sales, service, engineering, and R&D locations around the world. The company's predecessor, Cray Research, Inc. (CRI), was founded in 1972 by computer designer Seymour Cray. Seymour Cray later formed Cray Computer Corporation (CCC) in 1989, which went bankrupt in 1995. Cray Research was acquired by Silicon Graphics (SGI) in 1996. Cray Inc. was formed in 2000 when Tera Computer Company purchased the Cray R ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Multiple Instruction, Multiple Data

In computing, multiple instruction, multiple data (MIMD) is a technique employed to achieve parallelism. Machines using MIMD have a number of processors that function asynchronously and independently. At any time, different processors may be executing different instructions on different pieces of data. MIMD architectures may be used in a number of application areas such as computer-aided design/computer-aided manufacturing, simulation, modeling, and as communication switches. MIMD machines can be of either shared memory or distributed memory categories. These classifications are based on how MIMD processors access memory. Shared memory machines may be of the bus-based, extended, or hierarchical type. Distributed memory machines may have hypercube or mesh interconnection schemes. Examples An example of MIMD system is Intel Xeon Phi, descended from Larrabee microarchitecture. These processors have multiple processing cores (up to 61 as of 2015) that can execute different instr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Tera Computer Company

The Tera Computer Company was a manufacturer of high-performance computing software and hardware, founded in 1987 in Washington, D.C. and moved 1988 to Seattle, Washington by James Rottsolk and Burton Smith. The company's first supercomputer product, named MTA, featured interleaved multi-threading, i.e. a barrel processor. It also had no data cache, relying instead on switching between threads for latency tolerance, and used a deeply pipelined memory system to handle many simultaneous requests, with address randomization to avoid memory hot spots. Upon acquiring the Cray Research division of Silicon Graphics in 2000, the company was renamed to Cray Inc. See also * Heterogeneous Element Processor The Heterogeneous Element Processor (HEP) was introduced by Denelcor, Inc. in 1982. The HEP's architect was Burton Smith. The machine was designed to solve fluid dynamics problems for the Ballistic Research Laboratory. A HEP system, as the nam ... References * Software ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cayley Graph

In mathematics, a Cayley graph, also known as a Cayley color graph, Cayley diagram, group diagram, or color group is a graph that encodes the abstract structure of a group. Its definition is suggested by Cayley's theorem (named after Arthur Cayley), and uses a specified set of generators for the group. It is a central tool in combinatorial and geometric group theory. The structure and symmetry of Cayley graphs makes them particularly good candidates for constructing families of expander graphs. Definition Let G be a group and S be a generating set of G. The Cayley graph \Gamma = \Gamma(G,S) is an edge-colored directed graph constructed as follows: In his Collected Mathematical Papers 10: 403–405. * Each element g of G is assigned a vertex: the vertex set of \Gamma is identified with G. * Each element s of S is assigned a color c_s. * For every g \in G and s \in S, there is a directed edge of color c_s from the vertex corresponding to g to the one corresponding to gs. Not ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Silicon Graphics

Silicon Graphics, Inc. (stylized as SiliconGraphics before 1999, later rebranded SGI, historically known as Silicon Graphics Computer Systems or SGCS) was an American high-performance computing manufacturer, producing computer hardware and software. Founded in Mountain View, California in November 1981 by Jim Clark, its initial market was 3D graphics computer workstations, but its products, strategies and market positions developed significantly over time. Early systems were based on the Geometry Engine that Clark and Marc Hannah had developed at Stanford University, and were derived from Clark's broader background in computer graphics. The Geometry Engine was the first very-large-scale integration (VLSI) implementation of a geometry pipeline, specialized hardware that accelerated the "inner-loop" geometric computations needed to display three-dimensional images. For much of its history, the company focused on 3D imaging and was a major supplier of both hardware and software ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Naval Research Laboratory

The United States Naval Research Laboratory (NRL) is the corporate research laboratory for the United States Navy and the United States Marine Corps. It was founded in 1923 and conducts basic scientific research, applied research, technological development and prototyping. The laboratory's specialties include plasma physics, space physics, materials science, and tactical electronic warfare. NRL is one of the first US government scientific R&D laboratories, having opened in 1923 at the instigation of Thomas Edison, and is currently under the Office of Naval Research. As of 2016, NRL was a Navy Working Capital Fund activity, which means it is not a line-item in the US Federal Budget. Instead of direct funding from Congress, all costs, including overhead, were recovered through sponsor-funded research projects. NRL's research expenditures were approximately $1 billion per year. Research The Naval Research Laboratory conducts a wide variety of basic research and applied r ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Heterogeneous Element Processor

The Heterogeneous Element Processor (HEP) was introduced by Denelcor, Inc. in 1982. The HEP's architect was Burton Smith. The machine was designed to solve fluid dynamics problems for the Ballistic Research Laboratory. A HEP system, as the name implies, was pieced together from many heterogeneous components -- processors, data memory modules, and I/O modules. The components were connected via a switched network. A single processor, called a PEM, in a HEP system (up to sixteen PEMs could be connected) was rather unconventional; via a "program status word (PSW) queue," up to fifty processes could be maintained in hardware at once. The largest system ever delivered had 4 PEMs. The eight-stage instruction pipeline allowed instructions from eight different processes to proceed at once. In fact, only one instruction from a given process was allowed to be present in the pipeline at any point in time. Therefore, the full processor throughput of 10 MIPS could only be achieved when ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |