|

List Of AMD Accelerated Processing Unit Microprocessors

This is a list of microprocessors designed by AMD containing a 3D integrated graphics processing unit (iGPU), including those under the AMD APU (Accelerated Processing Unit) product series. Features overview Graphics API overview Desktop processors with 3D graphics APU or Radeon Graphics branded Lynx: "Llano" (2011) * Socket FM1 * CPU: K10 (also ''Husky'' or ''K10.5'') cores with an upgraded ''Stars'' architecture, no L3 cache ** L1 cache: 64 KB Data per core and 64 KB Instruction cache per core ** L2 cache: 512 KB on dual-core, 1 MB on tri- and quad-core models ** '' MMX, Enhanced 3DNow!, SSE, SSE2, SSE3, SSE4a, ABM, NX bit, AMD64, Cool'n'Quiet'', ''AMD-V'' * GPU: TeraScale 2 (Evergreen); all A and E series models feature ''Redwood''-class integrated graphics on die (''BeaverCreek'' for the dual-core variants and ''WinterPark'' for the quad-core variants). Sempron and Athlon models exclude integrated graphics. * List of embedded GPU's * Support for up to four ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Integrated Graphics Processing Unit

A graphics processing unit (GPU) is a specialized electronic circuit designed for digital image processing and to accelerate computer graphics, being present either as a discrete video card or embedded on motherboards, mobile phones, personal computers, workstations, and game consoles. GPUs were later found to be useful for non-graphic calculations involving embarrassingly parallel problems due to their parallel structure. The ability of GPUs to rapidly perform vast numbers of calculations has led to their adoption in diverse fields including artificial intelligence (AI) where they excel at handling data-intensive and computationally demanding tasks. Other non-graphical uses include the training of neural networks and cryptocurrency mining. History 1970s Arcade system boards have used specialized graphics circuits since the 1970s. In early video game hardware, RAM for frame buffers was expensive, so video chips composited data together as the display was being scanned out ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

DIMM

A DIMM (Dual In-line Memory Module) is a popular type of memory module used in computers. It is a printed circuit board with one or both sides (front and back) holding DRAM chips and pins. The vast majority of DIMMs are manufactured in compliance with JEDEC memory standards, although there are proprietary DIMMs. DIMMs come in a variety of speeds and capacities, and are generally one of two lengths: PC, which are , and laptop (SO-DIMM), which are about half the length at . History DIMMs (Dual In-line Memory Module) were a 1990s upgrade for SIMMs (Single In-line Memory Modules) as Intel P5-based Pentium processors began to gain market share. The Pentium had a 64-bit bus width, which would require SIMMs installed in matched pairs in order to populate the data bus. The processor would then access the two SIMMs in parallel. DIMMs were introduced to eliminate this disadvantage. The contacts on SIMMs on both sides are redundant, while DIMMs have separate electrical contacts o ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Thread (computing)

In computer science, a thread of execution is the smallest sequence of programmed instructions that can be managed independently by a scheduler, which is typically a part of the operating system. In many cases, a thread is a component of a process. The multiple threads of a given process may be executed concurrently (via multithreading capabilities), sharing resources such as memory, while different processes do not share these resources. In particular, the threads of a process share its executable code and the values of its dynamically allocated variables and non- thread-local global variables at any given time. The implementation of threads and processes differs between operating systems. History Threads made an early appearance under the name of "tasks" in IBM's batch processing operating system, OS/360, in 1967. It provided users with three available configurations of the OS/360 control system, of which Multiprogramming with a Variable Number of Tasks (MVT) ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Multi-core Processor

A multi-core processor (MCP) is a microprocessor on a single integrated circuit (IC) with two or more separate central processing units (CPUs), called ''cores'' to emphasize their multiplicity (for example, ''dual-core'' or ''quad-core''). Each core reads and executes Instruction set, program instructions, specifically ordinary Instruction set, CPU instructions (such as add, move data, and branch). However, the MCP can run instructions on separate cores at the same time, increasing overall speed for programs that support Multithreading (computer architecture), multithreading or other parallel computing techniques. Manufacturers typically integrate the cores onto a single IC Die (integrated circuit), die, known as a ''chip multiprocessor'' (CMP), or onto multiple dies in a single Chip carrier, chip package. As of 2024, the microprocessors used in almost all new personal computers are multi-core. A multi-core processor implements multiprocessing in a single physical package. Des ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Graphics Processing Unit

A graphics processing unit (GPU) is a specialized electronic circuit designed for digital image processing and to accelerate computer graphics, being present either as a discrete video card or embedded on motherboards, mobile phones, personal computers, workstations, and game consoles. GPUs were later found to be useful for non-graphic calculations involving embarrassingly parallel problems due to their parallel structure. The ability of GPUs to rapidly perform vast numbers of calculations has led to their adoption in diverse fields including artificial intelligence (AI) where they excel at handling data-intensive and computationally demanding tasks. Other non-graphical uses include the training of neural networks and cryptocurrency mining. History 1970s Arcade system boards have used specialized graphics circuits since the 1970s. In early video game hardware, RAM for frame buffers was expensive, so video chips composited data together as the display was being scann ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Central Processing Unit

A central processing unit (CPU), also called a central processor, main processor, or just processor, is the primary Processor (computing), processor in a given computer. Its electronic circuitry executes Instruction (computing), instructions of a computer program, such as arithmetic, logic, controlling, and input/output (I/O) operations. This role contrasts with that of external components, such as main memory and I/O circuitry, and specialized coprocessors such as graphics processing units (GPUs). The form, CPU design, design, and implementation of CPUs have changed over time, but their fundamental operation remains almost unchanged. Principal components of a CPU include the arithmetic–logic unit (ALU) that performs arithmetic operation, arithmetic and Bitwise operation, logic operations, processor registers that supply operands to the ALU and store the results of ALU operations, and a control unit that orchestrates the #Fetch, fetching (from memory), #Decode, decoding and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Stepping Level

In integrated circuits, the stepping level or revision level is a version number that refers to the introduction or revision of one or more photolithographic photomasks within the set of photomasks that is used to pattern an integrated circuit. The term originated from the name of the equipment ( "steppers") that exposes the photoresist to light. Integrated circuits have two primary classes of mask sets: firstly, "base" layers that are used to build the structures, such as transistors, that comprise circuit logic and, secondly, "metal" layers that connect the circuit logic. Typically, when an integrated circuit manufacturer such as Intel or AMD produces a new stepping (i.e. a revision to the masks), it is because it has found bugs in the logic, has made improvements to the design that permit faster processing, has found a way to increase yield or improve the "bin splits" (i.e. create faster transistors and thus faster CPUs), has improved maneuverability to more easily identify m ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

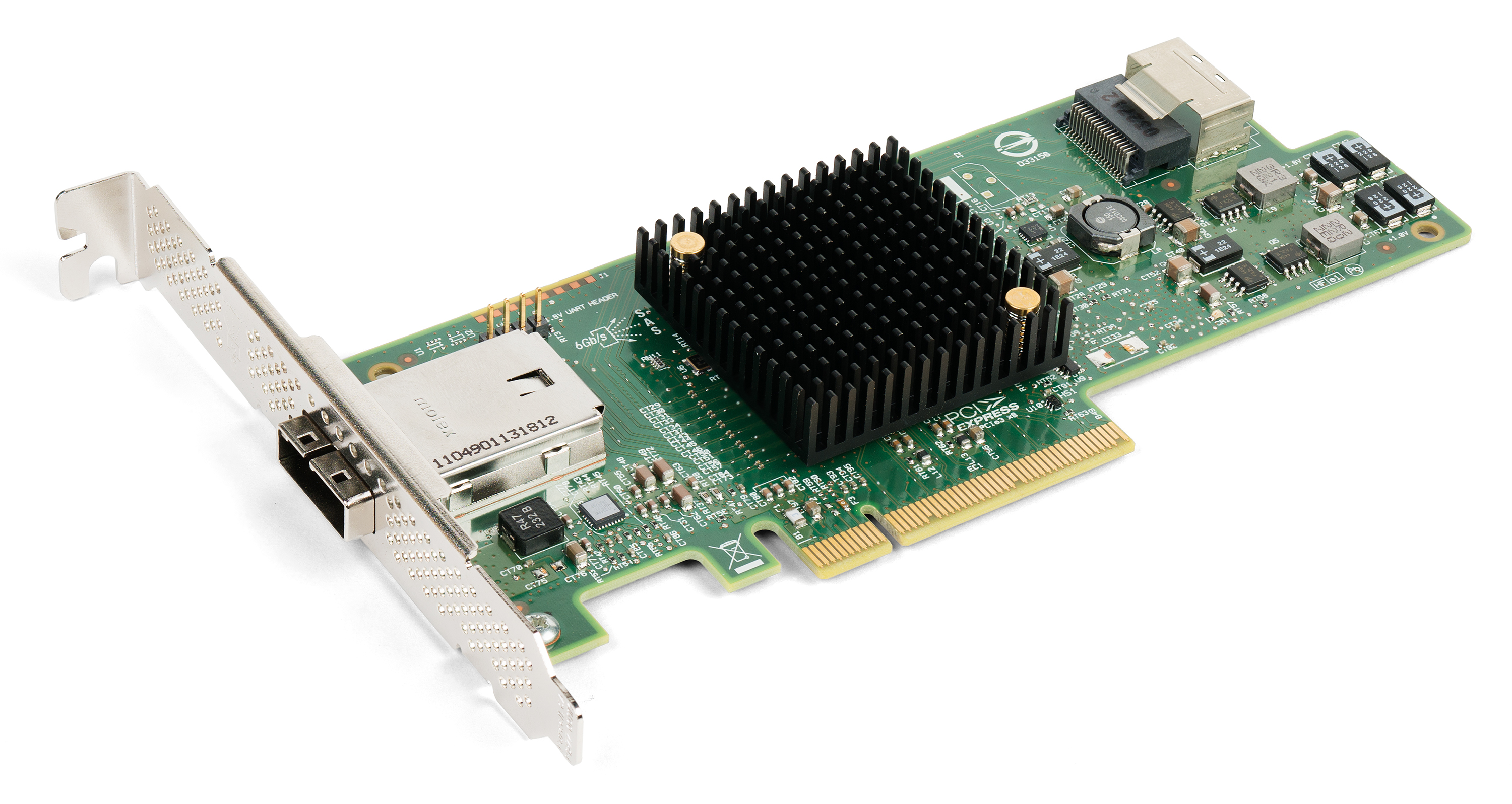

PCIE

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe, is a high-speed standard used to connect hardware components inside computers. It is designed to replace older expansion bus standards such as Peripheral Component Interconnect, PCI, PCI-X and Accelerated Graphics Port, AGP. Developed and maintained by the PCI-SIG (PCI Special Interest Group), PCIe is commonly used to connect graphics cards, sound cards, Wi-Fi and Ethernet adapters, and storage devices such as solid-state drives and hard disk drives. Compared to earlier standards, PCIe supports faster data transfer, uses fewer pins, takes up less space, and allows devices to be added or removed while the computer is running (hot swapping). It also includes better error detection and supports newer features like I/O virtualization for advanced computing needs. PCIe connections are made through "lanes," which are pairs of wires that send and receive data. Devices can use one or more lanes ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

UMI AMD

The Unified Media Interface (UMI) interconnect is the link between an AMD Accelerated Processing Unit (APU) and the FCH (Fusion Controller Hub). It is similar to Intel's DMI, and is based on PCI Express PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe, is a high-speed standard used to connect hardware components inside computers. It is designed to replace older expansion bus standards such as Peripher .... The Fusion Controller Hub is similar to the southbridge of earlier chipsets. References AMD technologies Computer buses {{computer-stub ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

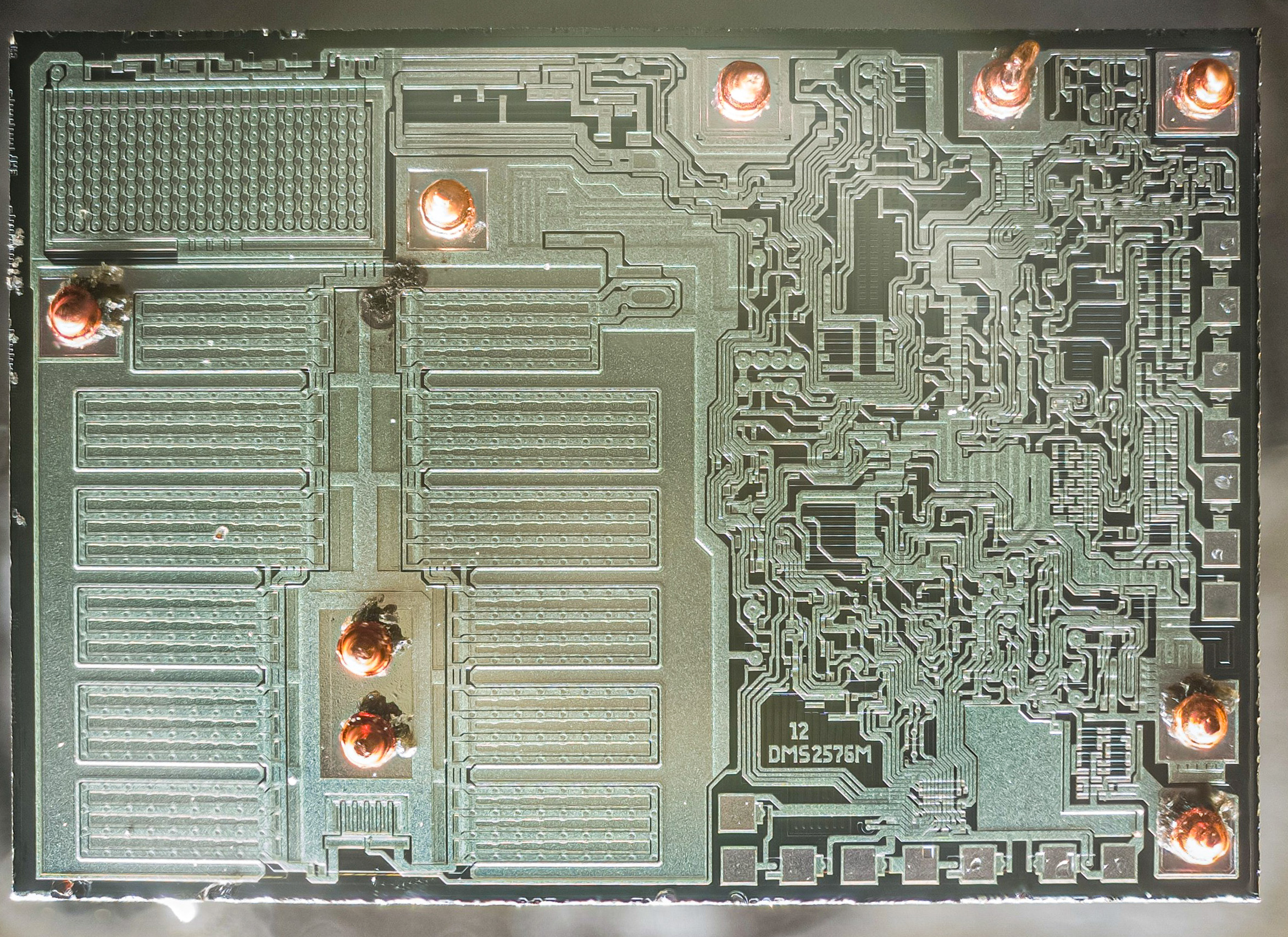

Die (integrated Circuit)

A die, in the context of integrated circuits, is a small block of semiconducting material on which a given functional circuit is Semiconductor fabrication, fabricated. Typically, integrated circuits are produced in large batches on a single wafer (electronics), wafer of electronic-grade Monocrystalline silicon, silicon (EGS) or other semiconductor (such as Gallium arsenide, GaAs) through processes such as photolithography. The wafer is cut (wafer dicing, diced) into many pieces, each containing one copy of the circuit. Each of these pieces is called a die. There are three commonly used plural forms: ''dice'', ''dies,'' and ''die''. To simplify handling and integration onto a printed circuit board, most dies are integrated circuit packaging, packaged in List of electronic component packaging types, various forms. Manufacturing process Most dies are composed of silicon and used for integrated circuits. The process begins with the production of Single crystal, monocrystalline sili ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Silicon On Insulator

In semiconductor manufacturing, silicon on insulator (SOI) technology is fabrication of silicon semiconductor devices in a layered silicon–insulator–silicon substrate, to reduce parasitic capacitance within the device, thereby improving performance. SOI-based devices differ from conventional silicon-built devices in that the silicon junction is above an electrical insulator, typically silicon dioxide or sapphire (these types of devices are called silicon on sapphire, or SOS). The choice of insulator depends largely on intended application, with sapphire being used for high-performance radio frequency (RF) and radiation-sensitive applications, and silicon dioxide for diminished short-channel effects in other microelectronics devices. The insulating layer and topmost silicon layer also vary widely with application. Industry need SOI technology is one of several manufacturing strategies to allow the continued miniaturization of microelectronic devices, colloquially referred to ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |