|

Goldmont

Goldmont is a microarchitecture for low-power Atom, Celeron and Pentium branded processors used in systems on a chip (SoCs) made by Intel. They allow only one thread per core. The ''Apollo Lake'' platform with 14 nm Goldmont core was unveiled at the Intel Developer Forum (IDF) in Shenzhen, China, April 2016. The Goldmont architecture borrows heavily from the Skylake Core processors, so it offers a more than 30 percent performance boost compared to the previous Braswell platform, and it can be used to implement power-efficient low-end devices including Cloudbooks, 2-in-1 netbooks, small PCs, IP cameras, and in-car entertainment systems. Design Goldmont is the 2nd generation out-of-order low-power Atom microarchitecture designed for the entry level desktop and notebook computers. Goldmont is built on the 14 nm manufacturing process and supports up to four cores for the consumer devices. It includes the Intel Gen9 graphics architecture introduced with the Skylake. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Goldmont Plus

Goldmont Plus is a microarchitecture for low-power Atom, Celeron and Pentium Silver branded processors used in systems on a chip (SoCs) made by Intel. The ''Gemini Lake'' platform with 14 nm Goldmont Plus core was officially launched on December 11, 2017. Intel launched the ''Gemini Lake Refresh'' platform on November 4, 2019. Design Goldmont Plus is an enhanced 2nd generation out-of-order low-power Atom microarchitecture designed for entry level desktop and notebook computers. Goldmont Plus is built on the 14 nm manufacturing process and supports up to four cores for the consumer devices. It includes the Intel Gen9 graphics architecture with improvements introduced with the Kaby Lake microarchitecture. The Goldmont Plus microarchitecture builds on the success of the Goldmont microarchitecture, and provides the following enhancements: * Widened previous generation Atom processor back-end pipeline to 4-wide allocation to 4-wide retire, while maintaining 3-wide fet ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel Atom

Intel Atom is the brand name for a line of IA-32 and x86-64 instruction set ultra-low-voltage processors by Intel Corporation designed to reduce electric consumption and power dissipation in comparison with ordinary processors of the Intel Core series. Atom is mainly used in netbooks, nettops, embedded applications ranging from health care to advanced robotics, mobile Internet devices (MIDs) and phones. The line was originally designed in 45 nm complementary metal–oxide–semiconductor (CMOS) technology and subsequent models, codenamed ''Cedar'', used a 32 nm process. The first generation of Atom processors are based on the Bonnell microarchitecture. On December 21, 2009, Intel announced the ''Pine Trail'' platform, including new Atom processor code-named ''Pineview'' (Atom N450), with total kit power consumption down 20%. On December 28, 2011, Intel updated the Atom line with the ''Cedar'' processors. In December 2012, Intel launched the 64-bit ''Centerton'' family of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

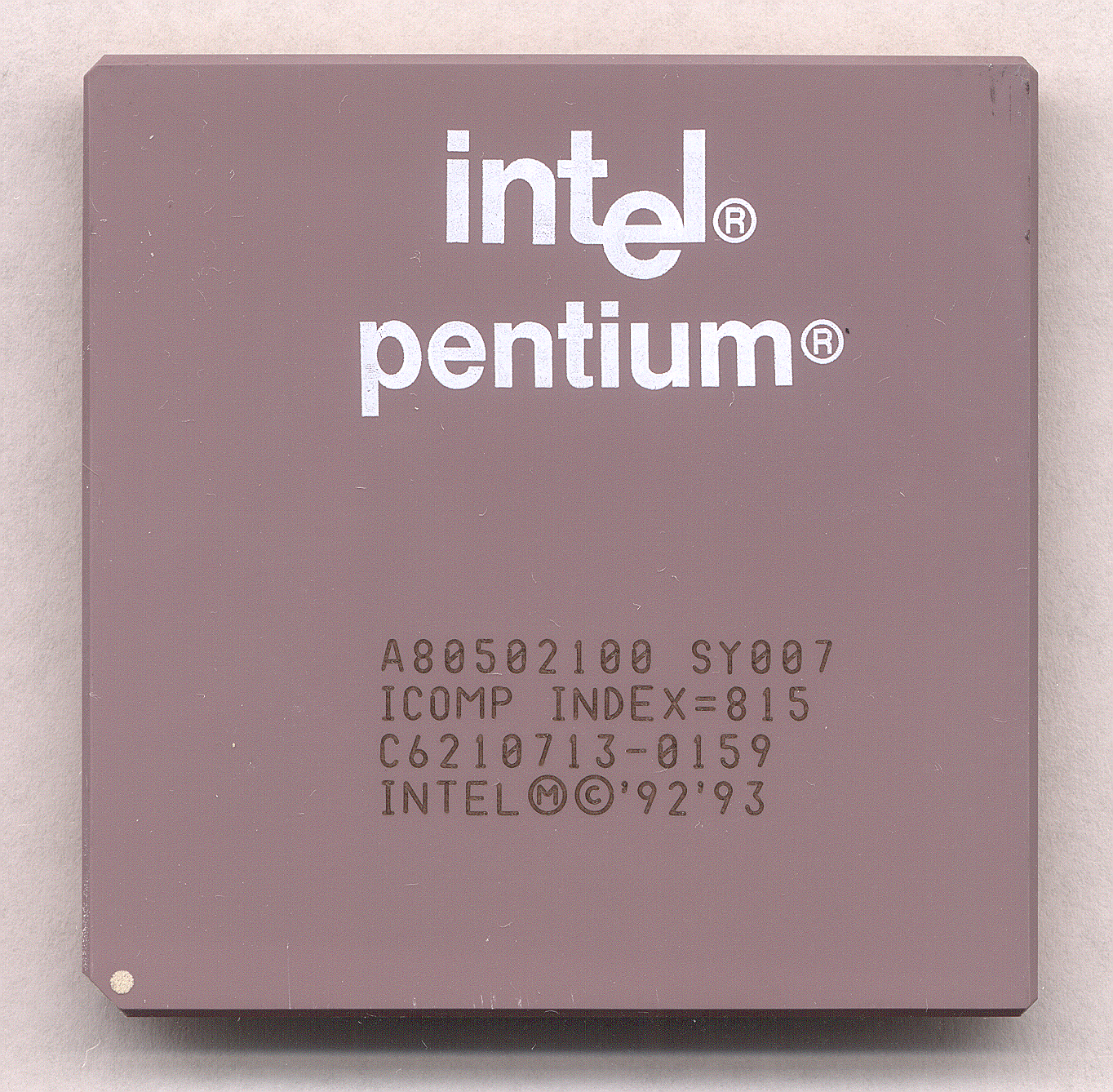

Pentium

Pentium is a brand used for a series of x86 architecture-compatible microprocessors produced by Intel. The original Pentium processor from which the brand took its name was first released on March 22, 1993. After that, the Pentium II and Pentium III were released. In their form , Pentium processors are considered entry-level products that Intel rates as "two stars", meaning that they are above the low-end Atom and Celeron series, but below the faster Intel Core lineup, and workstation/server Xeon series. , Pentium processors have little more than their name in common with earlier Pentiums, which were Intel's flagship processor for over a decade until the introduction of the Intel Core line in 2006. They are based on both the architecture used in Atom and that of Core processors. In the case of Atom architectures, Pentiums are the highest performance implementations of the architecture. Pentium processors with Core architectures prior to 2017 were distinguished from the fast ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Atom (system On Chip)

Atom is a system on a chip (SoC) platform designed for smartphones and tablet computers, launched by Intel in 2012. It is a continuation of the partnership announced by Intel and Google on September 13, 2011 to provide support for the Android operating system on Intel x86 processors. This range competes with existing SoCs developed for the smartphone and tablet market from companies such as Texas Instruments, Nvidia, Qualcomm and Samsung. Unlike these companies, which use ARM-based CPUs designed from the beginning to consume very low power, Intel has adapted the x86-based Intel Atom line of CPU developed for low power usage in netbooks, to even lower power usage. Since April 2012, several manufacturers have released Intel Atom-based tablets and phones as well as using the SoCs as a basis for other small form factor devices (e.g. mini PCs and stick PCs). In April 2016, Intel announced a major restructuring, including the cancellation of the SoFIA platform. It was reported by m ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SSE4

SSE4 (Streaming SIMD Extensions 4) is a SIMD CPU instruction set used in the Intel Core microarchitecture and AMD K10 (K8L). It was announced on September 27, 2006, at the Fall 2006 Intel Developer Forum, with vague details in a white paper; more precise details of 47 instructions became available at the Spring 2007 Intel Developer Forum in Beijing, in the presentation. SSE4 is fully compatible with software written for previous generations of Intel 64 and IA-32 architecture microprocessors. All existing software continues to run correctly without modification on microprocessors that incorporate SSE4, as well as in the presence of existing and new applications that incorporate SSE4. SSE4 subsets Intel SSE4 consists of 54 instructions. A subset consisting of 47 instructions, referred to as ''SSE4.1'' in some Intel documentation, is available in Penryn. Additionally, ''SSE4.2'', a second subset consisting of the 7 remaining instructions, is first available in Nehalem-based Core i7 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel SHA Extensions

Intel SHA Extensions are a set of extensions to the x86 instruction set architecture which support hardware acceleration of Secure Hash Algorithm (SHA) family. It was introduced in 2013. There are seven new SSE-based instructions, four supporting SHA-1 and three for SHA-256: * SHA1RNDS4, SHA1NEXTE, SHA1MSG1, SHA1MSG2 * SHA256RNDS2, SHA256MSG1, SHA256MSG2 x86 architecture processors Intel The following Intel processors support SHA instruction set: * Intel Goldmont (and later Atom microarchitectures) processors. * Intel Ice Lake (and later) processors. * Intel Rocket Lake (and later) processors. AMD Several AMD processors support SHA instruction set: * AMD Zen Zen ( zh, t=禪, p=Chán; ja, text= 禅, translit=zen; ko, text=선, translit=Seon; vi, text=Thiền) is a school of Mahayana Buddhism that originated in China during the Tang dynasty, known as the Chan School (''Chánzong'' 禪宗), and ... (and later) processors. References External links New Instr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AES Instruction Set

An Advanced Encryption Standard instruction set is now integrated into many processors. The purpose of the instruction set is to improve the speed and security of applications performing encryption and decryption using Advanced Encryption Standard (AES). They are often implemented as instructions implementing a single round of AES along with a special version for the last round which has a slightly different method. The side channel attack surface of AES is reduced when implemented in an instruction set, compared to when AES is implemented in software only. x86 architecture processors AES-NI (or the Intel Advanced Encryption Standard New Instructions; AES-NI) was the first major implementation. AES-NI is an extension to the x86 instruction set architecture for microprocessors from Intel and AMD proposed by Intel in March 2008. Instructions Intel The following Intel processors support the AES-NI instruction set: * Westmere based processors, specifically: ** Westmere ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

CLMUL Instruction Set

Carry-less Multiplication (CLMUL) is an extension to the x86 instruction set used by microprocessors from Intel and AMD which was proposed by Intel in March 2008 and made available in the Intel Westmere processors announced in early 2010. Mathematically, the instruction implements multiplication of polynomials over the finite field GF(2) where the bitstring a_0a_1\ldots a_ represents the polynomial a_0 + a_1X + a_2X^2 + \cdots + a_X^. The CLMUL instruction also allows a more efficient implementation of the closely related multiplication of larger finite fields GF(2''k'') than the traditional instruction set. One use of these instructions is to improve the speed of applications doing block cipher encryption in Galois/Counter Mode, which depends on finite field GF(2''k'') multiplication. Another application is the fast calculation of CRC values, including those used to implement the LZ77 sliding window DEFLATE algorithm in zlib and pngcrush. ARMv8 also has a version of CLMUL. SP ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Braswell (SOC)

Silvermont is a microarchitecture for low-power Atom, Celeron and Pentium branded processors used in systems on a chip (SoCs) made by Intel. Silvermont forms the basis for a total of four SoC families: * ''Merrifield'' and ''Moorefield'' consumer SoCs intended for smartphones * ''Bay Trail'' consumer SoCs aimed at tablets, hybrid devices, netbooks, nettops, and embedded/automotive systems * ''Avoton'' SoCs for micro-servers and storage devices * ''Rangeley'' SoCs targeting network and communication infrastructure. Silvermont is the successor of the Bonnell, using a newer 22 nm process (previously introduced with Ivy Bridge) and a new microarchitecture, replacing Hyper Threading with out-of-order execution. Silvermont was announced to news media on May 6, 2013, at Intel's headquarters at Santa Clara, California. Intel had repeatedly said the first Bay Trail devices would be available during the Holiday 2013 timeframe, while leaked slides showed that the release windo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Airmont Microarchitecture

Silvermont is a microarchitecture for low-power Atom, Celeron and Pentium branded processors used in systems on a chip (SoCs) made by Intel. Silvermont forms the basis for a total of four SoC families: * ''Merrifield'' and ''Moorefield'' consumer SoCs intended for smartphones * ''Bay Trail'' consumer SoCs aimed at tablets, hybrid devices, netbooks, nettops, and embedded/automotive systems * ''Avoton'' SoCs for micro-servers and storage devices * ''Rangeley'' SoCs targeting network and communication infrastructure. Silvermont is the successor of the Bonnell, using a newer 22 nm process (previously introduced with Ivy Bridge) and a new microarchitecture, replacing Hyper Threading with out-of-order execution. Silvermont was announced to news media on May 6, 2013, at Intel's headquarters at Santa Clara, California. Intel had repeatedly said the first Bay Trail devices would be available during the Holiday 2013 timeframe, while leaked slides showed that the release windo ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Microarchitecture

In computer engineering, microarchitecture, also called computer organization and sometimes abbreviated as µarch or uarch, is the way a given instruction set architecture (ISA) is implemented in a particular processor. A given ISA may be implemented with different microarchitectures; implementations may vary due to different goals of a given design or due to shifts in technology. Computer architecture is the combination of microarchitecture and instruction set architecture. Relation to instruction set architecture The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the instructions, execution model, processor registers, address and data formats among other things. The microarchitecture includes the constituent parts of the processor and how these interconnect and interoperate to implement the ISA. The microarchitecture of a machine is usually represented as (more or less detai ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

14 Nanometer

The 14 nm process refers to the MOSFET technology node that is the successor to the 22nm (or 20nm) node. The 14nm was so named by the International Technology Roadmap for Semiconductors (ITRS). Until about 2011, the node following 22nm was expected to be 16nm. All 14nm nodes use FinFET (fin field-effect transistor) technology, a type of multi-gate MOSFET technology that is a non-planar evolution of planar silicon CMOS technology. Samsung Electronics taped out a 14 nm chip in 2014, before manufacturing 10 nm class NAND flash chips in 2013. The same year, SK Hynix began mass-production of 16nm NAND flash, and TSMC began 16nm FinFET production. The following year, Intel began shipping 14nm scale devices to consumers. History Background The basis for sub-20nm fabrication is the FinFET (Fin field-effect transistor), an evolution of the MOSFET transistor. FinFET technology was pioneered by Digh Hisamoto and his team of researchers at Hitachi Central Research Laboratory in ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |