|

GDDR5

Graphics Double Data Rate 5 Synchronous Dynamic Random-Access Memory (GDDR5 SDRAM) is a type of synchronous graphics random-access memory (SGRAM) with a high bandwidth ("double data rate") interface designed for use in graphics cards, game consoles, and high-performance computing. It is a type of GDDR SDRAM (graphics DDR SDRAM). Overview Like its predecessor, GDDR4, GDDR5 is based on DDR3 SDRAM memory, which has double the data lines compared to DDR2 SDRAM. GDDR5 also uses 8-bit wide prefetch buffers similar to GDDR4 and DDR3 SDRAM. GDDR5 SGRAM conforms to the standards which were set out in the GDDR5 specification by the JEDEC. SGRAM is single-ported. However, it can open two memory pages at once, which simulates the dual-port nature of other VRAM technologies. It uses an 8N- prefetch architecture and DDR interface to achieve high performance operation and can be configured to operate in ×32 mode or ×16 (clamshell) mode which is detected during device initializati ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Nvidia GeForce GTX 980 Ti

The GeForce 900 series is a family of graphics processing units developed by Nvidia, succeeding the GeForce 700 series and serving as the high-end introduction to the Maxwell microarchitecture, named after James Clerk Maxwell. They were produced with TSMC's 28 nm process. With Maxwell, the successor to Kepler, Nvidia expected three major outcomes: improved graphics capabilities, simplified programming, and better energy efficiency compared to the GeForce 700 series and GeForce 600 series. Maxwell was announced in September 2010, with the first Maxwell-based GeForce consumer-class products released in early 2014. Architecture First generation Maxwell (GM10x) First generation Maxwell GM107/GM108 were released as GeForce GTX 745, GTX 750/750 Ti and GTX 850M/860M (GM107) and GT 830M/840M (GM108). These new chips provide few consumer-facing additional features; Nvidia instead focused on power efficiency. Nvidia increased the amount of L2 cache from 256 KiB on GK ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GDDR SDRAM

Graphics DDR SDRAM (GDDR SDRAM) is a type of synchronous dynamic random-access memory (SDRAM) specifically designed for applications requiring high bandwidth, e.g. graphics processing units (GPUs). GDDR SDRAM is distinct from the more widely known types of DDR SDRAM, such as DDR4 and DDR5, although they share some of the same features—including double data rate (DDR) data transfers. , GDDR SDRAM has been succeeded by GDDR2, GDDR3, GDDR4, GDDR5, GDDR5X, GDDR6, GDDR6X, GDDR6W and GDDR7. Generations File:ATI Radeon X1300 256MB - Hynix HY5DU561622CTP-5-5390.jpg, Hynix GDDR SDRAM File:SAMSUNG@QDDR3-SDRAM@256MBit@K5J55323QF-GC16 Stack-DSC01234-DSC01284 - ZS-retouched.jpg, A Samsung GDDR3 256MBit package File:Sapphire Ultimate HD 4670 512MB - Qimonda HYB18H512321BF-10-93577.jpg, A 512 MBit Qimonda GDDR3 SDRAM package File:SAMSUNG@QDDR3-SDRAM@256MBit@K5J55323QF-GC16 Stack-DSC01340-DSC01367 - ZS-retouched.jpg, Inside a Samsung GDDR3 256MBit package DDR SGRAM GDDR was init ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Synchronous Dynamic Random-access Memory

Synchronous dynamic random-access memory (synchronous dynamic RAM or SDRAM) is any DRAM where the operation of its external pin interface is coordinated by an externally supplied clock signal. DRAM integrated circuits (ICs) produced from the early 1970s to the early 1990s used an ''asynchronous'' interface, in which input control signals have a direct effect on internal functions delayed only by the trip across its semiconductor pathways. SDRAM has a ''synchronous'' interface, whereby changes on control inputs are recognised after a rising edge of its clock input. In SDRAM families standardized by JEDEC, the clock signal controls the stepping of an internal finite-state machine that responds to incoming commands. These commands can be pipelined to improve performance, with previously started operations completing while new commands are received. The memory is divided into several equally sized but independent sections called ''banks'', allowing the device to operate on a memor ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Prefetch Buffer

Synchronous dynamic random-access memory (synchronous dynamic RAM or SDRAM) is any Dynamic random-access memory, DRAM where the operation of its external pin interface is coordinated by an externally supplied clock signal. DRAM integrated circuits (ICs) produced from the early 1970s to the early 1990s used an ''asynchronous'' interface, in which input control signals have a direct effect on internal functions delayed only by the trip across its semiconductor pathways. SDRAM has a ''synchronous'' interface, whereby changes on control inputs are recognised after a rising edge of its clock input. In SDRAM families standardized by JEDEC, the clock signal controls the stepping of an internal finite-state machine that responds to incoming commands. These commands can be pipelined to improve performance, with previously started operations completing while new commands are received. The memory is divided into several equally sized but independent sections called ''Memory bank, banks'', a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GDDR6 SDRAM

Graphics Double Data Rate 6 Synchronous Dynamic Random-Access Memory (GDDR6 SDRAM) is a type of synchronous graphics random-access memory (SGRAM) with a high bandwidth, "double data rate" interface, designed for use in graphics cards, game consoles, and high-performance computing. It is a type of GDDR SDRAM (graphics DDR SDRAM), and is the successor to GDDR5. Just like GDDR5X it uses QDR (quad data rate) in reference to the write command clock (WCK) and ODR (Octal Data Rate) in reference to the command clock (CK). Overview The finalized specification was published by JEDEC in July 2017. GDDR6 offers increased per-pin bandwidth (up to 16 Gbit/s) and lower operating voltages (1.35 V), increasing performance and decreasing power consumption relative to GDDR5X. Commercial implementation At Hot Chips 2016, Samsung announced GDDR6 as the successor of GDDR5X. Samsung later announced that the first products would be 16 Gbit/s, 1.35 V chips. In January 2018, Sam ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

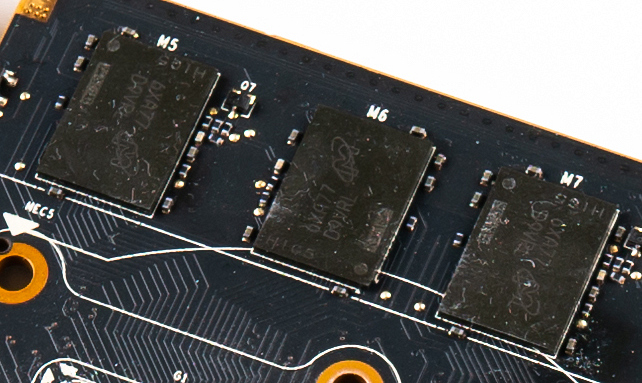

Video Card

A graphics card (also called a video card, display card, graphics accelerator, graphics adapter, VGA card/VGA, video adapter, display adapter, or colloquially GPU) is a computer expansion card that generates a feed of graphics output to a display device such as a computer monitor, monitor. Graphics cards are sometimes called ''discrete'' or ''dedicated'' graphics cards to emphasize their distinction to an graphics processing unit#Integrated graphics processing unit, integrated graphics processor on the motherboard or the central processing unit (CPU). A graphics processing unit (GPU) that performs the necessary computations is the main component in a graphics card, but the acronym "GPU" is sometimes also used to refer to the graphics card as a whole erroneously. Most graphics cards are not limited to simple display output. The graphics processing unit can be used for additional processing, which reduces the load from the CPU. Additionally, computing platforms such as OpenCL and C ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

GDDR4 SDRAM

GDDR4 SDRAM, an abbreviation for Graphics Double Data Rate 4 Synchronous Dynamic Random-Access Memory, is a type of graphics card memory (SGRAM) specified by the JEDEC Semiconductor Memory Standard. It is a rival medium to Rambus's XDR DRAM. GDDR4 is based on DDR3 SDRAM technology and was intended to replace the DDR2-based GDDR3, but it ended up being replaced by GDDR5 within a year. History * On October 26, 2005, Samsung announced that it developed the first GDDR4 memory, a 256- Mbit chip running at 2.5 Gbit/s. Samsung also revealed plans to sample and mass-produce GDDR4 SDRAM rated at 2.8 Gbit/s per pin. * In 2005, Hynix developed the first 512-Mbit GDDR4 memory chip. * On February 14, 2006, Samsung announced the development of 32-bit 512-Mbit GDDR4 SDRAM capable of transferring 3.2 Gbit/s per pin, or 12.8 GB/s for the module. * On July 5, 2006, Samsung announced the mass-production of 32-bit 512-Mbit GDDR4 SDRAM rated at 2.4 Gbit/s per pin, or 9.6& ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Qimonda

Qimonda Aktiengesellschaft, AG ( ) was a German DRAM, memory company split out of Infineon Technologies (itself a spun off business unit of Siemens AG) on 1 May 2006 to form at the time the second largest DRAM company worldwide, according to the industry research firm Gartner Dataquest. It was a patent licensing firm until Micron and others purchased its patents. Headquartered in Munich, Qimonda was a Wafer (electronics)#Standard_wafer_sizes, 300 mm manufacturer and was one of the top suppliers of DRAM products for the personal computer, PC and server (computing), server markets. Infineon still controls a 77.5% stake, which it has written down (2008). Infineon was on record as having the aim of divesting itself of this stake, with the purpose of becoming a minority stakeholder in 2009. The company has issued 42 million American depositary receipt, ADR shares, each ADR share representing one ordinary share in Qimonda. At its height in 2007, Qimonda employed approximately 13,50 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Double Data Rate

In computing, double data rate (DDR) describes a computer bus that transfers data on both the rising and falling edges of the clock signal and hence doubles the memory bandwidth by transferring data twice per clock cycle. This is also known as double pumped, dual-pumped, and double transition. The term toggle mode is used in the context of NAND flash memory. Overview The simplest way to design a clocked electronic circuit is to make it perform one transfer per full cycle (rise and fall) of a clock signal. This, however, requires that the clock signal changes twice per transfer, while the data lines change at most once per transfer. When operating at a high bandwidth, signal integrity limitations constrain the clock frequency. By using both edges of the clock, the data signals operate with the same limiting frequency, thereby doubling the data transmission rate. This technique has been used for microprocessor front-side busses, Ultra-3 SCSI, expansion buses ( AGP, PCI ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |