|

Elastic Interface Bus

Elastic interface buses, abbreviated as EI bus connections, can be generalized as bus connections which are high speed interfaces that send clock signals with data. Description The data bits that are sent through EI bus connections are aligned to the clock so that they latch to the data at the high speeds. EI bus connections require that the net topology and timing characteristics for each net on the bus are at least similar to each other in order to make lining up the edges of the data to the clock signals possible. In this environment, re-working connections in the connection module was not easily possible because all nets needed to have similar topology and timing characteristics. This increased the difficulty of a re-work solution or made it impossible and increased the modules that needed to be scrapped as unusable. Repair Elastic Interface repair involves a spare wire that is built into the bus interface in the connection module that has the same topology and characteristic ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Bus (computing)

In computer architecture, a bus (shortened form of the Latin ''omnibus'', and historically also called data highway or databus) is a communication system that transfers data between components inside a computer, or between computers. This expression covers all related hardware components (wire, optical fiber, etc.) and software, including communication protocols. Early computer buses were parallel electrical wires with multiple hardware connections, but the term is now used for any physical arrangement that provides the same logical function as a parallel electrical busbar. Modern computer buses can use both parallel and bit serial connections, and can be wired in either a multidrop (electrical parallel) or daisy chain topology, or connected by switched hubs, as in the case of Universal Serial Bus (USB). Background and nomenclature Computer systems generally consist of three main parts: * The central processing unit (CPU) that processes data, * The memory that holds the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

POWER6

The POWER6 is a microprocessor developed by IBM that implemented the Power ISA v.2.03. When it became available in systems in 2007, it succeeded the POWER5+ as IBM's flagship Power microprocessor. It is claimed to be part of the eCLipz project, said to have a goal of converging IBM's server hardware where practical (hence "ipz" in the acronym: iSeries, pSeries, and zSeries). History POWER6 was described at the International Solid-State Circuits Conference (ISSCC) in February 2006, and additional details were added at the Microprocessor Forum in October 2006 and at the next ISSCC in February 2007. It was formally announced on May 21, 2007. It was released on June 8, 2007 at speeds of 3.5, 4.2 and 4.7 GHz, but the company has noted prototypes have reached 6 GHz. POWER6 reached first silicon in the middle of 2005, and was bumped to 5.0 GHz in May 2008 with the introduction of the P595. Description The POWER6 is a dual-core processor. Each core is capable ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

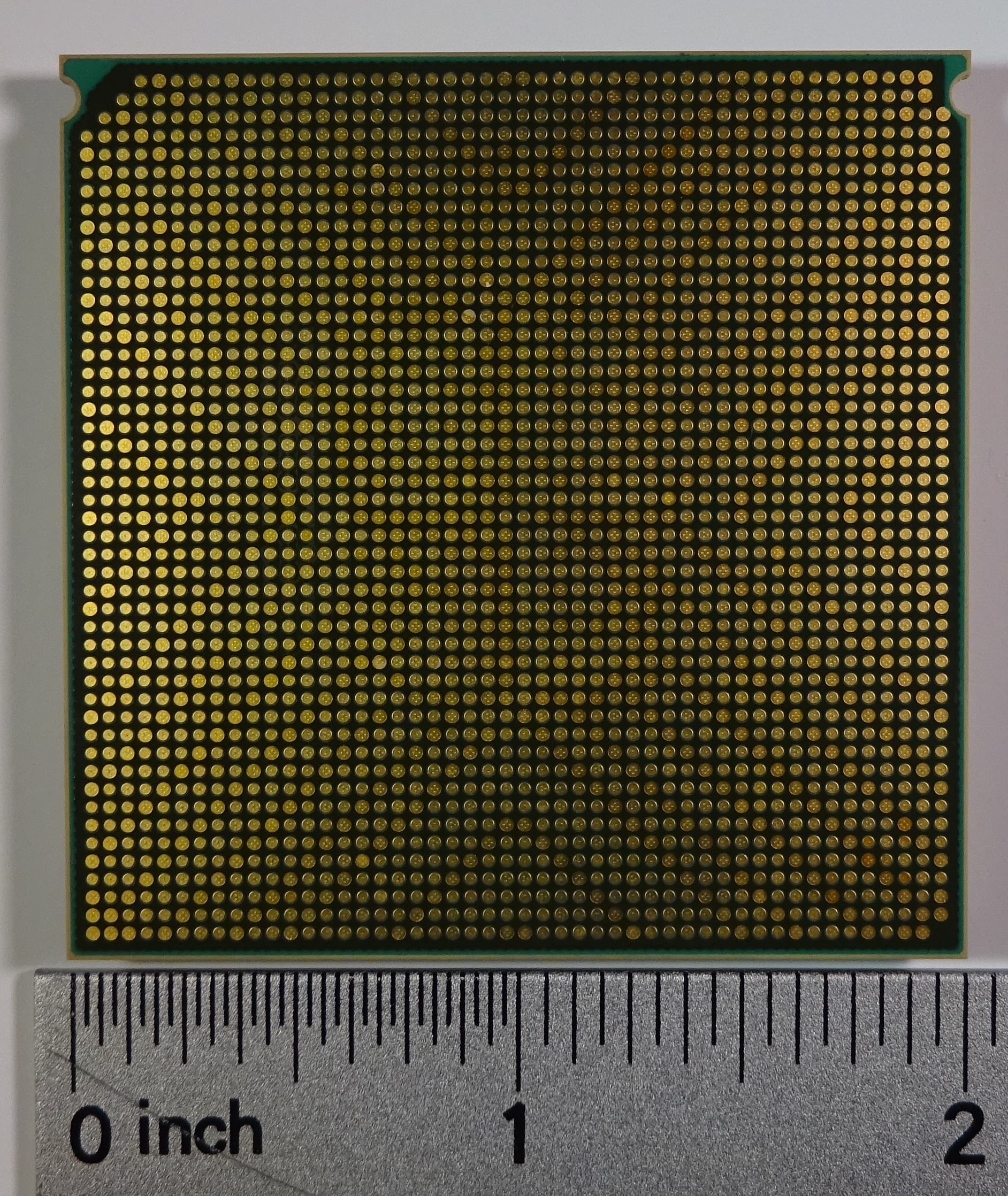

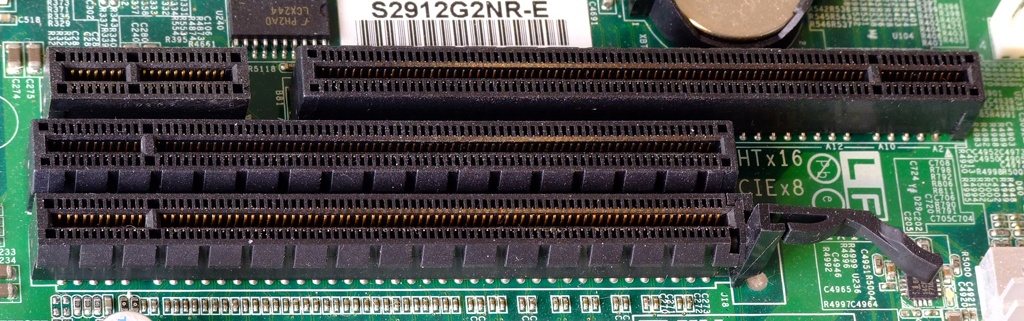

HyperTransport

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/ parallel high- bandwidth, low- latency point-to-point link that was introduced on April 2, 2001. The HyperTransport Consortium is in charge of promoting and developing HyperTransport technology. HyperTransport is best known as the system bus architecture of AMD central processing units (CPUs) from Athlon 64 through AMD FX and the associated motherboard chipsets. HyperTransport has also been used by IBM and Apple for the Power Mac G5 machines, as well as a number of modern MIPS systems. The current specification HTX 3.1 remained competitive for 2014 high-speed (2666 and 3200 MT/s or about 10.4 GB/s and 12.8 GB/s) DDR4 RAM and slower (around 1 GB/similar to high end Solid-state drive#Standard card form factors, PCIe SSDs ULLtraDIMM flash RAM) technology—a wider range of RAM speeds on a comm ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Mai Logic

Mai, or MAI, may refer to: Names * Mai (Chinese surname) * Mai (Vietnamese surname) * Mai (name) * Mai (singer), J-Pop singer * Iris Mai (born 1962), German chess master Places * Chiang Mai, largest city in northern Thailand * Ma-i, a pre-Hispanic Philippine state * Mai, Non Sung, Thailand Organisations * Manufacturers Association of Israel, an Israeli business organization * Marina Abramović Institute, a performance art organization * Market for Alternative Investment, a stock market for small/medium enterprises in Thailand * Montreal Arts Interculturels, a multidisciplinary cultural organization in Montreal, Canada * Moscow Aviation Institute, an engineering and aviation university in Russia * Motorsports Association of India, the FIA arm of Indian Motorsports Science and Technology * Machine augmented intelligence, use of technology to amplify and empower human thought and consciousness * Mean annual increment, a measure of the average growth per year a tree or stand of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM A2

The IBM A2 is an open source massively multicore capable and multithreaded 64-bit Power ISA processor core designed by IBM using the Power ISA v.2.06 specification. Versions of processors based on the A2 core range from a 2.3 GHz version with 16 cores consuming 65 W to a less powerful, four core version, consuming 20 W at 1.4 GHz. Design The A2 core is a processor core designed for customization and embedded use in system on chip-devices, and was developed following IBM's game console processor designs, the Xbox 360-processor and Cell processor for the PlayStation 3. A2I A2I is a 4-way simultaneous multithreaded core which implements the 64-bit Power ISA v.2.06 Book III-E embedded platform specification with support for the embedded hypervisor features. It was designed for implementations with many cores and focusing on high throughput and many simultaneous threads. A2I was written in VHDL. The core has 4×32 64-bit general purpose registers (GPR) w ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

POWER7

POWER7 is a family of superscalar multi-core microprocessors based on the Power ISA 2.06 instruction set architecture released in 2010 that succeeded the POWER6 and POWER6+. POWER7 was developed by IBM at several sites including IBM's Rochester, MN; Austin, TX; Essex Junction, VT; T. J. Watson Research Center, NY; Bromont, QC and IBM Deutschland Research & Development GmbH, Böblingen, Germany laboratories. IBM announced servers based on POWER7 on 8 February 2010. History IBM won a $244 million DARPA contract in November 2006 to develop a petascale supercomputer architecture before the end of 2010 in the HPCS project. The contract also states that the architecture shall be available commercially. IBM's proposal, PERCS (Productive, Easy-to-use, Reliable Computer System), which won them the contract, is based on the POWER7 processor, AIX operating system and General Parallel File System. One feature that IBM and DARPA collaborated on is modifying the addressing a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM Z10 (microprocessor)

The z10 is a microprocessor chip made by IBM for their System z10 mainframe computers, released February 26, 2008. It was called "z6" during development. Description The processor implements the CISC z/Architecture and has four cores. Each core has a 64 KB L1 instruction cache, a 128 KB L1 data cache and a 3 MB L2 cache (called the L1.5 cache by IBM). Finally, there is a 24 MB shared L3 cache (referred to as the L2 cache by IBM). The chip measures 21.7×20.0 mm and consists of 993 million transistors fabricated in IBM's 65 nm SOI fabrication process (CMOS 11S), supporting speeds of 4.4 GHz and above – more than twice the clock speed as former mainframes – with a 15 FO4 cycle. Each z10 chip has two 48 GB/s (48 billion bytes per second) SMP hub ports, four 13 GB/s memory ports, two 17 GB/s I/O ports, and 8765 contacts. The z10 processor was co-developed with and shares many design traits with the POWER6 processor, such as fabrication technology, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM System Z9

IBM System z9 is a line of IBM mainframe computers. The first models were available on September 16, 2005. The System z9 also marks the end of the previously used eServer zSeries naming convention. It was also the last mainframe computer that NASA ever used. Background System z9 is a mainframe using the z/Architecture, previously known as ESAME. z/Architecture is a 64-bit architecture which replaces the previous 31-bit-addressing/32-bit-data ESA/390 architecture while remaining completely compatible with it as well as the older 24-bit-addressing/32-bit-data System/360 architecture. The primary advantage of this arrangement is that memory intensive applications like DB2 are no longer bounded by 31-bit memory restrictions while older applications can run without modifications. Name change With the announcement of the System z9 Business Class server, IBM has renamed the System z9 109 as the System z9 Enterprise Class server. IBM documentation abbreviates them as the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Clock Signal

In electronics and especially synchronous digital circuits, a clock signal (historically also known as ''logic beat'') oscillates between a high and a low state and is used like a metronome to coordinate actions of digital circuits. A clock signal is produced by a clock generator. Although more complex arrangements are used, the most common clock signal is in the form of a square wave with a 50% duty cycle, usually with a fixed, constant frequency. Circuits using the clock signal for synchronization may become active at either the rising edge, falling edge, or, in the case of double data rate, both in the rising and in the falling edges of the clock cycle. Digital circuits Most integrated circuits (ICs) of sufficient complexity use a clock signal in order to synchronize different parts of the circuit, cycling at a rate slower than the worst-case internal propagation delays. In some cases, more than one clock cycle is required to perform a predictable action. As ICs bec ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IBM System Z

IBM Z is a family name used by IBM for all of its z/Architecture mainframe computers. In July 2017, with another generation of products, the official family was changed to IBM Z from IBM z Systems; the IBM Z family now includes the newest model, the IBM z16, as well as the z15, the z14, and the z13 (released under the IBM z Systems/IBM System z names), the IBM zEnterprise models (in common use the zEC12 and z196), the IBM System z10 models (in common use the z10 EC), the IBM System z9 models (in common use the z9EC) and ''IBM eServer zSeries'' models (in common use refers only to the z900 and z990 generations of mainframe). Architecture The ''zSeries,'' ''zEnterprise,'' ''System z'' and ''IBM Z'' families were named for their availability – ''z'' stands for zero downtime. The systems are built with spare components capable of hot failovers to ensure continuous operations. The IBM Z family maintains full backward compatibility. In effect, current systems are the direct, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |