|

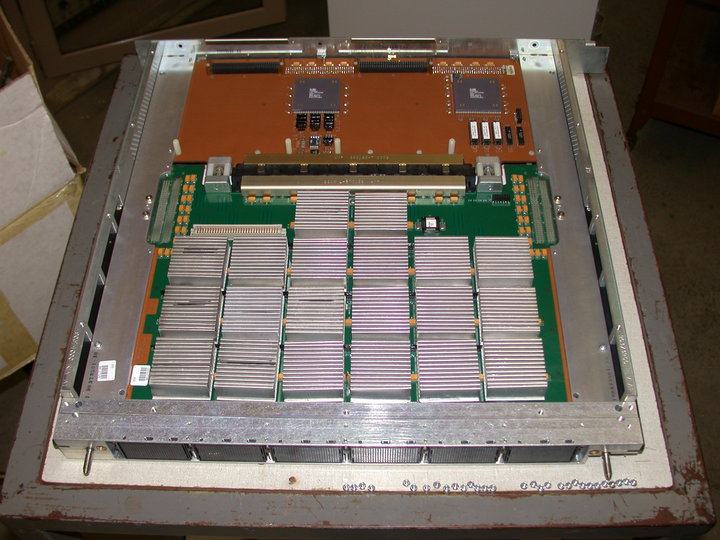

Cray SV1

The Cray SV1 is a vector processor supercomputer from the Cray Research division of Silicon Graphics introduced in 1998. The SV1 has since been succeeded by the Cray X1 and X1E vector supercomputers. Like its predecessor, the Cray J90, the SV1 used CMOS processors, which lowered the cost of the system, and allowed the computer to be air-cooled. The SV1 was backwards compatible with J90 and Y-MP software, and ran the same UNIX-derived UNICOS operating system. The SV1 used Cray floating point representation, not the IEEE 754 floating point format used on the Cray T3E and some Cray T90 systems. Unlike earlier Cray designs, the SV1 included a vector cache. It also introduced a feature called multi-streaming, in which one processor from each of four processor boards work together to form a virtual processor with four times the performance. The SV1 processor was clocked at 300 MHz. Later variants of the SV1, the SV1e and SV1ex, ran at 500 MHz, the latter also having faster memory and sup ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Vector Processor

In computing, a vector processor or array processor is a central processing unit (CPU) that implements an instruction set where its instructions are designed to operate efficiently and effectively on large one-dimensional arrays of data called ''vectors''. This is in contrast to scalar processors, whose instructions operate on single data items only, and in contrast to some of those same scalar processors having additional single instruction, multiple data (SIMD) or SWAR Arithmetic Units. Vector processors can greatly improve performance on certain workloads, notably numerical simulation and similar tasks. Vector processing techniques also operate in video-game console hardware and in graphics accelerators. Vector machines appeared in the early 1970s and dominated supercomputer design through the 1970s into the 1990s, notably the various Cray platforms. The rapid fall in the price-to-performance ratio of conventional microprocessor designs led to a decline in vector supercom ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cray T3E

The Cray T3E was Cray Research's second-generation massively parallel supercomputer architecture, launched in late November 1995. The first T3E was installed at the Pittsburgh Supercomputing Center in 1996. Like the previous Cray T3D, it was a fully distributed memory machine using a 3D torus topology interconnection network. The T3E initially used the DEC Alpha 21164 (EV5) microprocessor and was designed to scale from 8 to 2,176 ''Processing Elements'' (PEs). Each PE had between 64 MB and 2 GB of DRAM and a 6-way interconnect router with a payload bandwidth of 480 MB/s in each direction. Unlike many other MPP systems, including the T3D, the T3E was fully self-hosted and ran the UNICOS/mk distributed operating system with a ''GigaRing'' I/O subsystem integrated into the torus for network, disk and tape I/O. The original T3E (retrospectively known as the T3E-600) had a 300 MHz processor clock. Later variants, using the faster 21164A (EV56) processor, comprised the T3E-900 (4 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Teraflops

In computing, floating point operations per second (FLOPS, flops or flop/s) is a measure of computer performance, useful in fields of scientific computations that require floating-point calculations. For such cases, it is a more accurate measure than measuring instructions per second. Floating-point arithmetic Floating-point arithmetic is needed for very large or very small real numbers, or computations that require a large dynamic range. Floating-point representation is similar to scientific notation, except everything is carried out in base two, rather than base ten. The encoding scheme stores the sign, the exponent (in base two for Cray and VAX, base two or ten for IEEE floating point formats, and base 16 for IBM Floating Point Architecture) and the significand (number after the radix point). While several similar formats are in use, the most common is ANSI/IEEE Std. 754-1985. This standard defines the format for 32-bit numbers called ''single precision'', as well as 64-b ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SCSI

Small Computer System Interface (SCSI, ) is a set of standards for physically connecting and transferring data between computers and peripheral devices. The SCSI standards define commands, protocols, electrical, optical and logical interfaces. The SCSI standard defines command sets for specific peripheral device types; the presence of "unknown" as one of these types means that in theory it can be used as an interface to almost any device, but the standard is highly pragmatic and addressed toward commercial requirements. The initial Parallel SCSI was most commonly used for hard disk drives and tape drives, but it can connect a wide range of other devices, including scanners and CD drives, although not all controllers can handle all devices. The ancestral SCSI standard, X3.131-1986, generally referred to as SCSI-1, was published by the X3T9 technical committee of the American National Standards Institute (ANSI) in 1986. SCSI-2 was published in August 1990 as X3.T9.2/86-109 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Ethernet

Ethernet () is a family of wired computer networking technologies commonly used in local area networks (LAN), metropolitan area networks (MAN) and wide area networks (WAN). It was commercially introduced in 1980 and first standardized in 1983 as IEEE 802.3. Ethernet has since been refined to support higher bit rates, a greater number of nodes, and longer link distances, but retains much backward compatibility. Over time, Ethernet has largely replaced competing wired LAN technologies such as Token Ring, FDDI and ARCNET. The original 10BASE5 Ethernet uses coaxial cable as a shared medium, while the newer Ethernet variants use twisted pair and fiber optic links in conjunction with switches. Over the course of its history, Ethernet data transfer rates have been increased from the original to the latest , with rates up to under development. The Ethernet standards include several wiring and signaling variants of the OSI physical layer. Systems communicating over Ethernet ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Asynchronous Transfer Mode

Asynchronous Transfer Mode (ATM) is a telecommunications standard defined by American National Standards Institute (ANSI) and ITU-T (formerly CCITT) for digital transmission of multiple types of traffic. ATM was developed to meet the needs of the Broadband Integrated Services Digital Network as defined in the late 1980s, and designed to integrate telecommunication networks. It can handle both traditional high-throughput data traffic and real-time, low-latency content such as telephony (voice) and video.ATM Forum, The User Network Interface (UNI), v. 3.1, , Prentice Hall PTR, 1995, page 2. ATM provides functionality that uses features of circuit switching and packet switching networks by using asynchronous time-division multiplexing.McDysan (1999), p. 287. In the OSI reference model data link layer (layer 2), the basic transfer units are called '' frames''. In ATM these frames are of a fixed length (53 octets) called ''cells''. This differs from approaches such as Internet Pro ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

FDDI

Fiber Distributed Data Interface (FDDI) is a standard for data transmission in a local area network. It uses optical fiber as its standard underlying physical medium, although it was also later specified to use copper cable, in which case it may be called CDDI (Copper Distributed Data Interface), standardized as TP-PMD (Twisted-Pair Physical Medium-Dependent), also referred to as TP-DDI (Twisted-Pair Distributed Data Interface). FDDI was effectively made obsolete in local networks by Fast Ethernet which offered the same 100 Mbit/s speeds, but at a much lower cost and, since 1998, by Gigabit Ethernet due to its speed, and even lower cost, and ubiquity. Description FDDI provides a 100 Mbit/s optical standard for data transmission in local area network that can extend in range up to . Although FDDI logical topology is a ring-based token network, it did not use the IEEE 802.5 Token Ring protocol as its basis; instead, its protocol was derived from the IEEE 802.4 token bu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cray T90

The Cray T90 series (code-named ''Triton'' during development) was the last of a line of vector processing supercomputers manufactured by Cray Research, Inc, superseding the Cray C90 series. The first machines were shipped in 1995, and featured a 2.2 ns (450 MHz) clock cycle and two-wide vector pipes, for a peak speed of 1.8 gigaflops per processor; the high clock speed arises from the CPUs being built using ECL logic. As with the Cray J90, each CPU contained a scalar data cache, in addition to the instruction buffering/caching which has always been in Cray architectures. Configurations were available with between four and 32 processors, and with either IEEE 754 or traditional Cray floating-point arithmetic; the processors shared an SRAM main memory of up to eight gigabytes, with a bandwidth of three 64-bit words per cycle per CPU (giving a 32-CPU STREAM bandwidth of 360 gigabytes per second). The clock signal is distributed via a fiber-optic harness to the processors. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IEEE 754

The IEEE Standard for Floating-Point Arithmetic (IEEE 754) is a technical standard for floating-point arithmetic established in 1985 by the Institute of Electrical and Electronics Engineers (IEEE). The standard addressed many problems found in the diverse floating-point implementations that made them difficult to use reliably and portably. Many hardware floating-point units use the IEEE 754 standard. The standard defines: * ''arithmetic formats:'' sets of binary and decimal floating-point data, which consist of finite numbers (including signed zeros and subnormal numbers), infinities, and special "not a number" values (NaNs) * ''interchange formats:'' encodings (bit strings) that may be used to exchange floating-point data in an efficient and compact form * ''rounding rules:'' properties to be satisfied when rounding numbers during arithmetic and conversions * ''operations:'' arithmetic and other operations (such as trigonometric functions) on arithmetic formats * ''excepti ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Supercomputer

A supercomputer is a computer with a high level of performance as compared to a general-purpose computer. The performance of a supercomputer is commonly measured in floating-point operations per second ( FLOPS) instead of million instructions per second (MIPS). Since 2017, there have existed supercomputers which can perform over 1017 FLOPS (a hundred quadrillion FLOPS, 100 petaFLOPS or 100 PFLOPS). For comparison, a desktop computer has performance in the range of hundreds of gigaFLOPS (1011) to tens of teraFLOPS (1013). Since November 2017, all of the world's fastest 500 supercomputers run on Linux-based operating systems. Additional research is being conducted in the United States, the European Union, Taiwan, Japan, and China to build faster, more powerful and technologically superior exascale supercomputers. Supercomputers play an important role in the field of computational science, and are used for a wide range of computationally intensive tasks in var ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

.jpg)