|

CompCert

CompCert is a formally verified optimizing compiler for a large subset of the C99 programming language (known as Clight) which currently targets PowerPC, ARM, RISC-V, x86 and x86-64 architectures. This project, led by Xavier Leroy, started officially in 2005, funded by the French institutes ANR and INRIA. The compiler is specified, programmed and proven in the Rocq proof assistant. It aims to be used for programming embedded systems requiring reliability. The performance of its generated code is often close to that of GCC (version 3) at optimization level -O1, and always better than that of GCC without optimizations. Since 2015, AbsInt offers commercial licenses, provides support and maintenance, and contributes to the advancement of the tool. CompCert is released under a noncommercial license, and is therefore not free software, although some of its source files are dual-licensed with the GNU Lesser General Public License version 2.1 or later or are available under the ter ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Formal Verification

In the context of hardware and software systems, formal verification is the act of proving or disproving the correctness of a system with respect to a certain formal specification or property, using formal methods of mathematics. Formal verification is a key incentive for formal specification of systems, and is at the core of formal methods. It represents an important dimension of analysis and verification in electronic design automation and is one approach to software verification. The use of formal verification enables the highest Evaluation Assurance Level ( EAL7) in the framework of common criteria for computer security certification. Formal verification can be helpful in proving the correctness of systems such as: cryptographic protocols, combinational circuits, digital circuits with internal memory, and software expressed as source code in a programming language. Prominent examples of verified software systems include the CompCert verified C compiler and the seL ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AbsInt

AbsInt is a software-development tools vendor based in Saarbrücken, Germany. The company was founded in 1998 as a technology spin-off from the Department of Programming Languages and Compiler Construction of Prof. Reinhard Wilhelm at Saarland University. AbsInt specializes in software-verification tools based on abstract interpretation. Its tools are used worldwide by Fortune 500 companies, educational institutions, government agencies and startups. Products aiT WCET Analyzer statically computes safe upper bounds for the worst-case execution time of tasks in real-time systems. It directly analyzes binary executables and takes the intrinsic cache and pipeline behavior of the microprocessor into account. The U.S. National Highway Traffic Safety Administration (NHTSA) and NASA used it in its Study on Sudden Unintended Acceleration in the electronic throttle control systems of Toyota vehicles. StackAnalyzer determines the maximum stack usage of the tasks in embedded applications a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Sandrine Blazy

Sandrine Blazy is a French computer scientist known for her research in the formal verification of compilers, and especially for her work as a developer of CompCert, a compiler for a large subset of C99 that is "the first industrial-strength compiler with a mechanically checked proof of correctness". She is a professor at the University of Rennes and deputy director of IRISA, the Institut de recherche en informatique et systèmes aléatoires of the University of Rennes and the French National Centre for Scientific Research. Education and career Blazy studied computer science as an undergraduate through the École nationale supérieure d'informatique pour l'industrie et l'entreprise (ENSIIE) and Sorbonne University, earning both an engineering degree from ENSIIE and a master's degree from the Sorbonne in 1990. She completed a Ph.D. in 1993, and received a habilitation in 2008 at the University of Évry Val d'Essonne. She worked as a lecturer at ENSIIE from 1994 to 2009, when she ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Xavier Leroy

Xavier Leroy (born 15 March 1968) is a French computer scientist and programmer. He is best known for his role as a primary developer of the OCaml system. He is Professor of software science at Collège de France. Before his appointment at Collège de France in 2018, he was senior scientist (''directeur de recherche'') at the French government research institution Inria. Leroy was admitted to the École normale supérieure in Paris in 1987, where he studied mathematics and computer science. From 1989 to 1992 he did his PhD in computer science under the supervision of Gérard Huet. He is an internationally recognized expert on functional programming languages and compilers. In recent years, he has taken an interest in formal methods, formal proofs and certified compilation. He is the leader of the CompCert project that develops an optimizing compiler for the C programming language, formally verified in Coq. Leroy was also the original author of LinuxThreads, the most wide ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

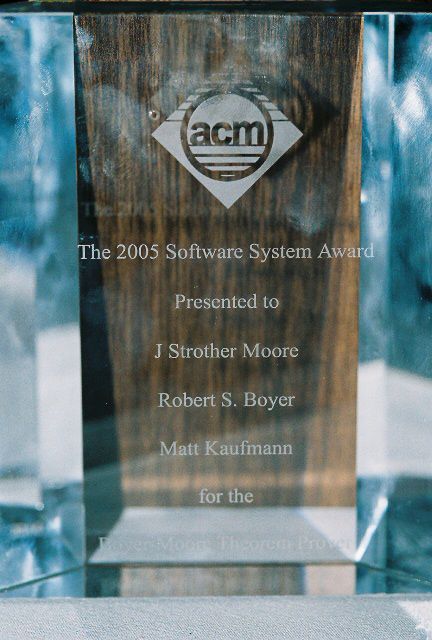

ACM Software System Award

The ACM Software System Award is an annual award that honors people or an organization "for developing a software system that has had a lasting influence, reflected in contributions to concepts, in commercial acceptance, or both". It is awarded by the Association for Computing Machinery (ACM) since 1983, with a cash prize sponsored by IBM of currently $35,000. Recipients The following is a list of recipients of the ACM Software System Award: See also * Software system A software system is a system of intercommunicating software component, components based on software forming part of a computer system (a combination of Computer hardware, hardware and software). It "consists of a number of separate Computer progr ... * List of computer science awards References External links Software System Award — ACM Awards{{Association for Computing Machinery Awards established in 1983 Software System Award Computer science awards ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Rocq

The Rocq Prover (previously known as Coq) is an interactive theorem prover first released in 1989. It allows the expression of mathematical assertions, mechanical checking of proofs of these assertions, assists in finding formal proofs using proof automation routines and extraction of a certified program from the constructive proof of its formal specification. Rocq works within the theory of the ''calculus of inductive constructions'', a derivative of the ''calculus of constructions''. Rocq is not an automated theorem prover but includes automatic theorem proving tactics ( procedures) and various decision procedures. The Association for Computing Machinery awarded Thierry Coquand, Gérard Huet, Christine Paulin-Mohring, Bruno Barras, Jean-Christophe Filliâtre, Hugo Herbelin, Chetan Murthy, Yves Bertot, and Pierre Castéran with the 2013 ACM Software System Award for Rocq (when it was still named Coq). Overview When viewed as a programming language, Rocq implements a d ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

INRIA

The National Institute for Research in Digital Science and Technology (Inria) () is a French national research institution focusing on computer science and applied mathematics. It was created under the name French Institute for Research in Computer Science and Automation (IRIA) () in 1967 at Rocquencourt near Paris, part of Plan Calcul. Its first site was the historical premises of SHAPE (central command of NATO military forces), which is still used as Inria's main headquarters. In 1980, IRIA became INRIA. Since 2011, it has been styled ''Inria''. Inria is a Public Scientific and Technical Research Establishment (EPST) under the double supervision of the French Ministry of National Education, Advanced Instruction and Research and the Ministry of Economy, Finance and Industry. Administrative status Inria has nine research centers distributed across France (in Bordeaux, Grenoble- Inovallée, Lille, Lyon, Nancy, Paris- Rocquencourt, Rennes, Saclay, and Sophia Antipolis) a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Architecture

ARM (stylised in lowercase as arm, formerly an acronym for Advanced RISC Machines and originally Acorn RISC Machine) is a family of reduced instruction set computer, RISC instruction set architectures (ISAs) for central processing unit, computer processors. Arm Holdings develops the ISAs and licenses them to other companies, who build the physical devices that use the instruction set. It also designs and licenses semiconductor intellectual property core, cores that implement these ISAs. Due to their low costs, low power consumption, and low heat generation, ARM processors are useful for light, portable, battery-powered devices, including smartphones, laptops, and tablet computers, as well as embedded systems. However, ARM processors are also used for desktop computer, desktops and server (computing), servers, including Fugaku (supercomputer), Fugaku, the world's fastest supercomputer from 2020 to 2022. With over 230 billion ARM chips produced, , ARM is the most widely used ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

RISC-V

RISC-V (pronounced "risk-five") is an open standard instruction set architecture (ISA) based on established reduced instruction set computer (RISC) principles. The project commenced in 2010 at the University of California, Berkeley. It transferred to the RISC-V Foundation in 2015, and from there to RISC-V International, a Swiss non-profit entity, in November 2019. Similar to several other RISC ISAs, e.g. Amber (processor), Amber (ARMv2)(2001), SuperH#J_Core, J-Core(2015), OpenRISC(2000), or OpenSPARC(2005), RISC-V is offered under royalty-free open-source licenses. The documents defining the RISC-V instruction set architecture (ISA) are offered under a Creative Commons license or a BSD licenses, BSD License. Mainline support for RISC-V was added to the Linux 5.17 kernel in 2022, along with its toolchain. In July 2023, RISC-V, in its 64-bit computing, 64-bit variant called riscv64, was included as an official architecture of Linux distribution Debian, in its Debian version histor ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

X86-64

x86-64 (also known as x64, x86_64, AMD64, and Intel 64) is a 64-bit extension of the x86 instruction set architecture, instruction set. It was announced in 1999 and first available in the AMD Opteron family in 2003. It introduces two new operating modes: 64-bit mode and compatibility mode, along with a new four-level paging mechanism. In 64-bit mode, x86-64 supports significantly larger amounts of virtual memory and physical memory compared to its 32-bit computing, 32-bit predecessors, allowing programs to utilize more memory for data storage. The architecture expands the number of general-purpose registers from 8 to 16, all fully general-purpose, and extends their width to 64 bits. Floating-point arithmetic is supported through mandatory SSE2 instructions in 64-bit mode. While the older x87 FPU and MMX registers are still available, they are generally superseded by a set of sixteen 128-bit Processor register, vector registers (XMM registers). Each of these vector registers ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

PowerPC

PowerPC (with the backronym Performance Optimization With Enhanced RISC – Performance Computing, sometimes abbreviated as PPC) is a reduced instruction set computer (RISC) instruction set architecture (ISA) created by the 1991 Apple Inc., Apple–IBM–Motorola alliance, known as AIM alliance, AIM. PowerPC, as an evolving instruction set, has been named Power ISA since 2006, while the old name lives on as a trademark for some implementations of Power Architecture–based processors. Originally intended for personal computers, the architecture is well known for being used by Apple's desktop and laptop lines from 1994 until 2006, and in several videogame consoles including Microsoft's Xbox 360, Sony's PlayStation 3, and Nintendo's GameCube, Wii, and Wii U. PowerPC was also used for the Curiosity (rover), Curiosity and Perseverance (rover), Perseverance rovers on Mars and a variety of satellites. It has since become a niche architecture for personal computers, particularly with A ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |