|

Bijan Davari

Bijan Davari (born September 16, 1954) is an Iranian-American engineer. He is an IBM Fellow and Vice President at IBM Thomas J Watson Research Center, Yorktown Hts, NY. His pioneering work in the miniaturization of semiconductor devices changed the world of computing. His research led to the first generation of voltage-scaled deep-submicron CMOS with sufficient performance to totally replace bipolar technology in IBM mainframes and enable new high-performance UNIX servers. As head of IBM’s Semiconductor Research Center (SRDC), he led IBM into the use of Copper interconnect, silicon on insulator (SOI), and Embedded DRAM before its rivals. He is a member of the U.S. National Academy of Engineering and is known for his seminal contributions to the field of CMOS technology. He is an IEEE Fellow, recipient of the J J Ebers Award in 2005 and IEEE Andrew S. Grove Award in 2010. At the present time, he leads the Next Generation Systems Area of research. Education Bijan Davari wa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

American Citizen

Citizenship of the United States is a legal status that entails Americans with specific rights, duties, protections, and benefits in the United States. It serves as a foundation of fundamental rights derived from and protected by the Constitution and laws of the United States, such as freedom of expression, due process, the rights to vote (however, not all citizens have the right to vote in all federal elections, for example, those living in Puerto Rico), live and work in the United States, and to receive federal assistance. There are two primary sources of citizenship: birthright citizenship, in which persons born within the territorial limits of the United States are presumed to be a citizen, or—providing certain other requirements are met—born abroad to a United States citizen parent, and naturalization, a process in which an eligible legal immigrant applies for citizenship and is accepted. The first of these two pathways to citizenship is specified in the Citizenship Cla ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Rensselaer Polytechnic Institute

Rensselaer Polytechnic Institute () (RPI) is a private research university in Troy, New York, with an additional campus in Hartford, Connecticut. A third campus in Groton, Connecticut closed in 2018. RPI was established in 1824 by Stephen Van Rensselaer and Amos Eaton for the "application of science to the common purposes of life" and is the oldest technological university in the English-speaking world and the Western Hemisphere. Built on a hillside, RPI's campus overlooks the city of Troy and the Hudson River, and is a blend of traditional and modern architecture. The institute operates an on‑campus business incubator and the Rensselaer Technology Park. RPI is organized into six main schools which contain 37 departments, with emphasis on science and technology. It is classified among "R1: Doctoral Universities: Very High Research Activity" and many of its engineering programs are highly ranked. As of 2017, RPI's faculty and alumni included 6 members of the National Inve ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Living People

Related categories * :Year of birth missing (living people) / :Year of birth unknown * :Date of birth missing (living people) / :Date of birth unknown * :Place of birth missing (living people) / :Place of birth unknown * :Year of death missing / :Year of death unknown * :Date of death missing / :Date of death unknown * :Place of death missing / :Place of death unknown * :Missing middle or first names See also * :Dead people * :Template:L, which generates this category or death years, and birth year and sort keys. : {{DEFAULTSORT:Living people 21st-century people People by status ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Cell Broadband Engine

Cell is a multi-core microprocessor microarchitecture that combines a general-purpose PowerPC core of modest performance with streamlined coprocessing elements which greatly accelerate multimedia and vector processing applications, as well as many other forms of dedicated computation. It was developed by Sony, Toshiba, and IBM, an alliance known as "STI". The architectural design and first implementation were carried out at the STI Design Center in Austin, Texas over a four-year period beginning March 2001 on a budget reported by Sony as approaching US$400 million. Cell is shorthand for Cell Broadband Engine Architecture, commonly abbreviated ''CBEA'' in full or ''Cell BE'' in part. The first major commercial application of Cell was in Sony's PlayStation 3 game console, released in 2006. In May 2008, the Cell-based IBM Roadrunner supercomputer became the first TOP500 LINPACK sustained 1.0 petaflops system. Mercury Computer Systems also developed designs based on the Cell. The ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

250 Nanometer

The 250 nanometer (250 nm or 0.25 µm) process refers to a level of semiconductor process technology that was reached by most manufacturers in the 1997–1998 timeframe. Products featuring 250 nm manufacturing process *The DEC Alpha 21264A, which was made commercially available in 1999. *The AMD K6-2 ''Chomper'' and ''Chomper Extended''. Chomper was released on May 28, 1998. *The AMD K6-III "Sharptooth" used 250 nm. *The mobile Pentium MMX ''Tillamook'', released in August 1997. *The Pentium II '' Deschutes''. *The Pentium III '' Katmai''. *The Dreamcast's CPU and GPU. *The initial version of the Emotion Engine processor used in the PlayStation 2 The PlayStation 2 (PS2) is a home video game console developed and marketed by Sony Computer Entertainment. It was first released in Japan on 4 March 2000, in North America on 26 October 2000, in Europe on 24 November 2000, and in Australia on 3 .... *00250 Computer-related introductions in 1998 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

180 nm

The 180 nm process refers to the level of MOSFET ( CMOS) semiconductor process technology that was commercialized around the 1998–2000 timeframe by leading semiconductor companies, starting with TSMC and Fujitsu, then followed by Sony, Toshiba, Intel, AMD, Texas Instruments and IBM. The origin of the 180 nm value is historical, as it reflects a trend of 70% scaling every 2–3 years. The naming is formally determined by the International Technology Roadmap for Semiconductors (ITRS). Some of the first CPUs manufactured with this process include Intel Coppermine family of Pentium III processors. This was the first technology using a gate length shorter than that of light used for contemporary lithography, which had a wavelength of 193 nm. Some more recent microprocessors and microcontrollers (e.g. PIC) are using this technology because it is typically low cost and does not require upgrading of existing equipment. In 2022, Google sponsored open-source hardwa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Multigate Device

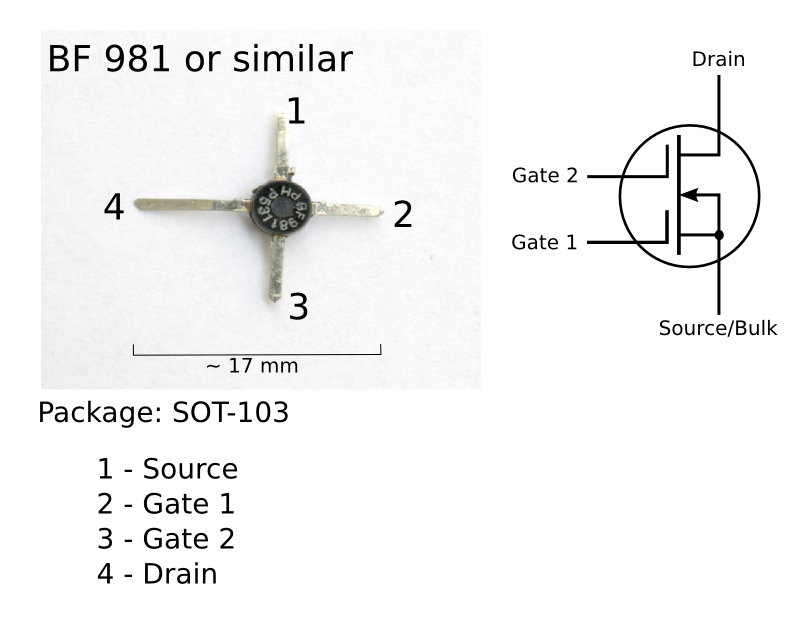

A multigate device, multi-gate MOSFET or multi-gate field-effect transistor (MuGFET) refers to a metal–oxide–semiconductor field-effect transistor (MOSFET) that has more than one gate on a single transistor. The multiple gates may be controlled by a single gate electrode, wherein the multiple gate surfaces act electrically as a single gate, or by independent gate electrodes. A multigate device employing independent gate electrodes is sometimes called a multiple-independent-gate field-effect transistor (MIGFET). The most widely used multi-gate devices are the FinFET (fin field-effect transistor) and the GAAFET (gate-all-around field-effect transistor), which are non-planar transistors, or 3D transistors. Multi-gate transistors are one of the several strategies being developed by MOS semiconductor manufacturers to create ever-smaller microprocessors and memory cells, colloquially referred to as extending Moore's law (in its narrow, specific version concerning density scaling, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Tungsten

Tungsten, or wolfram, is a chemical element with the symbol W and atomic number 74. Tungsten is a rare metal found naturally on Earth almost exclusively as compounds with other elements. It was identified as a new element in 1781 and first isolated as a metal in 1783. Its important ores include scheelite and wolframite, the latter lending the element its alternate name. The free element is remarkable for its robustness, especially the fact that it has the highest melting point of all known elements barring carbon (which sublimes at normal pressure), melting at . It also has the highest boiling point, at . Its density is , comparable with that of uranium and gold, and much higher (about 1.7 times) than that of lead. Polycrystalline tungsten is an intrinsically brittle and hard material (under standard conditions, when uncombined), making it difficult to work. However, pure single-crystalline tungsten is more ductile and can be cut with a hard-steel hacksaw. Tungsten occurs in many ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Gate Oxide

The gate oxide is the dielectric layer that separates the gate terminal of a MOSFET (metal-oxide-semiconductor field-effect transistor) from the underlying source and drain terminals as well as the conductive channel that connects source and drain when the transistor is turned on. Gate oxide is formed by thermal oxidation of the silicon of the channel to form a thin (5 - 200 nm) insulating layer of silicon dioxide. The insulating silicon dioxide layer is formed through a process of self-limiting oxidation, which is described by the Deal–Grove model. A conductive gate material is subsequently deposited over the gate oxide to form the transistor. The gate oxide serves as the dielectric layer so that the gate can sustain as high as 1 to 5 MV/cm transverse electric field in order to strongly modulate the conductance of the channel. Above the gate oxide is a thin electrode layer made of a conductor which can be aluminium, a highly doped silicon, a refractory metal such as tungste ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

10 nanometer

In semiconductor fabrication, the International Technology Roadmap for Semiconductors (ITRS) defines the 10 nm process as the MOSFET technology node following the 14 nm node. 10 nm class denotes chips made using process technologies between 10 and 20 nm. All production 10 nm processes are based on FinFET (fin field-effect transistor) technology, a type of multi-gate MOSFET technology that is a non-planar evolution of planar silicon CMOS technology. Samsung first started their production of 10 nm-class chips in 2013 for their multi-level cell (MLC) flash memory chips, followed by their SoCs using their 10 nm process in 2016. TSMC began commercial production of 10 nm chips in 2016, and Intel later began production of 10nm chips in 2018. Since 2009, however, "node" has become a commercial name for marketing purposes that indicates new generations of process technologies, without any relation to gate length, metal pitch or gate pitch. For example, GlobalFoun ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Shallow Trench Isolation

Shallow trench isolation (STI), also known as box isolation technique, is an integrated circuit feature which prevents electric current leakage between adjacent semiconductor device components. STI is generally used on CMOS process technology nodes of 250 nanometers and smaller. Older CMOS technologies and non-MOS technologies commonly use isolation based on LOCOS. STI is created early during the semiconductor device fabrication process, before transistors are formed. The key steps of the STI process involve etching a pattern of trenches in the silicon, depositing one or more dielectric materials (such as silicon dioxide) to fill the trenches, and removing the excess dielectric using a technique such as chemical-mechanical planarizationbr> Certain semiconductor fabrication technologies also include deep trench isolation, a related feature often found in analog integrated circuits. The effect of the trench edge has given rise to what has recently been termed the "reverse narro ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |