|

Ampere (microarchitecture)

Ampere is the codename for a graphics processing unit (GPU) microarchitecture developed by Nvidia as the successor to both the Volta and Turing architectures, officially announced on May 14, 2020. It is named after French mathematician and physicist André-Marie Ampère. Nvidia announced the next-generation GeForce 30 series consumer GPUs at a GeForce Special Event on September 1, 2020. Nvidia announced A100 80GB GPU at SC20 on November 16, 2020. Mobile RTX graphics cards and the RTX 3060 were revealed on January 12, 2021. Nvidia also announced Ampere's successor, Hopper, at GTC 2022, and "Ampere Next Next" for a 2024 release at GPU Technology Conference 2021. Details Architectural improvements of the Ampere architecture include the following: * CUDA Compute Capability 8.0 for A100 and 8.6 for the GeForce 30 series * TSMC's 7 nm FinFET process for A100 * Custom version of Samsung's 8 nm process (8N) for the GeForce 30 series * Third-generation Tensor Cores with ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Turing (microarchitecture)

Turing is the codename for a graphics processing unit (GPU) microarchitecture developed by Nvidia. It is named after the prominent mathematician and computer scientist Alan Turing. The architecture was first introduced in August 2018 at SIGGRAPH 2018 in the workstation-oriented Quadro RTX cards, and one week later at Gamescom in consumer GeForce RTX 20 series graphics cards. Building on the preliminary work of its HPC-exclusive predecessor, the Turing architecture introduces the first consumer products capable of real-time ray tracing, a longstanding goal of the computer graphics industry. Key elements include dedicated artificial intelligence processors ("Tensor cores") and dedicated ray tracing processors (“RT cores”). Turing leverages DXR, OptiX, and Vulkan for access to ray-tracing. In February 2019, Nvidia released the GeForce 16 series of GPUs, which utilizes the new Turing design but lacks the RT and Tensor cores. Turing is manufactured using TSMC's 12 nm FinFET s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

HBM2

High Bandwidth Memory (HBM) is a high-speed computer memory interface for 3D-stacked synchronous dynamic random-access memory (SDRAM) initially from Samsung, AMD and SK Hynix. It is used in conjunction with high-performance graphics accelerators, network devices, high-performance datacenter AI ASICs and FPGAs and in some supercomputers (such as the NEC SX-Aurora TSUBASA and Fujitsu A64FX). The first HBM memory chip was produced by SK Hynix in 2013, and the first devices to use HBM were the AMD Fiji GPUs in 2015. High Bandwidth Memory has been adopted by JEDEC as an industry standard in October 2013.High Bandwidth Memory (HBM) DRAM (JESD235) JEDEC, October 2013 The second generation, HBM2, was accepted by JEDEC in January 2016. Technology < ...

|

Mellanox

Mellanox Technologies Ltd. ( he, מלאנוקס טכנולוגיות בע"מ) was an Israeli-American multinational supplier of computer networking products based on InfiniBand and Ethernet technology. Mellanox offered adapters, switches, software, cables and silicon for markets including high-performance computing, data centers, cloud computing, computer data storage and financial services. On March 11, 2019, Nvidia announced its intent to acquire the company for $6.9 billion. Other companies willing to acquire Mellanox were Intel, Xilinx and Microsoft. The deal closed on April 27, 2020, with approval from the EU, U.S. and Chinese antitrust authorities. The company was integrated into Nvidia's networking division in 2020 and Nvidia stopped using the brand name "Mellanox" for its new networking products. History 1999–2009 Mellanox was founded in May 1999 by former Israeli executives of Intel Corporation and Galileo Technology (which was acquired by Marvell Technology Group ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Epyc

Epyc is a brand of multi-core x86-64 microprocessors designed and sold by AMD, based on the company's Zen microarchitecture. Introduced in June 2017, they are specifically targeted for the server and embedded system markets. Epyc processors share the same microarchitecture as their regular desktop-grade counterparts, but have enterprise-grade features such as higher core counts, more PCI Express lanes, support for larger amounts of RAM, and larger cache memory. They also support multi-chip and dual-socket system configurations by using the Infinity Fabric interconnect. History In March 2017, AMD announced plans to re-enter the server market with a platform based on the Zen microarchitecture, codenamed Naples, and officially revealed it under the brand name Epyc in May. That June, AMD officially launched Epyc 7001 series processors, offering up to 32 cores per socket, and enabling performance that allowed Epyc to be competitive with the competing Intel Xeon product line. Two years ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

NVMe

NVM Express (NVMe) or Non-Volatile Memory Host Controller Interface Specification (NVMHCIS) is an open, logical-device interface specification for accessing a computer's non-volatile storage media usually attached via PCI Express (PCIe) bus. The initialism ''NVM'' stands for ''non-volatile memory'', which is often NAND flash memory that comes in several physical form factors, including solid-state drives (SSDs), PCIe add-in cards, and M.2 cards, the successor to mSATA cards. NVM Express, as a logical-device interface, has been designed to capitalize on the low latency and internal parallelism of solid-state storage devices. Architecturally, the logic for NVMe is physically stored within and executed by the NVMe controller chip that is physically co-located with the storage media, usually an SSD. Version changes for NVMe, e.g., 1.3 to 1.4, are incorporated within the storage media, and do not affect PCIe-compatible components such as motherboards and CPUs. By its design, NVM Exp ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

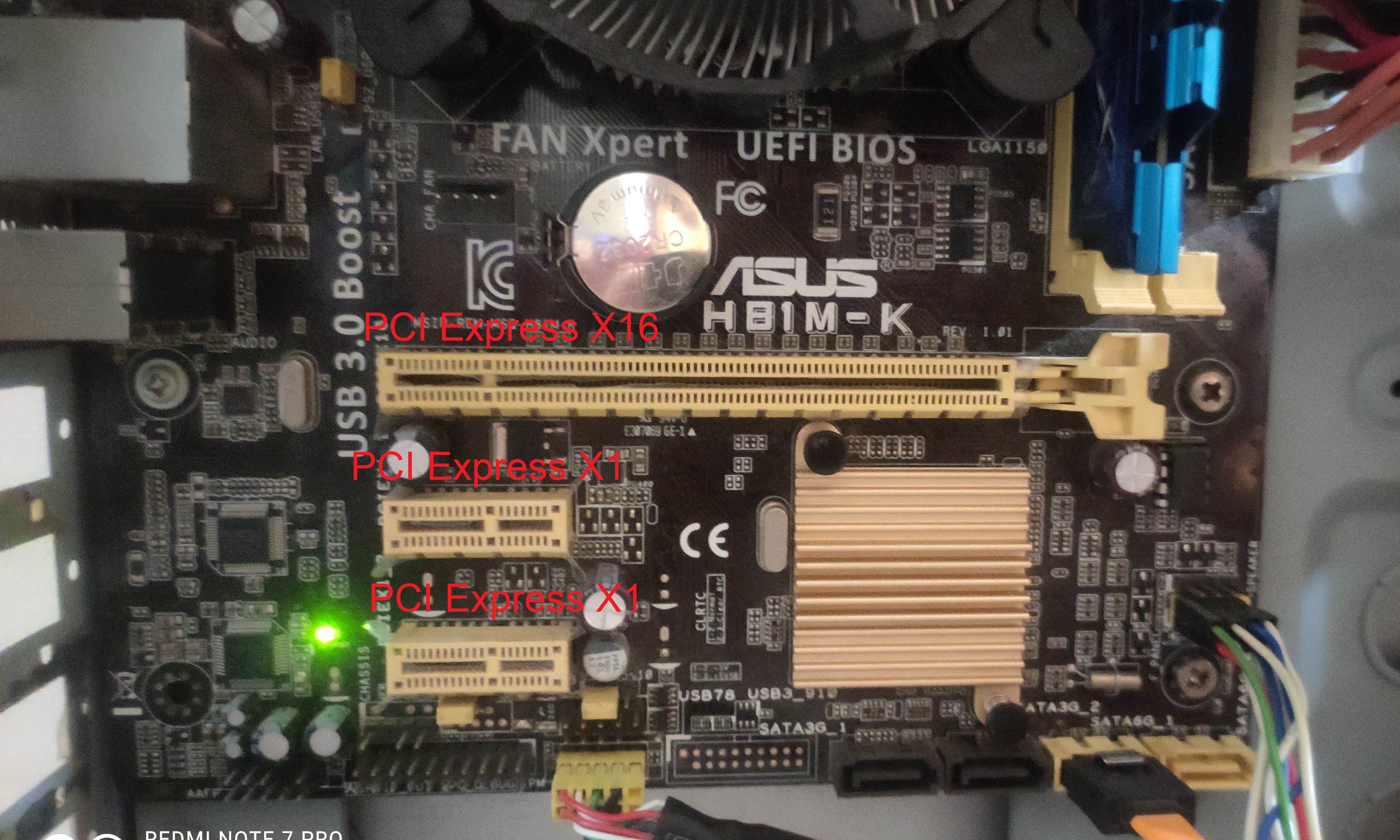

PCI Express

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common motherboard interface for personal computers' graphics cards, hard disk drive host adapters, SSDs, Wi-Fi and Ethernet hardware connections. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism (Advanced Error Reporting, AER), and native hot-swap functionality. More recent revisions of the PCIe standard provide hardware support for I/O virtualization. The PCI Express electrical interface is measured by the number of simultaneous lanes. (A lane is a single send/receive line of data. The analogy is a highway with traffic in both directions. ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Nvidia DGX

Nvidia DGX is a line of Nvidia-produced servers and workstations which specialize in using GPGPU to accelerate deep learning applications. The typical design of a DGX system is based upon a rackmount chassis with motherboard that carries high performance x86 server CPUs (Typically Intel Xeons, though recently the DGX A100 and DGX Station A100 utilize AMD EPYC CPUs). The main component of a DGX system is a set of 4 to 16 Nvidia Tesla GPU modules on an independent system board. DGX systems have large heatsinks and powerful fans to adequately cool thousands of watts of thermal output. The GPU modules are typically integrated into the system using a version of the SXM socket. Models Pascal - Volta DGX-1 DGX-1 servers feature 8 GPUs based on the Pascal or Volta daughter cards with 128GB of total HBM2 memory, connected by an NVLink mesh network. The DGX-1 was announced on the 6th of April in 2016. All models are based on a dual socket configuration of Intel Xeon E5 CPUs, and a ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Library (computing)

In computer science, a library is a collection of non-volatile memory, non-volatile resources used by computer programs, often for software development. These may include configuration data, documentation, help data, message templates, Code reuse, pre-written code and subroutines, Class (computer science), classes, Value (computer science), values or Data type, type specifications. In OS/360 and successors, IBM's OS/360 and its successors they are referred to as Data set (IBM mainframe)#Partitioned datasets, partitioned data sets. A library is also a collection of implementations of behavior, written in terms of a language, that has a well-defined interface (computing), interface by which the behavior is invoked. For instance, people who want to write a higher-level program can use a library to make system calls instead of implementing those system calls over and over again. In addition, the behavior is provided for reuse by multiple independent programs. A program invokes the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

JPEG

JPEG ( ) is a commonly used method of lossy compression for digital images, particularly for those images produced by digital photography. The degree of compression can be adjusted, allowing a selectable tradeoff between storage size and image quality. JPEG typically achieves 10:1 compression with little perceptible loss in image quality. Since its introduction in 1992, JPEG has been the most widely used image compression standard in the world, and the most widely used digital image format, with several billion JPEG images produced every day as of 2015. The term "JPEG" is an acronym for the Joint Photographic Experts Group, which created the standard in 1992. JPEG was largely responsible for the proliferation of digital images and digital photos across the Internet, and later social media. JPEG compression is used in a number of image file formats. JPEG/Exif is the most common image format used by digital cameras and other photographic image capture devices; along with JPEG ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Nvidia NVDEC

Nvidia NVDEC (formerly known as NVCUVID) is a feature in its graphics cards that performs video decoding, offloading this compute-intensive task from the CPU. It is accompanied by NVENC for video ''encoding'' in Nvidia's Video Codec SDK. Technology NVDEC can offload video decoding to full fixed-function decoding hardware (Nvidia PureVideo), or (partially) decode via CUDA software running on the GPU, if fixed-function hardware is not available. Depending on the GPU architecture, the following codecs are supported: * MPEG-2 * VC-1 * H.264 (AVC) * H.265 (HEVC) * VP8 * VP9 * AV1 Versions NVCUVID was originally distributed as part of the Nvidia CUDA Toolkit. Later, it was renamed to NVDEC and moved to the Nvidia Video Codec SDK. Operating system support NVDEC is available for Windows and Linux operating systems. As NVDEC is a proprietary API (as opposed to the open-source VDPAU API), it is only supported by the proprietary Nvidia driver on Linux. Application and library s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Nvidia PureVideo

PureVideo is Nvidia's hardware SIP core that performs video decoding. PureVideo is integrated into some of the Nvidia GPUs, and it supports hardware decoding of multiple video codec standards: MPEG-2, VC-1, H.264, HEVC, and AV1. PureVideo occupies a considerable amount of a GPU's die area and should not be confused with Nvidia NVENC. In addition to video decoding on chip, PureVideo offers features such as edge enhancement, noise reduction, deinterlacing, dynamic contrast enhancement and color enhancement. Operating system support The PureVideo SIP core needs to be supported by the device driver, which provides one or more interfaces such as NVDEC, VDPAU, VAAPI or DXVA. One of these interfaces is then used by end-user software, for example VLC media player or GStreamer, to access the PureVideo hardware and make use of it. Nvidia's proprietary device driver is available for multiple operating systems and support for PureVideo has been added to it. Additionally, a free device d ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SR-IOV

In virtualization, single root input/output virtualization (SR-IOV) is a specification that allows the isolation of PCI Express resources for manageability and performance reasons. Details A single physical PCI Express bus can be shared in a virtual environment using the SR-IOV specification. The SR-IOV offers different virtual functions to different virtual components (e.g. network adapter) on a physical server machine. SR-IOV uses physical and virtual functions to control or configure PCIe devices. Physical functions have the ability to move data in and out of the device while virtual functions are lightweight PCIe functions that support data flowing but also have a restricted set of configuration resources. The virtual or physical functions available to the hypervisor or guest operating system depend on the PCIe device. The SR-IOV allows different virtual machines (VMs) in a virtual environment to share a single PCI Express hardware interface. In contrast, MR-IOV allows I/O PC ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |