|

AGESA

AMD Generic Encapsulated Software Architecture (AGESA) is a procedure library developed by Advanced Micro Devices (AMD), used to perform the Platform Initialization (PI) on mainboards using their AMD64 architecture. As part of the BIOS of such mainboards, AGESA is responsible for the initialization of the CPU cores, chipset, main memory, and the HyperTransport controller. History AGESA was open sourced in early 2011, aiming to aid in the development of coreboot, a project attempting to replace PC's proprietary BIOS. However, such releases never became the basis for the development of coreboot beyond AMD's family 15h, as they were subsequently halted. AGESA became particularly relevant with the AM4 platform, which AMD designed for futureproofing, and as of May 2019 has served as the base for three different generations of CPUs based on its Zen architecture. For each of these generations, a new branch of AGESA code has been released. AGESA versioning often runs separately for ea ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Coreboot

coreboot, formerly known as LinuxBIOS, is a software project aimed at replacing proprietary firmware (BIOS or UEFI) found in most computers with a lightweight firmware designed to perform only the minimum number of tasks necessary to load and run a modern 32-bit or 64-bit operating system. Since coreboot initializes the bare hardware, it must be ported to every chipset and motherboard that it supports. As a result, coreboot is available only for a limited number of hardware platforms and motherboard models. One of the coreboot variants is Libreboot, a software distribution fully free of proprietary blobs, aimed at end users. History The coreboot project began in the winter of 1999 in the Advanced Computing Laboratory at Los Alamos National Laboratory (LANL), with the goal of creating a BIOS that would start fast and handle errors intelligently. It is licensed under the terms of the GNU General Public License version 2 (GPLv2). Main contributors include LANL, SiS, AMD, Core ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Coreboot

coreboot, formerly known as LinuxBIOS, is a software project aimed at replacing proprietary firmware (BIOS or UEFI) found in most computers with a lightweight firmware designed to perform only the minimum number of tasks necessary to load and run a modern 32-bit or 64-bit operating system. Since coreboot initializes the bare hardware, it must be ported to every chipset and motherboard that it supports. As a result, coreboot is available only for a limited number of hardware platforms and motherboard models. One of the coreboot variants is Libreboot, a software distribution fully free of proprietary blobs, aimed at end users. History The coreboot project began in the winter of 1999 in the Advanced Computing Laboratory at Los Alamos National Laboratory (LANL), with the goal of creating a BIOS that would start fast and handle errors intelligently. It is licensed under the terms of the GNU General Public License version 2 (GPLv2). Main contributors include LANL, SiS, AMD, Core ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

AMD64

x86-64 (also known as x64, x86_64, AMD64, and Intel 64) is a 64-bit version of the x86 instruction set, first released in 1999. It introduced two new modes of operation, 64-bit mode and compatibility mode, along with a new 4-level paging mode. With 64-bit mode and the new paging mode, it supports vastly larger amounts of virtual memory and physical memory than was possible on its 32-bit predecessors, allowing programs to store larger amounts of data in memory. x86-64 also expands general-purpose registers to 64-bit, and expands the number of them from 8 (some of which had limited or fixed functionality, e.g. for stack management) to 16 (fully general), and provides numerous other enhancements. Floating-point arithmetic is supported via mandatory SSE2-like instructions, and x87/ MMX style registers are generally not used (but still available even in 64-bit mode); instead, a set of 16 vector registers, 128 bits each, is used. (Each register can store one or two double-preci ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

HyperTransport

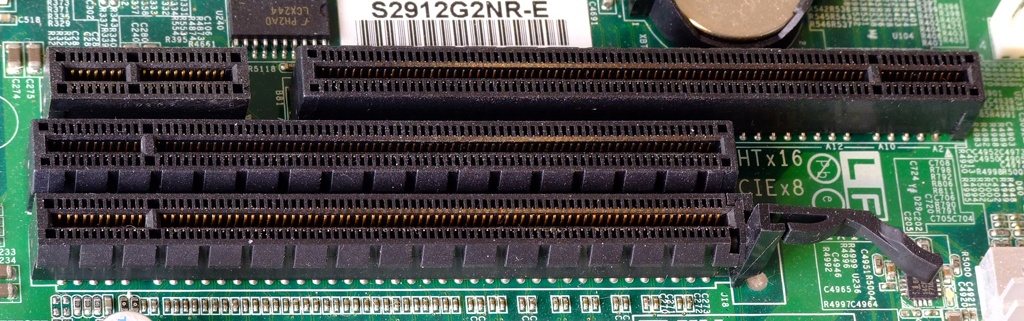

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/parallel high-bandwidth, low- latency point-to-point link that was introduced on April 2, 2001. The HyperTransport Consortium is in charge of promoting and developing HyperTransport technology. HyperTransport is best known as the system bus architecture of AMD central processing units (CPUs) from Athlon 64 through AMD FX and the associated motherboard chipsets. HyperTransport has also been used by IBM and Apple for the Power Mac G5 machines, as well as a number of modern MIPS systems. The current specification HTX 3.1 remained competitive for 2014 high-speed (2666 and 3200 MT/s or about 10.4 GB/s and 12.8 GB/s) DDR4 RAM and slower (around 1 GB/similar to high end Solid-state drive#Standard card form factors, PCIe SSDs ULLtraDIMM flash RAM) technology—a wider range of RAM speeds on a common CPU bus ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Memory Reference Code

The Memory Reference Code (or MRC) is a fundamental component in the design of some computers, and is "one of the most important aspects of the BIOS" for an Intel-based motherboard. It is the part of an Intel motherboard's firmware that determines how the computer's memory (RAM) will be initialized, and adjusts memory timing algorithms correctly for the effects of any modifications set by the user or computer hardware. Overview Intel has defined the Memory Reference Code (MRC) as follows: The MRC is responsible for initializing the memory as part of the POST process at power-on. Intel provides support in the MRC for all fully validated memory configurations. For non-validated configurations, a system designer should work with their BIOS vendor to produce a working MRC solution ... The MRC in the system BIOS needs to know the specification of the attached system memory. Most of this info should be contained in the onboard SPD. With this in mind care needs to be taken wh ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Advanced Micro Devices

Advanced Micro Devices, Inc. (AMD) is an American multinational semiconductor company based in Santa Clara, California, that develops computer processors and related technologies for business and consumer markets. While it initially manufactured its own processors, the company later outsourced its manufacturing, a practice known as going fabless, after GlobalFoundries was spun off in 2009. AMD's main products include microprocessors, motherboard chipsets, embedded processors, graphics processors, and FPGAs for servers, workstations, personal computers, and embedded system applications. History First twelve years Advanced Micro Devices was formally incorporated by Jerry Sanders, along with seven of his colleagues from Fairchild Semiconductor, on May 1, 1969. Sanders, an electrical engineer who was the director of marketing at Fairchild, had, like many Fairchild executives, grown frustrated with the increasing lack of support, opportunity, and flexibility within th ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Platform Initialization

The Platform Initialization Specification (PI Specification) is a specification published by the Unified EFI Forum that describes the internal interfaces between different parts of computer platform firmware. This allows for more interoperability between firmware components from different sources. This specification is normally, but not by requirement, used in conjunction with the UEFI UEFI (Unified Extensible Firmware Interface) is a set of specifications written by the UEFI Forum. They define the architecture of the platform firmware used for booting and its interface for interaction with the operating system. Examples of f ... specification. Current version Platform Initialization Specification 1.7, Released January 2019. Contents As of version 1.3, the PI specification contains five volumes: * Volume 1: Pre-EFI Initialization Core Interface * Volume 2: Driver Execution Environment Core Interface * Volume 3: Shared Architectural Elements * Volume 4: System Management ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

BIOS

In computing, BIOS (, ; Basic Input/Output System, also known as the System BIOS, ROM BIOS, BIOS ROM or PC BIOS) is firmware used to provide runtime services for operating systems and programs and to perform hardware initialization during the booting process (power-on startup). The BIOS firmware comes pre-installed on an IBM PC or IBM PC compatible's system board and exists in some UEFI-based systems to maintain compatibility with operating systems that do not support UEFI native operation. The name originates from the Basic Input/Output System used in the CP/M operating system in 1975. The BIOS originally proprietary to the IBM PC has been reverse engineered by some companies (such as Phoenix Technologies) looking to create compatible systems. The interface of that original system serves as a ''de facto'' standard. The BIOS in modern PCs initializes and tests the system hardware components (Power-on self-test), and loads a boot loader from a mass storage device which then i ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Central Processing Unit

A central processing unit (CPU), also called a central processor, main processor or just processor, is the electronic circuitry that executes instructions comprising a computer program. The CPU performs basic arithmetic, logic, controlling, and input/output (I/O) operations specified by the instructions in the program. This contrasts with external components such as main memory and I/O circuitry, and specialized processors such as graphics processing units (GPUs). The form, design, and implementation of CPUs have changed over time, but their fundamental operation remains almost unchanged. Principal components of a CPU include the arithmetic–logic unit (ALU) that performs arithmetic and logic operations, processor registers that supply operands to the ALU and store the results of ALU operations, and a control unit that orchestrates the fetching (from memory), decoding and execution (of instructions) by directing the coordinated operations of the ALU, registers and other co ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Zen (first Generation Microarchitecture)

Zen is the codename for the first iteration in a family of computer processor microarchitectures of the same name from AMD. It was first used with their Ryzen series of CPUs in February 2017. The first Zen-based preview system was demonstrated at E3 2016, and first substantially detailed at an event hosted a block away from the Intel Developer Forum 2016. The first Zen-based CPUs, codenamed "Summit Ridge", reached the market in early March 2017, Zen-derived Epyc server processors launched in June 2017 and Zen-based APUs arrived in November 2017. Zen is a clean sheet design that differs from AMD's previous long-standing Bulldozer architecture. Zen-based processors use a 14 nm FinFET process, are reportedly more energy efficient, and can execute significantly more instructions per cycle. SMT has been introduced, allowing each core to run two threads. The cache system has also been redesigned, making the L1 cache write-back. Zen processors use three different sockets: desktop and ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Zen (microarchitecture)

Zen is the codename for a family of computer processor microarchitectures from AMD, first launched in February 2017 with the first generation of its Ryzen CPUs. It is used in Ryzen (desktop and mobile), Ryzen Threadripper (workstation/high end desktop), and Epyc (server). Comparison History First generation The first generation Zen was launched with the Ryzen 1000 series of CPUs (codenamed Summit Ridge) in February 2017. The first Zen-based preview system was demonstrated at E3 2016, and first substantially detailed at an event hosted a block away from the Intel Developer Forum 2016. The first Zen-based CPUs reached the market in early March 2017, and Zen-derived Epyc server processors (codenamed "Naples") launched in June 2017 and Zen-based APUs (codenamed "Raven Ridge") arrived in November 2017. This first iteration of Zen utilized Global Foundries' 14 nm manufacturing process. First generation refresh Zen+ was first released in April 2018, powering the second ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Zen+

Zen+ is the codename for a computer processor microarchitecture by AMD. It is the successor to the first gen Zen microarchitecture, first released in April 2018, powering the second generation of Ryzen processors, known as Ryzen 2000 for mainstream desktop systems, Threadripper 2000 for high-end desktop setups and Ryzen 3000G (instead of 2000G) for accelerated processing units (APUs). Features Zen+ uses GlobalFoundries' 12 nm fabrication process, an optimization of the 14 nm process used for Zen, with only minor design rule changes. This means that the die sizes between Zen and Zen+ are identical as AMD chose to use the new smaller transistors to increase the amount of empty space, or "dark silicon", between the various features on the die. This was done to improve power efficiency & reduce thermal density to allow for higher clock speeds, rather than design an entirely new floorplan for a physically smaller die (which would have been significantly more work and thus ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |