|

Dhrystone

Dhrystone is a synthetic computing benchmark program developed in 1984 by Reinhold P. Weicker intended to be representative of system (integer) programming. The Dhrystone grew to become representative of general processor ( CPU) performance. The name "Dhrystone" is a pun on a different benchmark algorithm called Whetstone, which emphasizes floating point performance. With Dhrystone, Weicker gathered meta-data from a broad range of software, including programs written in FORTRAN, PL/1, SAL, ALGOL 68, and Pascal. He then characterized these programs in terms of various common constructs: procedure calls, pointer indirections, assignments, etc. From this he wrote the Dhrystone benchmark to correspond to a representative mix. Dhrystone was published in Ada, with the C version for Unix developed by Rick Richardson ("version 1.1") greatly contributing to its popularity. Dhrystone vs. Whetstone The Dhrystone benchmark contains no floating point operations, thus the name is a p ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Million Instructions Per Second

Instructions per second (IPS) is a measure of a computer's processor speed. For complex instruction set computers (CISCs), different instructions take different amounts of time, so the value measured depends on the instruction mix; even for comparing processors in the same family the IPS measurement can be problematic. Many reported IPS values have represented "peak" execution rates on artificial instruction sequences with few branches and no cache contention, whereas realistic workloads typically lead to significantly lower IPS values. Memory hierarchy also greatly affects processor performance, an issue barely considered in IPS calculations. Because of these problems, synthetic benchmarks such as Dhrystone are now generally used to estimate computer performance in commonly used applications, and raw IPS has fallen into disuse. The term is commonly used in association with a metric prefix (k, M, G, T, P, or E) to form kilo instructions per second (kIPS), mega instructio ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Whetstone (benchmark)

The Whetstone benchmark is a synthetic benchmark for evaluating the performance of computers. It was first written in ALGOL 60 in 1972 at the Technical Support Unit of the Department of Trade and Industry (later part of the Central Computer and Telecommunications Agency) in the United Kingdom. It was derived from statistics on program behaviour gathered on the KDF9 computer at NPL National Physical Laboratory, using a modified version of its Whetstone ALGOL 60 compiler. The workload on the machine was represented as a set of frequencies of execution of the 124 instructions of the Whetstone Code. The Whetstone Compiler was built at the Atomic Power Division of the English Electric Company in Whetstone, Leicestershire, England, hence its name. Dr. B.A. Wichman at NPL produced a set of 42 simple ALGOL 60 statements, which in a suitable combination matched the execution statistics. To make a more practical benchmark Harold Curnow of TSU wrote a program incorporating the 42 statemen ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Benchmark (computing)

In computing, a benchmark is the act of running a computer program, a set of programs, or other operations, in order to assess the relative performance of an object, normally by running a number of standard tests and trials against it. The term ''benchmark'' is also commonly utilized for the purposes of elaborately designed benchmarking programs themselves. Benchmarking is usually associated with assessing performance characteristics of computer hardware, for example, the floating point operation performance of a CPU, but there are circumstances when the technique is also applicable to software. Software benchmarks are, for example, run against compilers or database management systems (DBMS). Benchmarks provide a method of comparing the performance of various subsystems across different chip/system architectures. Benchmarking as a part of continuous integration is called Continuous Benchmarking. Purpose As computer architecture advanced, it became more difficult to compa ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

SPECint

SPEC INT is a computer benchmark specification for CPU integer processing power. It is maintained by the Standard Performance Evaluation Corporation (SPEC). SPEC INT is the integer performance testing component of the SPEC test suite. The first SPEC test suite, CPU92, was announced in 1992. It was followed by CPU95, CPU2000, and CPU2006. The latest standard is SPEC CPU 2017 and consists of SPEC speed and SPEC rate (aka SPECCPU_2017). SPEC INT 2006 CPU2006 is a set of benchmarks designed to test the CPU performance of a modern server computer system. It is split into two components, the first being CINT2006, the other being CFP2006 ( SPECfp), for floating point testing. SPEC defines a base runtime for each of the 12 benchmark programs. For SPECint2006, that number ranges from 1000 to 3000 seconds. The timed test is run on the system, and the time of the test system is compared to the reference time, and a ratio is computed. That ratio becomes the SPEC INT score for that tes ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Geekbench

Geekbench is a proprietary and freemium cross-platform utility for benchmarking the central processing unit (CPU) and graphics processing unit (GPU) of computers, laptops, tablets, and phones. History Geekbench began as a benchmark for Mac OS X and Windows, and is now a cross-platform benchmark that supports macOS, Windows, Linux, Android and iOS. In version 4, Geekbench started measuring GPU performance in areas such as image processing and computer vision. In version 5, Geekbench dropped support for IA-32. In version 6, the current version, Geekbench includes CPU and GPU compute benchmarks. Usage It uses a scoring system that separates single-core and multi-core performance, and workloads designed to simulate real-world scenarios. The software benchmark is available for macOS, Windows, Linux, Android and iOS. Free users are required to upload test results online in order to run the benchmark. In 2013, the usefulness of the scores from earlier versions of Geekbench (up to ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Standard Performance Evaluation Corporation

The Standard Performance Evaluation Corporation (SPEC) is a non-profit consortium that establishes and maintains standardized benchmarks and performance evaluation tools for new generations of computing systems. SPEC was founded in 1988 and its membership comprises over 120 computer hardware and software vendors, educational institutions, research organizations, and government agencies internationally. SPEC benchmarks and tools are widely used to evaluate the performance of computer systems; the test results are published on the SPEC website. External links * Official List of SPEC Benchmarks Computer performance Evaluation of computers Companies established in 1988 Companies based in Virginia Standards organizations in the United States {{Compu-stub ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Data Cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (MMU) whi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

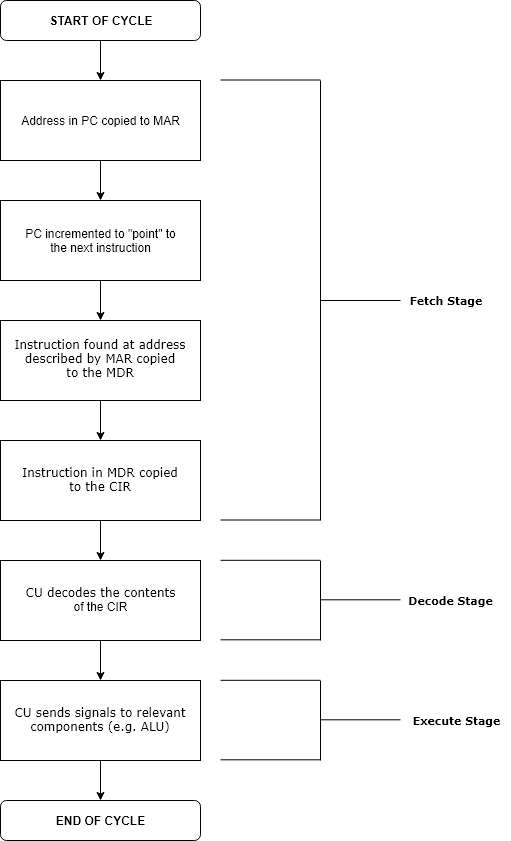

Instruction Fetch

The instruction cycle (also known as the fetch–decode–execute cycle, or simply the fetch–execute cycle) is the cycle that the central processing unit (CPU) follows from boot-up until the computer has shut down in order to process instructions. It is composed of three main stages: the fetch stage, the decode stage, and the execute stage. In simpler CPUs, the instruction cycle is executed sequentially, each instruction being processed before the next one is started. In most modern CPUs, the instruction cycles are instead executed concurrently, and often in parallel, through an instruction pipeline: the next instruction starts being processed before the previous instruction has finished, which is possible because the cycle is broken up into separate steps. Role of components Program counter The program counter (PC) is a register that holds the memory address of the next instruction to be executed. After each instruction copy to the memory address register (MAR), the PC can ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Instruction Cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which stores copies of the data from frequently used main memory locations. Most CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level 1. The cache memory is typically implemented with static random-access memory (SRAM), in modern CPUs by far the largest part of them by chip area, but SRAM is not always used for all levels (of I- or D-cache), or even any level, sometimes some latter or all levels are implemented with eDRAM. Other types of caches exist (that are not counted towards the "cache size" of the most important caches mentioned above), such as the translation lookaside buffer (TLB) which is part of the memory management unit (MMU) w ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

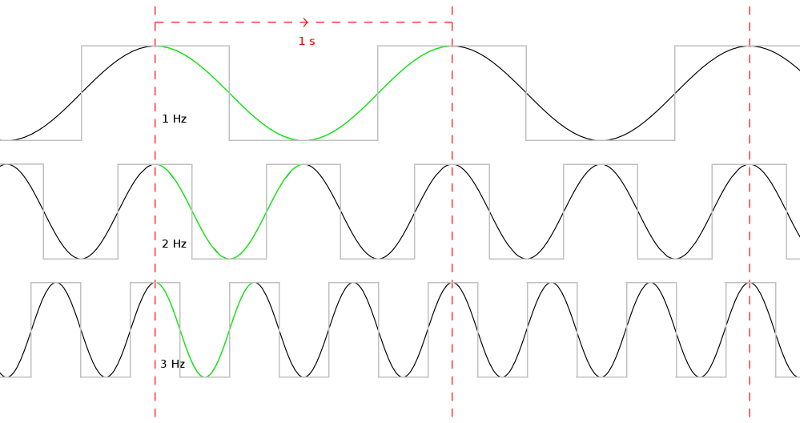

Clock Rate

Clock rate or clock speed in computing typically refers to the frequency at which the clock generator of a processor can generate pulses used to synchronize the operations of its components. It is used as an indicator of the processor's speed. Clock rate is measured in the SI unit of frequency hertz (Hz). The clock rate of the first generation of computers was measured in hertz or kilohertz (kHz), the first personal computers from the 1970s through the 1980s had clock rates measured in megahertz (MHz). In the 21st century the speed of modern CPUs is commonly advertised in gigahertz (GHz). This metric is most useful when comparing processors within the same family, holding constant other features that may affect performance. Determining factors Binning Manufacturers of modern processors typically charge higher prices for processors that operate at higher clock rates, a practice called binning. For a given CPU, the clock rates are determined at the end of the manufact ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

VAX 11/780

The VAX-11 is a discontinued family of 32-bit superminicomputers, running the Virtual Address eXtension (VAX) instruction set architecture (ISA), developed and manufactured by Digital Equipment Corporation (DEC). Development began in 1976. In addition to being powerful machines in their own right, they also offer the additional ability to run user mode PDP-11 code (thus the -11 in VAX-11), offering an upward compatible path for existing customers. The first machine in the series, the VAX-11/780, was announced in October 1977. Its former competitors in the minicomputer space, like Data General and Hewlett-Packard, were unable to successfully respond to the introduction and rapid update of the VAX design. DEC followed the VAX-11/780 with the lower-cost 11/750, and the even lower cost 11/730 and 11/725 models in 1982. More powerful models, initially known as the VAX-11/790 and VAX-11/795, were instead rebranded as the VAX 8600 series. The VAX-11 line was discontinued in 1988, havin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |