|

Harvard Architecture

The Harvard architecture is a computer architecture with separate computer storage, storage and signal pathways for Machine code, instructions and data. It is often contrasted with the von Neumann architecture, where program instructions and data share the same memory and pathways. This architecture is often used in real-time processing or low-power applications. The term is often stated as having originated from the Harvard Mark I relay-based computer, which stored instructions on punched tape (24 bits wide) and data in electro-mechanical counters. These early machines had data storage entirely contained within the central processing unit, and provided no access to the instruction storage as data. Programs needed to be loaded by an operator; the processor could not Booting, initialize itself. However, in the only peer-reviewed paper on the topic published in 2022 the author states that: * 'The term "Harvard architecture" was coined decades later, in the context of microcontr ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Read-only Memory

Read-only memory (ROM) is a type of non-volatile memory used in computers and other electronic devices. Data stored in ROM cannot be electronically modified after the manufacture of the memory device. Read-only memory is useful for storing software that is rarely changed during the life of the system, also known as firmware. Software applications, such as video games, for programmable devices can be distributed as ROM cartridge, plug-in cartridges containing ROM. Strictly speaking, ''read-only memory'' refers to hard-wired memory, such as diode matrix or a #Solid-state ROM, mask ROM integrated circuit (IC), that cannot be electronically changed after manufacture. Although discrete circuits can be altered in principle, through the addition of Jump wire, bodge wires and the removal or replacement of components, ICs cannot. Correction of errors, or updates to the software, require new devices to be manufactured and to replace the installed device. Floating-gate ROM semiconductor ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Intel 80486

The Intel 486, officially named i486 and also known as 80486, is a microprocessor introduced in 1989. It is a higher-performance follow-up to the i386, Intel 386. It represents the fourth generation of binary compatible CPUs following the Intel 8086, 8086 of 1978, the Intel 80286 of 1982, and 1985's i386. It was the first tightly-instruction pipeline, pipelined x86 design as well as the first x86 chip to include more than one million transistors. It offered a large on-chip Cache (computing), cache and an integrated floating-point unit. When it was announced, the initial performance was originally published between 15 and 20 VAX Unit of Performance, VAX MIPS, between 37,000 and 49,000 Dhrystone, dhrystones per second, and between 6.1 and 8.2 double-precision Whetstone (benchmark), megawhetstones per second for both 25 and 33 MHz version. A typical 50 MHz i486 executes 41 million instructions per second Dhrystone MIPS and SPECint, SPEC integer rating of 27.9.Chen, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Memory Bound

Memory bound refers to a situation in which the time to complete a given computational problem is decided primarily by the amount of free memory required to hold the working data. This is in contrast to algorithms that are compute-bound, where the number of elementary computation steps is the deciding factor. Memory and computation boundaries can sometimes be traded against each other, e.g. by saving and reusing preliminary results or using lookup tables. Memory-bound functions and memory functions Memory-bound functions and memory functions are related in that both involve extensive memory access, but a distinction exists between the two. Memory functions use a dynamic programming technique called memoization in order to relieve the inefficiency of recursion that might occur. It is based on the simple idea of calculating and storing solutions to subproblems so that the solutions can be reused later without recalculating the subproblems again. The best known example that take ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Machine Language

In computer programming, machine code is computer code consisting of machine language instructions, which are used to control a computer's central processing unit (CPU). For conventional binary computers, machine code is the binaryOn nonbinary machines it is, e.g., a decimal representation. representation of a computer program that is actually read and interpreted by the computer. A program in machine code consists of a sequence of machine instructions (possibly interspersed with data). Each machine code instruction causes the CPU to perform a specific task. Examples of such tasks include: # Load a word from memory to a CPU register # Execute an arithmetic logic unit (ALU) operation on one or more registers or memory locations # Jump or skip to an instruction that is not the next one In general, each architecture family (e.g., x86, ARM) has its own instruction set architecture (ISA), and hence its own specific machine code language. There are exceptions, such as the V ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Function Table

In computer science, a dispatch table is a table of pointers or memory addresses to functions or methods. Use of such a table is a common technique when implementing late binding in object-oriented programming. In different programming languages Perl The following shows one way to implement a dispatch table in Perl, using a hash to store references to code (also known as function pointers). # Define the table using one anonymous code-ref and one named code-ref my %dispatch = ( "-h" => sub , "-g" => \&say_goodbye ); sub say_goodbye # Fetch the code ref from the table, and invoke it my $sub = $dispatch; print $sub ? $sub->() : "unknown argument\n"; Running this Perl program as perl greet -h will produce "hello", and running it as perl greet -g will produce "goodbye". JavaScript Following is a demo of implementing a dispatch table in JavaScript: const thingsWeCanDo = ; function doSomething(doWhat) Virtual method tables In object-oriented programming ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Text String

In computer programming, a string is traditionally a sequence of characters, either as a literal constant or as some kind of variable. The latter may allow its elements to be mutated and the length changed, or it may be fixed (after creation). A string is often implemented as an array data structure of bytes (or words) that stores a sequence of elements, typically characters, using some character encoding. More general, ''string'' may also denote a sequence (or list) of data other than just characters. Depending on the programming language and precise data type used, a variable declared to be a string may either cause storage in memory to be statically allocated for a predetermined maximum length or employ dynamic allocation to allow it to hold a variable number of elements. When a string appears literally in source code, it is known as a string literal or an anonymous string. In formal languages, which are used in mathematical logic and theoretical computer science, a strin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Atmel AVR

AVR is a family of microcontrollers developed since 1996 by Atmel, acquired by Microchip Technology in 2016. They are 8-bit RISC single-chip microcontrollers based on a modified Harvard architecture. AVR was one of the first microcontroller families to use on-chip flash memory for program storage, as opposed to Programmable read-only memory, one-time programmable ROM, EPROM, or EEPROM used by other microcontrollers at the time. AVR microcontrollers are used numerously as embedded systems. They are especially common in hobbyist and educational embedded applications, popularized by their inclusion in many of the Arduino line of open hardware development boards. The AVR 8-bit microcontroller architecture was introduced in 1997. By 2003, Atmel had shipped 500 million AVR flash microcontrollers. History The AVR architecture was conceived by two students at the Norwegian Institute of Technology (NTH), Alf-Egil Bogen and Vegard Wollan.Archived aGhostarchiveand thWayback Machine ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Flash Memory

Flash memory is an Integrated circuit, electronic Non-volatile memory, non-volatile computer memory storage medium that can be electrically erased and reprogrammed. The two main types of flash memory, NOR flash and NAND flash, are named for the NOR gate, NOR and NAND gate, NAND logic gates. Both use the same cell design, consisting of floating-gate MOSFETs. They differ at the circuit level, depending on whether the state of the bit line or word lines is pulled high or low; in NAND flash, the relationship between the bit line and the word lines resembles a NAND gate; in NOR flash, it resembles a NOR gate. Flash memory, a type of floating-gate memory, was invented by Fujio Masuoka at Toshiba in 1980 and is based on EEPROM technology. Toshiba began marketing flash memory in 1987. EPROMs had to be erased completely before they could be rewritten. NAND flash memory, however, may be erased, written, and read in blocks (or pages), which generally are much smaller than the entire devi ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Power ISA

Power ISA is a reduced instruction set computer (RISC) instruction set architecture (ISA) currently developed by the OpenPOWER Foundation, led by IBM. It was originally developed by IBM and the now-defunct Power.org industry group. Power ISA is an evolution of the PowerPC ISA, created by the mergers of the core PowerPC ISA and the optional Book E for embedded applications. The merger of these two components in 2006 was led by Power.org founders IBM and Freescale Semiconductor. Prior to version 3.0, the ISA is divided into several categories. Processors implement a set of these categories as required for their task. Different classes of processors are required to implement certain categories, for example a server-class processor includes the categories: ''Base'', ''Server'', ''Floating-Point'', ''64-Bit'', etc. All processors implement the Base category. Power ISA is a RISC load/store architecture. It has multiple sets of registers: * ''32'' × 32-bit or 64-bit general- ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Architecture

ARM (stylised in lowercase as arm, formerly an acronym for Advanced RISC Machines and originally Acorn RISC Machine) is a family of reduced instruction set computer, RISC instruction set architectures (ISAs) for central processing unit, computer processors. Arm Holdings develops the ISAs and licenses them to other companies, who build the physical devices that use the instruction set. It also designs and licenses semiconductor intellectual property core, cores that implement these ISAs. Due to their low costs, low power consumption, and low heat generation, ARM processors are useful for light, portable, battery-powered devices, including smartphones, laptops, and tablet computers, as well as embedded systems. However, ARM processors are also used for desktop computer, desktops and server (computing), servers, including Fugaku (supercomputer), Fugaku, the world's fastest supercomputer from 2020 to 2022. With over 230 billion ARM chips produced, , ARM is the most widely used ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

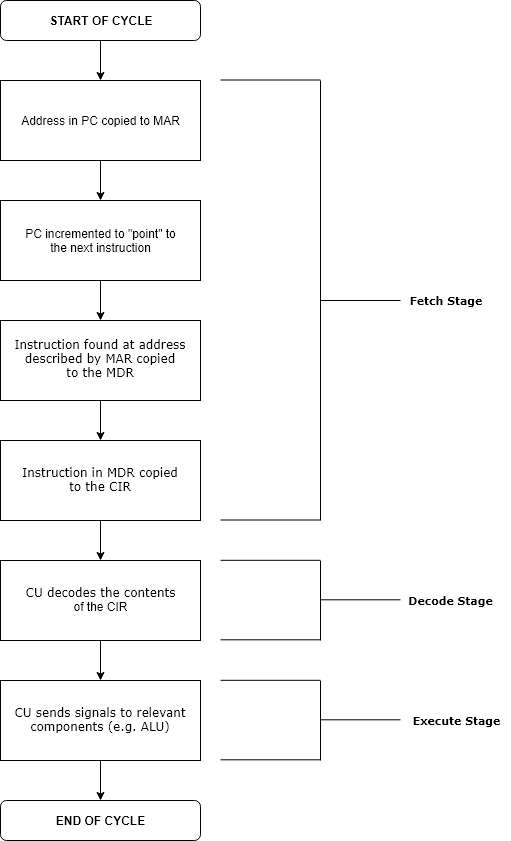

Instruction Fetch

The instruction cycle (also known as the fetch–decode–execute cycle, or simply the fetch–execute cycle) is the cycle that the central processing unit (CPU) follows from boot-up until the computer has shut down in order to process instructions. It is composed of three main stages: the fetch stage, the decode stage, and the execute stage. In simpler CPUs, the instruction cycle is executed sequentially, each instruction being processed before the next one is started. In most modern CPUs, the instruction cycles are instead executed concurrently, and often in parallel, through an instruction pipeline: the next instruction starts being processed before the previous instruction has finished, which is possible because the cycle is broken up into separate steps. Role of components Program counter The program counter (PC) is a register that holds the memory address of the next instruction to be executed. After each instruction copy to the memory address register (MAR), the PC can ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |