|

Firefly (cache Coherence Protocol)

The Firefly cache coherence protocol is the schema used in the DEC Firefly multiprocessor workstation, developed by DEC Systems Research Center. This protocol is a 3 State Write Update Cache Coherence Protocol. Unlike the Dragon protocol, the Firefly protocol updates the Main Memory as well as the Local caches on Write Update Bus Transition. Thus the Shared Clean and Shared Modified States present in case of Dragon Protocol, are not distinguished between in case of Firefly Protocol. States In this protocol, the following states can be assigned to each block: * Valid-Exclusive(V): The cache block is valid, clean and only resides in one cache. * Shared(S): The cache block is valid, clean and may reside in multiple caches. * Dirty(D): The block is the only copy of the memory and it is dirty i.e. its value has been modified since being brought from the memory. This is the only state that generates a write-back when the block is replaced in the cache. These states correspond to the ' ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Cache Coherence

In computer architecture, cache coherence is the uniformity of shared resource data that is stored in multiple local caches. In a cache coherent system, if multiple clients have a cached copy of the same region of a shared memory resource, all copies are the same. Without cache coherence, a change made to the region by one client may not be seen by others, and errors can result when the data used by different clients is mismatched. A cache coherence protocol is used to maintain cache coherency. The two main types are snooping and directory-based protocols. Cache coherence is of particular relevance in multiprocessing systems, where each CPU may have its own local cache of a shared memory resource. Overview In a shared memory multiprocessor system with a separate cache memory for each processor, it is possible to have many copies of shared data: one copy in the main memory and one in the local cache of each processor that requested it. When one of the copies of data is c ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

DEC Firefly

The Firefly was a shared memory asymmetric multiprocessor workstation, developed by the Systems Research Center, a research organization within Digital Equipment Corporation. The first version built contained up to seven MicroVAX 78032 microprocessors. The cache from each of the microprocessors kept a consistent view of the same main memory using a cache coherency algorithm, the Firefly protocol. The second version of the Firefly used faster CVAX 78034 microprocessors. It was later introduced as a product by DEC as the VAXstation 3520/3540 codenamed ''Firefox''. Hardware description The Firefly was an asymmetric multiprocessor specialized racked computer as only one of the microprocessors had access to a Q-Bus interface that implemented the I/O subsystem. Processors The Firefly contained a primary processor board and zero, one, two or three secondary processor boards. These processor boards were 8 by 10 inches large. The primary processor board contained a microp ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

DEC Systems Research Center

The Systems Research Center (SRC) was a research laboratory created by Digital Equipment Corporation (DEC) in 1984, in Palo Alto, California. DEC SRC was founded by a group of computer scientists, led by Robert Taylor, who left the Computer Science Laboratory (CSL) of Xerox PARC after an internal power struggle. SRC survived the takeover of DEC by Compaq in 1998. It was renamed to "Compaq Systems Research Center". When Compaq was acquired by Hewlett-Packard in 2002, SRC was merged with other HP corporate research labs and relocated there. After Taylor's retirement, the lab was directed by Roy Levin and then by Lyle Ramshaw. Some of the critical developments made at SRC include the Modula-3 programming language; the snoopy cache, used in the first multiprocessor workstation, the Firefly, built from MicroVAX 78032 microprocessors; the first multi-threaded Unix system, Taos; the first user interface editor; early networked window systems, Trestle. AltaVista was jointly deve ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

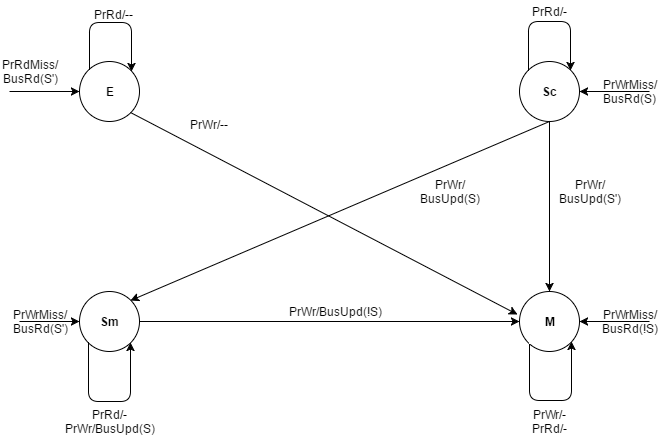

Dragon Protocol

The Dragon Protocol is an update based cache coherence protocol used in multi-processor systems. Write propagation is performed by directly updating all the cached values across multiple processors. Update based protocols such as the Dragon protocol perform efficiently when a write to a cache block is followed by several reads made by other processors, since the updated cache block is readily available across caches associated with all the processors. States Each cache block resides in one of the four states: exclusive-clean, shared-clean, shared-modified and modify. * Exclusive-clean (E): This means that the cache block was first fetched by the current processor and has not been accessed by any other processor since. * Shared clean (Sc): This means that the cache block definitely exists in multiple processor’s caches, and that the current processor is not the last one to write the block. States E and Sc are maintained separately by the protocol to prevent read-write operations ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

MESI Protocol

The MESI protocol is an invalidate-based cache coherence protocol, and is one of the most common protocols that support write-back caches. It is also known as the Illinois protocol due to its development at the University of Illinois at Urbana-Champaign. Write back caches can save considerable bandwidth generally wasted on a write through cache. There is always a dirty state present in write-back caches that indicates that the data in the cache is different from that in the main memory. The Illinois Protocol requires a cache-to-cache transfer on a miss if the block resides in another cache. This protocol reduces the number of main memory transactions with respect to the MSI protocol. This marks a significant improvement in performance. States The letters in the acronym MESI represent four exclusive states that a cache line can be marked with (encoded using two additional bits): ;Modified (M): The cache line is present only in the current cache, and is ''dirty'' - it has been m ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Bus Sniffing

Bus snooping or bus sniffing is a scheme by which a coherency controller (snooper) in a cache (a snoopy cache) monitors or snoops the bus transactions, and its goal is to maintain a cache coherency in distributed shared memory systems. This scheme was introduced by Ravishankar and Goodman in 1983, under the name "write-once" cache coherency. A cache containing a coherency controller (snooper) is called a snoopy cache. How it works When specific data are shared by several caches and a processor modifies the value of the shared data, the change must be propagated to all the other caches which have a copy of the data. This change propagation prevents the system from violating cache coherency. The notification of data change can be done by bus snooping. All the snoopers monitor every transaction on a bus. If a transaction modifying a shared cache block appears on a bus, all the snoopers check whether their caches have the same copy of the shared block. If a cache has a copy of the s ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Firefly State Transition Diagram

The Lampyridae are a family of elateroid beetles with more than 2,000 described species, many of which are light-emitting. They are soft-bodied beetles commonly called fireflies, lightning bugs, or glowworms for their conspicuous production of light, mainly during twilight, to attract mates. The type species is ''Lampyris noctiluca'', the common glow-worm of Europe. Light production in the Lampyridae is thought to have originated as a warning signal that the larvae were distasteful. This ability to create light was then co-opted as a mating signal and, in a further development, adult female fireflies of the genus ''Photuris'' mimic the flash pattern of the ''Photinus'' beetle to trap their males as prey. Fireflies are found in temperate and tropical climates. Many live in marshes or in wet, wooded areas where their larvae have abundant sources of food. Although all known fireflies glow as larvae, only some species produce light in their adult stage, and the location of ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Cache Coherence

In computer architecture, cache coherence is the uniformity of shared resource data that is stored in multiple local caches. In a cache coherent system, if multiple clients have a cached copy of the same region of a shared memory resource, all copies are the same. Without cache coherence, a change made to the region by one client may not be seen by others, and errors can result when the data used by different clients is mismatched. A cache coherence protocol is used to maintain cache coherency. The two main types are snooping and directory-based protocols. Cache coherence is of particular relevance in multiprocessing systems, where each CPU may have its own local cache of a shared memory resource. Overview In a shared memory multiprocessor system with a separate cache memory for each processor, it is possible to have many copies of shared data: one copy in the main memory and one in the local cache of each processor that requested it. When one of the copies of data is c ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

MSI Protocol

In computing, the MSI protocol - a basic Cache coherence, cache-coherence protocol - operates in multiprocessor systems. As with other cache coherency protocols, the letters of the protocol name identify the possible states in which a cache line can be. Overview In MSI, each block contained inside a cache can have one of three possible states: *Modified: The block has been modified in the CPU cache, cache. The data in the cache is then inconsistent with the backing store (e.g. Main memory, memory). A cache with a block in the "M" state has the responsibility to write the block to the backing store when it is evicted. *Shared: This block is unmodified and exists in read-only state in at least one cache. The cache can evict the data without writing it to the backing store. *Invalid: This block is either not present in the current cache or has been invalidated by a bus request, and must be fetched from memory or another CPU cache, cache if the block is to be stored in this cac ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |