MasPar on:

[Wikipedia]

[Google]

[Amazon]

MasPar Computer Corporation was a

While Kalb was the vice-president of the division of

While Kalb was the vice-president of the division of

"MasPar: Massively Parallel Computers – 32 cores on a chip"

* increasing the connectivity of each processor element to 8 neighbors from 4. * adding a global interconnect for all of the processing elements, which was a triple-redundant switch which was easier to implement than a full

Company Overview of Neovista Software, Inc.

/ref>DSstar Vol. 5 No. 27 (July 3, 2001)

MasPar is unique in being a manufacturer of

MasPar is unique in being a manufacturer of  The MP-2 PE chip contains 32 processor elements, each a full 32-bit ALU with floating point, registers, and a

The MP-2 PE chip contains 32 processor elements, each a full 32-bit ALU with floating point, registers, and a  The 32 PEs on a chip are clustered into two groups sharing a common memory interface, or M-machine, for access. A global scoreboard keeps track of memory and register usage. The path to memory is 16 bits wide. Both big and little endian formats are supported. Each processor has its own 64 Kbyte of memory. Both direct and indirect data memory addressing are supported.

The chip is implemented in 1.0-

The 32 PEs on a chip are clustered into two groups sharing a common memory interface, or M-machine, for access. A global scoreboard keeps track of memory and register usage. The path to memory is 16 bits wide. Both big and little endian formats are supported. Each processor has its own 64 Kbyte of memory. Both direct and indirect data memory addressing are supported.

The chip is implemented in 1.0-

Ian Kaplan's history of venture capital

{{DEFAULTSORT:Maspar American companies established in 1987 American companies disestablished in 1999 Companies based in Sunnyvale, California Computer companies established in 1987 Computer companies disestablished in 1999 Defunct computer companies of the United States Defunct computer hardware companies Massively parallel computers Parallel computing Serial computers SIMD computing Supercomputers

minisupercomputer

Minisupercomputers constituted a short-lived class of computers that emerged in the mid-1980s, characterized by the combination of vector processing and small-scale multiprocessing. As scientific computing using vector processors became more po ...

vendor that was founded in 1987 by Jeff Kalb. The company was based in Sunnyvale, California

Sunnyvale () is a city located in the Santa Clara Valley in northwest Santa Clara County in the U.S. state of California.

Sunnyvale lies along the historic El Camino Real and Highway 101 and is bordered by portions of San Jose to the nor ...

.

History

While Kalb was the vice-president of the division of

While Kalb was the vice-president of the division of Digital Equipment Corporation

Digital Equipment Corporation (DEC ), using the trademark Digital, was a major American company in the computer industry from the 1960s to the 1990s. The company was co-founded by Ken Olsen and Harlan Anderson in 1957. Olsen was president un ...

(DEC) that built integrated circuit

An integrated circuit or monolithic integrated circuit (also referred to as an IC, a chip, or a microchip) is a set of electronic circuits on one small flat piece (or "chip") of semiconductor material, usually silicon. Large numbers of tiny ...

s, some researchers in that division were building a supercomputer based on the Goodyear MPP

The Goodyear Massively Parallel Processor (MPP) was a

massively parallel processing supercomputer built by Goodyear Aerospace

for the NASA Goddard Space Flight Center. It was designed to deliver enormous computational power at lower cost than oth ...

(massively parallel processor) supercomputer. The DEC researchers enhanced the architecture by:

* making the processor elements to be 4-bit

In computer architecture, 4-bit integers, or other data units are those that are 4 bits wide. Also, 4-bit central processing unit (CPU) and arithmetic logic unit (ALU) architectures are those that are based on registers, or data buses of that si ...

instead of 1-bit

John Culver"MasPar: Massively Parallel Computers – 32 cores on a chip"

* increasing the connectivity of each processor element to 8 neighbors from 4. * adding a global interconnect for all of the processing elements, which was a triple-redundant switch which was easier to implement than a full

crossbar switch

In electronics and telecommunications, a crossbar switch (cross-point switch, matrix switch) is a collection of switches arranged in a matrix configuration. A crossbar switch has multiple input and output lines that form a crossed pattern of int ...

.

After Digital decided not to commercialize the research project, Kalb decided to start a company to sell this minisupercomputer. In 1990, the first generation product MP-1 was delivered. In 1992, the follow-on MP-2 was shipped. The company shipped more than 200 systems.

MasPar along with nCUBE

nCUBE was a series of parallel computing computers from the company of the same name. Early generations of the hardware used a custom microprocessor. With its final generations of servers, nCUBE no longer designed custom microprocessors for mach ...

criticized the open government support, by DARPA

The Defense Advanced Research Projects Agency (DARPA) is a research and development agency of the United States Department of Defense responsible for the development of emerging technologies for use by the military.

Originally known as the A ...

, of competitors Intel

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California. It is the world's largest semiconductor chip manufacturer by revenue, and is one of the developers of the x86 ser ...

for their hypercube Personal SuperComputers ( iPSC) and the Thinking Machines

Thinking Machines Corporation was a supercomputer manufacturer and artificial intelligence (AI) company, founded in Waltham, Massachusetts, in 1983 by Sheryl Handler and W. Daniel "Danny" Hillis to turn Hillis's doctoral work at the Massachuset ...

Connection Machine

A Connection Machine (CM) is a member of a series of massively parallel supercomputers that grew out of doctoral research on alternatives to the traditional von Neumann architecture of computers by Danny Hillis at Massachusetts Institute of Techno ...

on the pages of ''Datamation

''Datamation'' is a computer magazine that was published in print form in the United States between 1957 and 1998,

''.

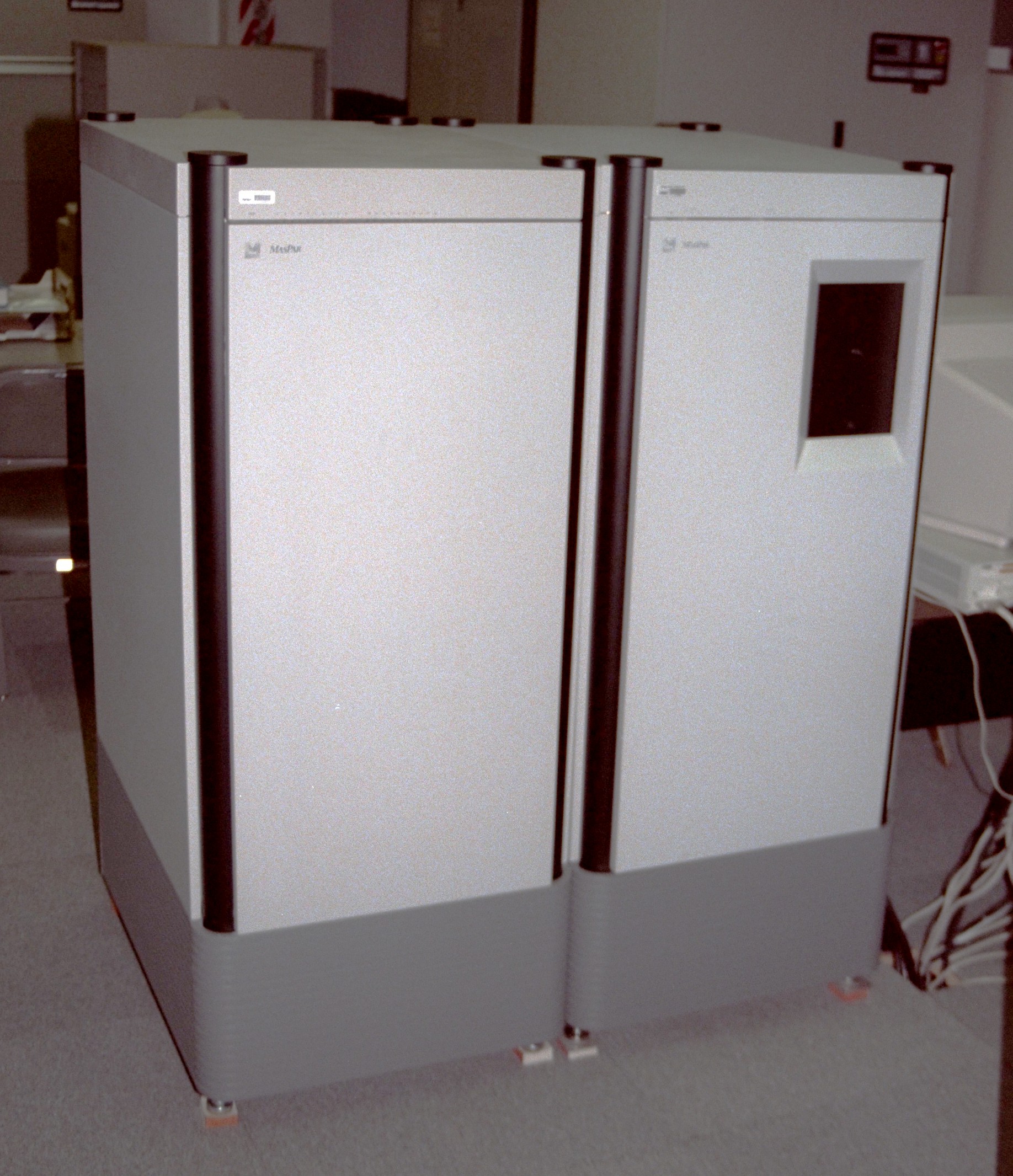

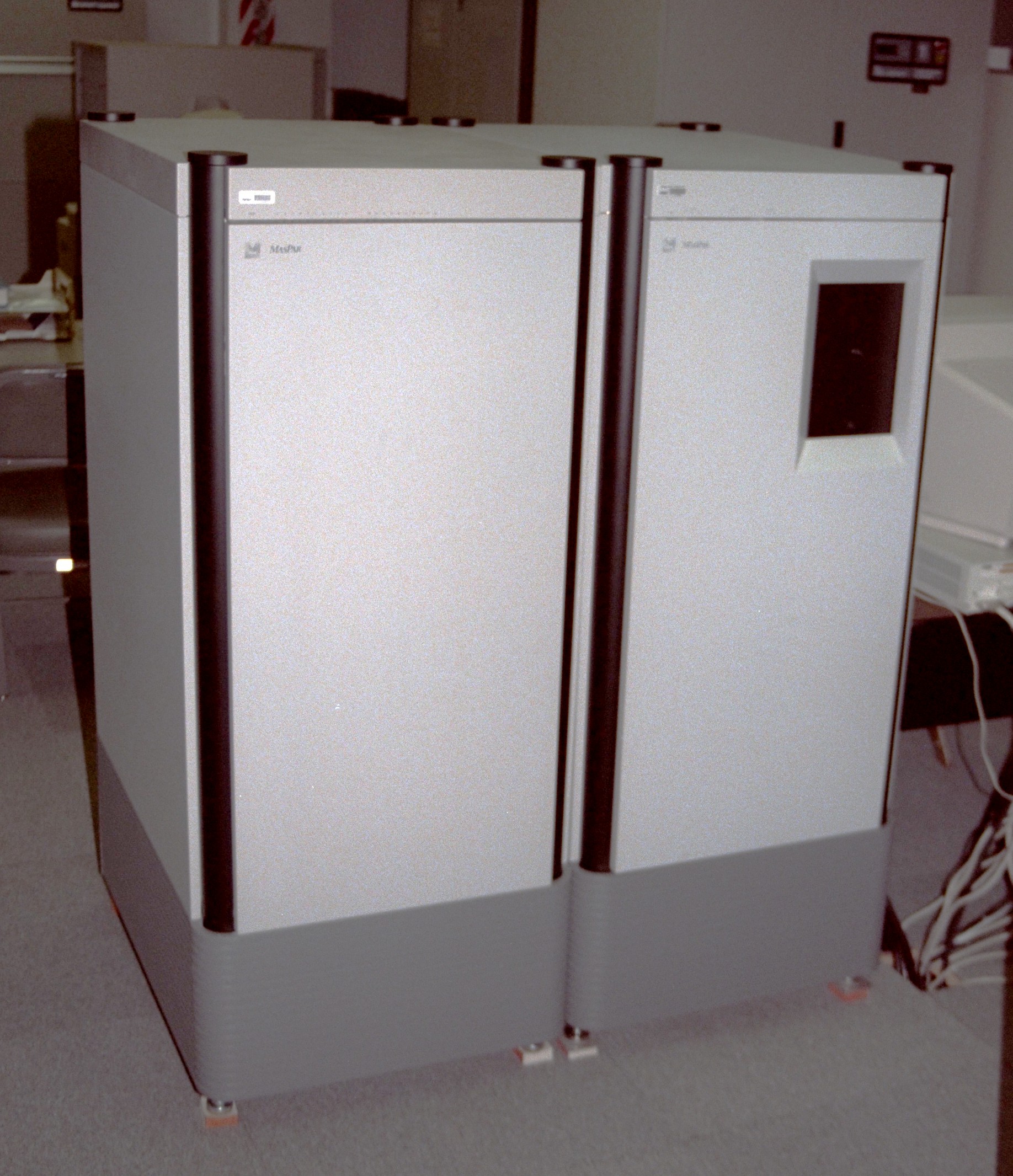

Samples of MasPar MPs, from the NASA

The National Aeronautics and Space Administration (NASA ) is an independent agency of the US federal government responsible for the civil space program, aeronautics research, and space research.

NASA was established in 1958, succeedin ...

Goddard Space Flight Center

The Goddard Space Flight Center (GSFC) is a major NASA space research laboratory located approximately northeast of Washington, D.C. in Greenbelt, Maryland, United States. Established on May 1, 1959 as NASA's first space flight center, GSFC empl ...

, are in storage at the Computer History Museum

The Computer History Museum (CHM) is a museum of computer history, located in Mountain View, California. The museum presents stories and artifacts of Silicon Valley and the information age, and explores the computing revolution and its impact o ...

.

MasPar offered a family of SIMD

Single instruction, multiple data (SIMD) is a type of parallel processing in Flynn's taxonomy. SIMD can be internal (part of the hardware design) and it can be directly accessible through an instruction set architecture (ISA), but it shoul ...

machines, second sourced by DEC. The processor units are proprietary.

There was no MP-3. MasPar exited the computer hardware business in June 1996, halting all hardware development and transforming itself into a new data mining software company called NeoVista Software. NeoVista was acquired by Accrue Software in 1999, which in turn sold the division to JDA Software

Blue Yonder (formerly JDA Software Group) is an American software and consultancy company owned by multinational conglomerate Panasonic. Blue Yonder provides supply chain management, manufacturing planning, retail planning, store operations and c ...

in 2001.Bloomberg BusinessweekCompany Overview of Neovista Software, Inc.

/ref>DSstar Vol. 5 No. 27 (July 3, 2001)

Hardware

MasPar is unique in being a manufacturer of

MasPar is unique in being a manufacturer of SIMD

Single instruction, multiple data (SIMD) is a type of parallel processing in Flynn's taxonomy. SIMD can be internal (part of the hardware design) and it can be directly accessible through an instruction set architecture (ISA), but it shoul ...

supercomputers (as opposed to vector machines). In this approach, a collection of ALU's listen to a program broadcast from a central source. The ALUs can do their own data fetch, but are all under control of a central Array Control Unit. There is a central clock. The emphasis is on communications efficiency, and low latency. The MasPar architecture is designed to scale, and balance processing, memory, and communication.

The Maspar MP-1 PE and the later binary-compatible Maspar MP-2 PE are full custom

Full-custom design is a methodology for designing integrated circuits by specifying the layout of each individual transistor and the interconnections between them. Alternatives to full-custom design include various forms of semi-custom design, ...

CMOS

Complementary metal–oxide–semiconductor (CMOS, pronounced "sea-moss", ) is a type of metal–oxide–semiconductor field-effect transistor (MOSFET) fabrication process that uses complementary and symmetrical pairs of p-type and n-type MOSF ...

chips, designed in-house, and fabricated by various vendors such as HP or TI.

The Array Control Unit (ACU) handles instruction fetch. It is a load-store architecture. The MasPar architecture is Harvard

Harvard University is a private Ivy League research university in Cambridge, Massachusetts. Founded in 1636 as Harvard College and named for its first benefactor, the Puritan clergyman John Harvard, it is the oldest institution of higher le ...

in a broad sense. The ACU implements a microcode

In processor design, microcode (μcode) is a technique that interposes a layer of computer organization between the central processing unit (CPU) hardware and the programmer-visible instruction set architecture of a computer. Microcode is a la ...

d instruction fetch, but achieves a RISC-like 1 instruction per clock. The Arithmetic units, ALUs with data fetch capability, are implemented 32 to a chip. Each ALU is connected in a nearest neighbor fashion to 8 others. The edge connections are brought off-chip. In this scheme, the perimeters can be toroid

In mathematics, a toroid is a surface of revolution with a hole in the middle. The axis of revolution passes through the hole and so does not intersect the surface. For example, when a rectangle is rotated around an axis parallel to one of its ...

-wrapped. Up to 16,384 units can be connected within the confines of a cabinet. A global router, essentially a cross-bar switch, provides external I/O to the processor array.

The MP-2 PE chip contains 32 processor elements, each a full 32-bit ALU with floating point, registers, and a

The MP-2 PE chip contains 32 processor elements, each a full 32-bit ALU with floating point, registers, and a barrel shifter

A barrel shifter is a digital circuit that can shift a data word by a specified number of bits without the use of any sequential logic, only pure combinational logic, i.e. it inherently provides a binary operation. It can however in theory also ...

. Only the instruction fetch feature is removed, and placed in the ACU. The PE design is literally replicated 32 times on the chip. The chip is designed to interface to DRAM

Dynamic random-access memory (dynamic RAM or DRAM) is a type of random-access semiconductor memory that stores each bit of data in a memory cell, usually consisting of a tiny capacitor and a transistor, both typically based on metal-oxid ...

, to other processor array chips, and to communication router chips.

Each ALU, called a PE slice, contains sixty four 32 bit registers that are used for both integer and floating point. The registers are both bit and byte

The byte is a unit of digital information that most commonly consists of eight bits. Historically, the byte was the number of bits used to encode a single character of text in a computer and for this reason it is the smallest addressable uni ...

addressable. The floating point unit handles single precision

Single-precision floating-point format (sometimes called FP32 or float32) is a computer number format, usually occupying 32 bits in computer memory; it represents a wide dynamic range of numeric values by using a floating radix point.

A floatin ...

and double precision

Double-precision floating-point format (sometimes called FP64 or float64) is a floating-point number format, usually occupying 64 bits in computer memory; it represents a wide dynamic range of numeric values by using a floating radix point.

Flo ...

arithmetic on IEEE

The Institute of Electrical and Electronics Engineers (IEEE) is a 501(c)(3) professional association for electronic engineering and electrical engineering (and associated disciplines) with its corporate office in New York City and its operati ...

format numbers. Each PE slice contains two registers for data memory address, and the data. Each PE also has two one-bit serial ports, one for inbound and one for outbound communication to its nearest neighbor. The direction of communication is controlled globally. The PEs also have inbound and outbound paths to a global router for I/O. A broadcast port allows a single instance of data to be "promoted" to parallel data. Alternately, global data can be 'or-ed' to a scalar result.

The serial links support 1 Mbyte/s bit-serial communication that allows coordinated register-register communication between processors. Each processor has its own local memory, implemented in DRAM. No internal memory is included on the processors. Microcoded instruction decode is used.

The 32 PEs on a chip are clustered into two groups sharing a common memory interface, or M-machine, for access. A global scoreboard keeps track of memory and register usage. The path to memory is 16 bits wide. Both big and little endian formats are supported. Each processor has its own 64 Kbyte of memory. Both direct and indirect data memory addressing are supported.

The chip is implemented in 1.0-

The 32 PEs on a chip are clustered into two groups sharing a common memory interface, or M-machine, for access. A global scoreboard keeps track of memory and register usage. The path to memory is 16 bits wide. Both big and little endian formats are supported. Each processor has its own 64 Kbyte of memory. Both direct and indirect data memory addressing are supported.

The chip is implemented in 1.0-micrometre

The micrometre (American and British English spelling differences#-re, -er, international spelling as used by the International Bureau of Weights and Measures; SI symbol: μm) or micrometer (American and British English spelling differences# ...

, two-level, metal CMOS, dissipates 0.8 watt, and is packaged in a 208-pin PQFP

A quad flat package (QFP) is a surface-mounted integrated circuit package with "gull wing" leads extending from each of the four sides. Socketing such packages is rare and through-hole mounting is not possible. Versions ranging from 32 to 304 ...

. A relatively low clock rate of 12.5 MHz is used.

The Maspar machines are front ended by a host machine, usually a VAX. They are accessed by extensions to Fortran and C. Full IEEE single- and double-precision floating point are supported.

There is no cache for the ALUs. Cache is not required, due to the memory interface operating at commensurate speed with the ALU data accesses.

The ALUs do not implement memory management

Memory management is a form of resource management applied to computer memory. The essential requirement of memory management is to provide ways to dynamically allocate portions of memory to programs at their request, and free it for reuse when ...

for data memory. The ACU uses demand paged virtual memory

In computing, virtual memory, or virtual storage is a memory management technique that provides an "idealized abstraction of the storage resources that are actually available on a given machine" which "creates the illusion to users of a very ...

for the instruction memory.

See also

*Goodyear MPP

The Goodyear Massively Parallel Processor (MPP) was a

massively parallel processing supercomputer built by Goodyear Aerospace

for the NASA Goddard Space Flight Center. It was designed to deliver enormous computational power at lower cost than oth ...

* ICL DAP

* Thinking Machines Corporation

Thinking Machines Corporation was a supercomputer manufacturer and artificial intelligence (AI) company, founded in Waltham, Massachusetts, in 1983 by Sheryl Handler and W. Daniel "Danny" Hillis to turn Hillis's doctoral work at the Massachusett ...

* Parsytec

* SUPRENUM

References

External links

Ian Kaplan's history of venture capital

{{DEFAULTSORT:Maspar American companies established in 1987 American companies disestablished in 1999 Companies based in Sunnyvale, California Computer companies established in 1987 Computer companies disestablished in 1999 Defunct computer companies of the United States Defunct computer hardware companies Massively parallel computers Parallel computing Serial computers SIMD computing Supercomputers