Intel i960 on:

[Wikipedia]

[Google]

[Amazon]

The i960 design was begun in response to the failure of Intel's

The i960 design was begun in response to the failure of Intel's

Intel

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California. It is the world's largest semiconductor chip manufacturer by revenue, and is one of the developers of the x86 ser ...

's i960 (or 80960) was a RISC

In computer engineering, a reduced instruction set computer (RISC) is a computer designed to simplify the individual instructions given to the computer to accomplish tasks. Compared to the instructions given to a complex instruction set comp ...

-based microprocessor

A microprocessor is a computer processor where the data processing logic and control is included on a single integrated circuit, or a small number of integrated circuits. The microprocessor contains the arithmetic, logic, and control circ ...

design that became popular during the early 1990s as an embedded microcontroller

A microcontroller (MCU for ''microcontroller unit'', often also MC, UC, or μC) is a small computer on a single VLSI integrated circuit (IC) chip. A microcontroller contains one or more CPUs ( processor cores) along with memory and programmabl ...

. It became a best-selling CPU in that segment, along with the competing AMD 29000

The AMD Am29000, commonly shortened to 29k, is a family of 32-bit RISC microprocessors and microcontrollers developed and fabricated by Advanced Micro Devices (AMD). Based on the seminal Berkeley RISC, the 29k added a number of significant impr ...

. In spite of its success, Intel stopped marketing the i960 in the late 1990s, as a result of a settlement with DEC whereby Intel received the rights to produce the StrongARM CPU. The processor continues to be used for a few military applications.

Origin

The i960 design was begun in response to the failure of Intel's

The i960 design was begun in response to the failure of Intel's iAPX 432

The iAPX 432 (''Intel Advanced Performance Architecture'') is a discontinued computer architecture introduced in 1981. It was Intel's first 32-bit processor design. The main processor of the architecture, the ''general data processor'', is imp ...

design of the early 1980s. The iAPX 432 was intended to directly support high-level languages that supported tagged, protected

Protection is any measure taken to guard a thing against damage caused by outside forces. Protection can be provided to physical objects, including organisms, to systems, and to intangible things like civil and political rights. Although th ...

, garbage-collected memory—such as Ada

Ada may refer to:

Places

Africa

* Ada Foah, a town in Ghana

* Ada (Ghana parliament constituency)

* Ada, Osun, a town in Nigeria

Asia

* Ada, Urmia, a village in West Azerbaijan Province, Iran

* Ada, Karaman, a village in Karaman Province, T ...

and Lisp

A lisp is a speech impairment in which a person misarticulates sibilants (, , , , , , , ). These misarticulations often result in unclear speech.

Types

* A frontal lisp occurs when the tongue is placed anterior to the target. Interdental lispin ...

—in hardware. Because of its instruction-set complexity, its multi-chip implementation, and design flaws, the iAPX 432 was very slow in comparison to other processors of its time.

In 1984, Intel and Siemens

Siemens AG ( ) is a German multinational conglomerate corporation and the largest industrial manufacturing company in Europe headquartered in Munich with branch offices abroad.

The principal divisions of the corporation are ''Industry'', ''E ...

started a joint project, ultimately called BiiN, to create a high-end, fault-tolerant, object-oriented computer system programmed entirely in Ada. Many of the original i432 team members joined this project, although a new lead architect, Glenford Myers, was brought in from IBM. The intended market for the BiiN systems was high-reliability-computer users such as banks, industrial systems, and nuclear power plants.

Intel's major contribution to the BiiN system was a new processor design, influenced by the protected-memory concepts from the i432. The new design was to include a number of features to improve performance and avoid problems that had led to the i432's downfall. The first 960 processors entered the final stages of design, known as '' taping-out'', in October 1985 and were sent to manufacturing that month, with the first working chips arriving in late 1985 and early 1986.

The BiiN effort eventually failed, due to market forces, and the 960MX was left without a use. Myers attempted to save the design by extracting several subsets of the full capability architecture created for the BiiN system. He tried to convince Intel management to market the i960 (then still known as the "P7") as a general-purpose processor, both in place of the Intel 80286

The Intel 80286 (also marketed as the iAPX 286 and often called Intel 286) is a 16-bit microprocessor that was introduced on February 1, 1982. It was the first 8086-based CPU with separate, non- multiplexed address and data buses and also the ...

and i386

The Intel 386, originally released as 80386 and later renamed i386, is a 32-bit microprocessor introduced in 1985. The first versions had 275,000 transistorsUnix

Unix (; trademarked as UNIX) is a family of multitasking, multiuser computer operating systems that derive from the original AT&T Unix, whose development started in 1969 at the Bell Labs research center by Ken Thompson, Dennis Ritchie, ...

systems, including a pitch to Steve Jobs

Steven Paul Jobs (February 24, 1955 – October 5, 2011) was an American entrepreneur, industrial designer, media proprietor, and investor. He was the co-founder, chairman, and CEO of Apple; the chairman and majority shareholder of Pixar; ...

for use in the NeXT

Next may refer to:

Arts and entertainment Film

* ''Next'' (1990 film), an animated short about William Shakespeare

* ''Next'' (2007 film), a sci-fi film starring Nicolas Cage

* '' Next: A Primer on Urban Painting'', a 2005 documentary film

Lit ...

system. Competition within and outside of Intel came not only from the i386

The Intel 386, originally released as 80386 and later renamed i386, is a 32-bit microprocessor introduced in 1985. The first versions had 275,000 transistorsi860 processor, yet another RISC processor design emerging within Intel at the time. Myers was unsuccessful at convincing Intel management to support the i960 as a general-purpose or Unix processor, but the chip found a ready market in early high-performance 32-bit embedded systems.

The lead architect of i960 was

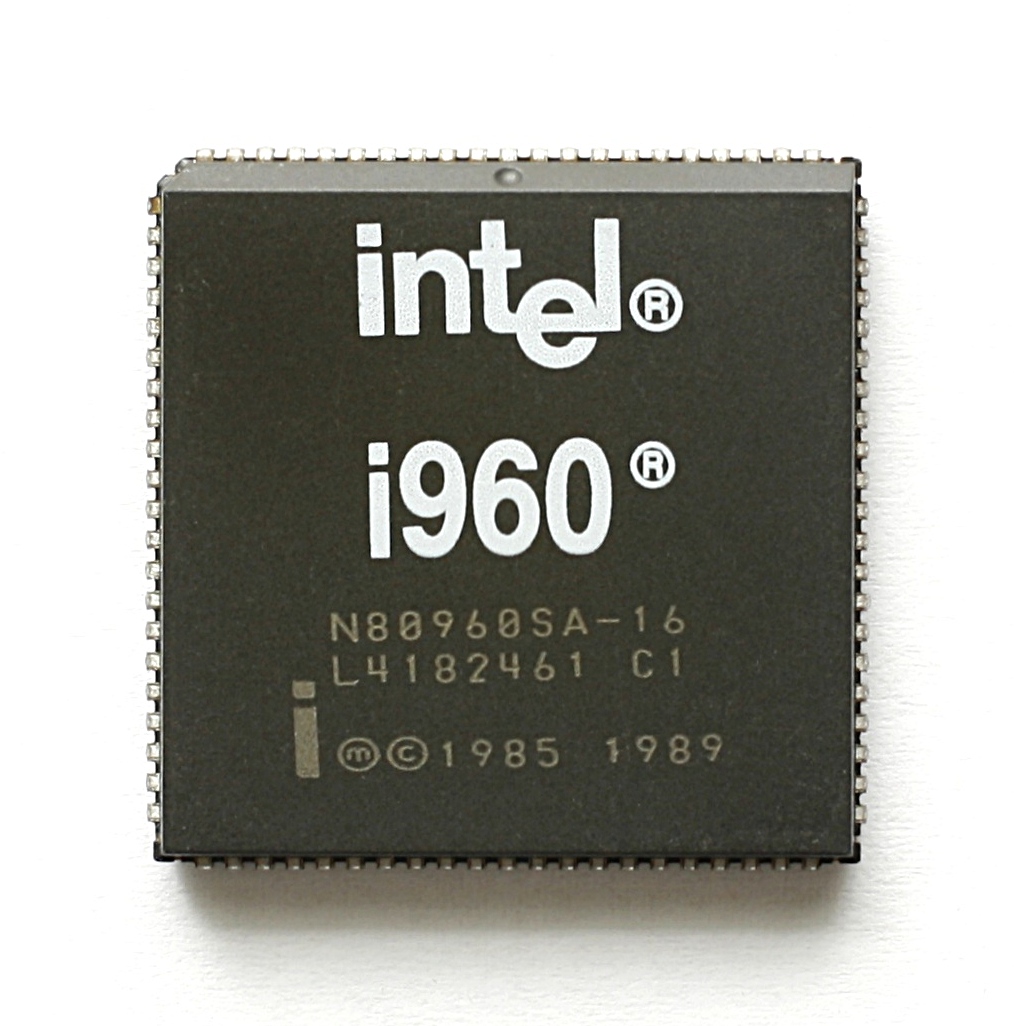

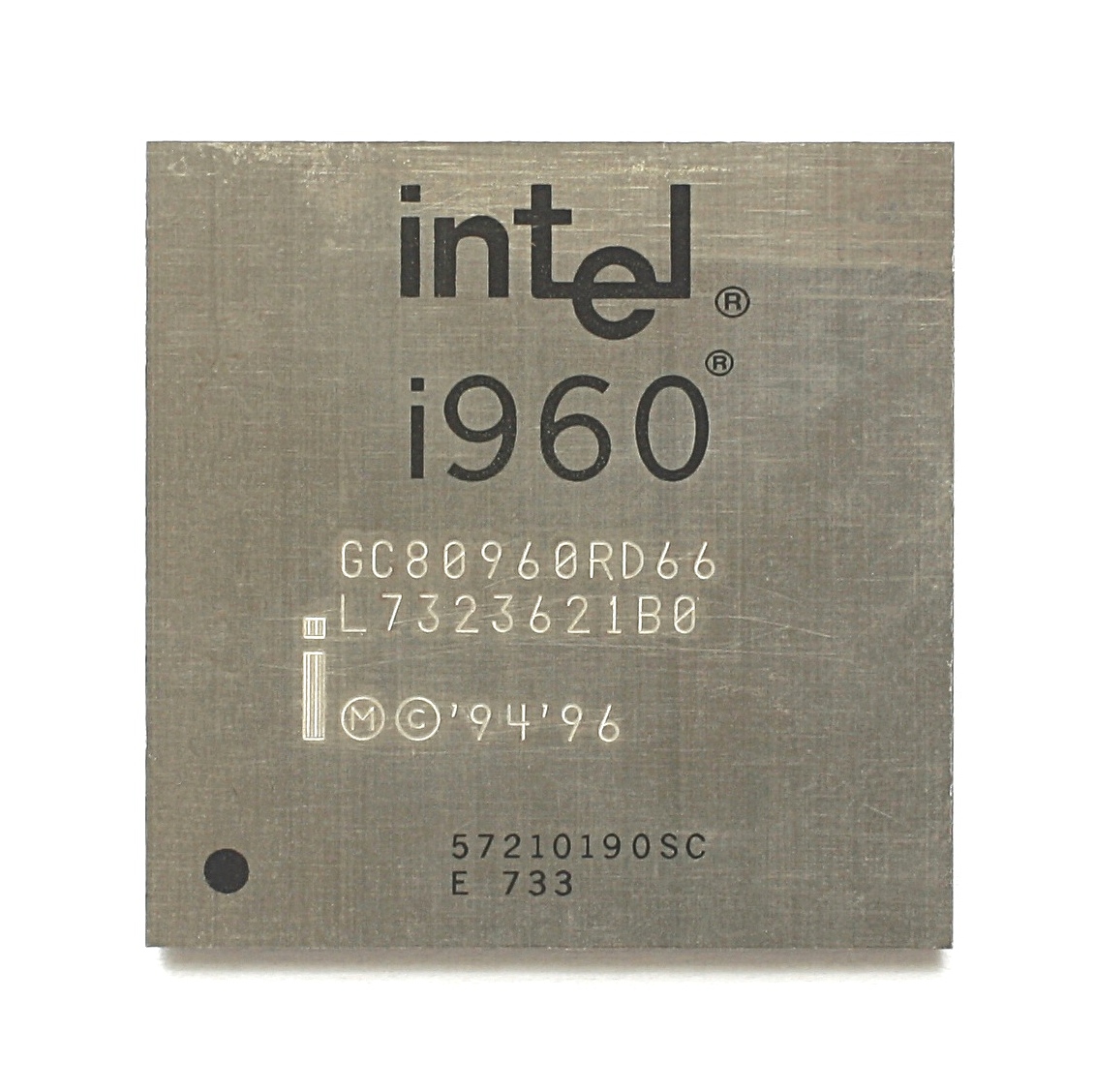

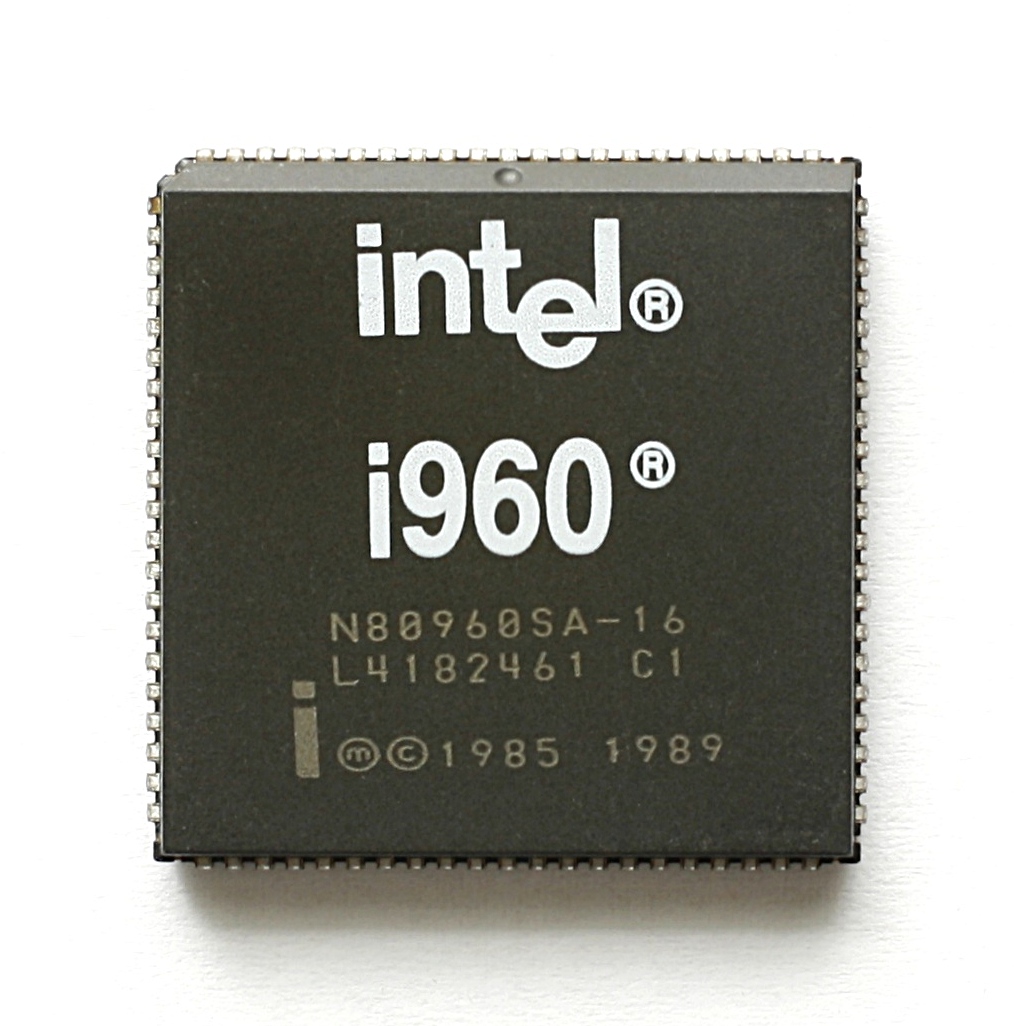

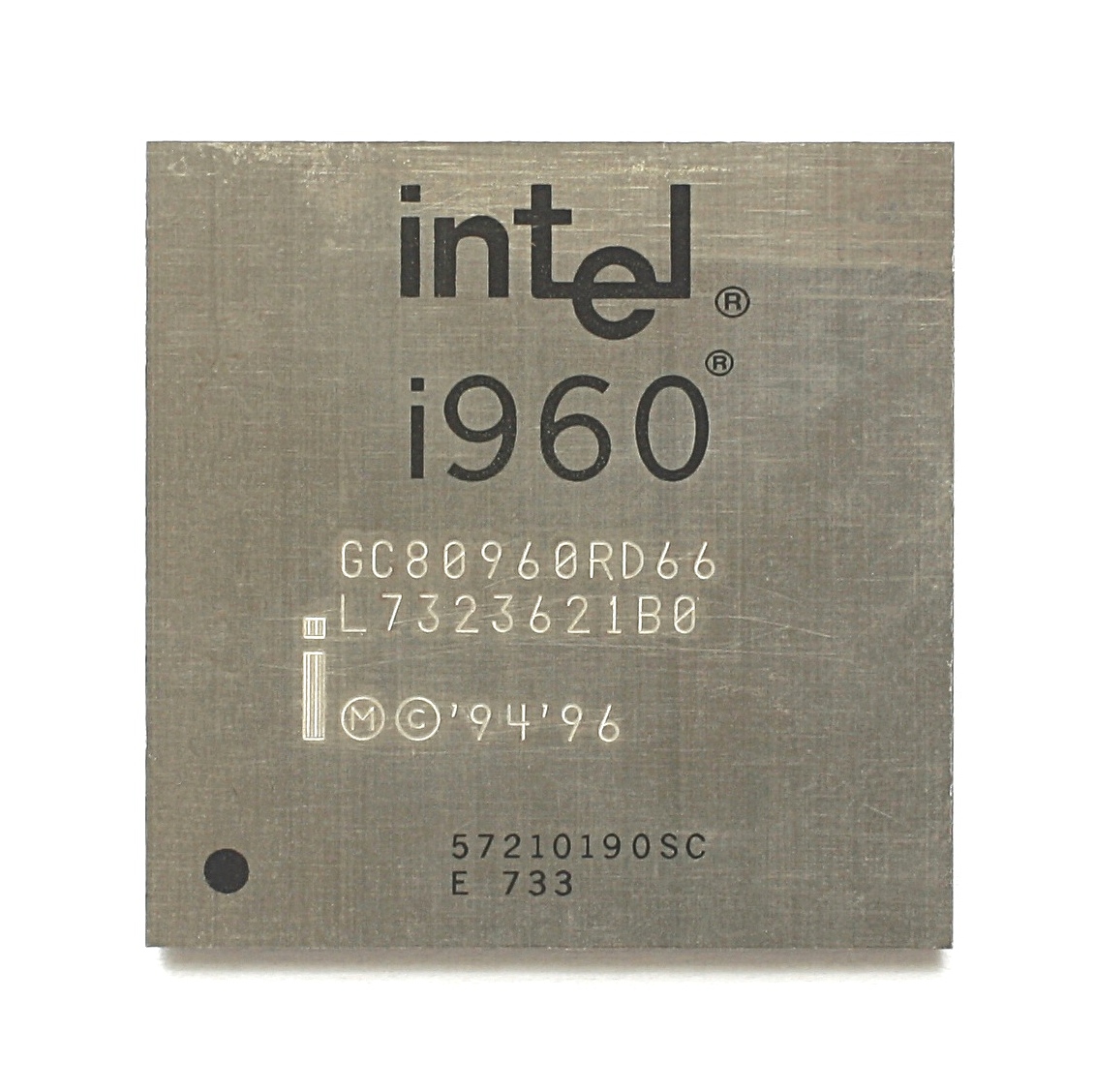

Intel 80960MX die.jpg, Intel 80960MX

Intel 80960KA die.JPG, Intel 80960KA

Intel 80960SA die.JPG, Intel 80960SA

Intel 80960CA die.JPG, Intel 80960CA

Intel A80960CF-25.jpg, Intel 80960CF

Intel 80960JA die.jpg, Intel 80960JA

Intel 80960HD die.JPG, Intel 80960HD

i960 homepage at Intel

i960 images and descriptions at cpu-collection.de

BiiN CPU Architecture Reference Manual (describes i960MX instruction set)

authored by

superscalar

A superscalar processor is a CPU that implements a form of parallelism called instruction-level parallelism within a single processor. In contrast to a scalar processor, which can execute at most one single instruction per clock cycle, a sup ...

ity specialist Fred Pollack Fred Pollack is a retired microprocessor electronics engineer who worked on several Intel chips. He was the lead engineer of the Intel iAPX 432, the lead architect of the Intel i960, and the lead architect of the Pentium Pro.

He specialized in ...

who was also the lead engineer of the Intel iAPX 432

The iAPX 432 (''Intel Advanced Performance Architecture'') is a discontinued computer architecture introduced in 1981. It was Intel's first 32-bit processor design. The main processor of the architecture, the ''general data processor'', is im ...

and the lead architect of the i686 chip, the Pentium Pro

The Pentium Pro is a sixth-generation x86 microprocessor developed and manufactured by Intel and introduced on November 1, 1995. It introduced the P6 microarchitecture (sometimes termed i686) and was originally intended to replace the original ...

.

Architecture

To avoid the performance issues that plagued the i432, the central i960 instruction-set architecture was a RISC design, which was only implemented in full in the i960MX. The memory subsystem was 33-bits wide—to accommodate a 32-bit word and a "tag" bit to implement memory protection in hardware. In many ways, the i960 followed the original Berkeley RISC design, notably in its use ofregister window

In computer engineering, register windows are a feature which dedicates registers to a subroutine by dynamically aliasing a subset of internal registers to fixed, programmer-visible registers. Register windows are implemented to improve the perfo ...

s, an implementation-specific number of caches for the per-subroutine registers that allowed for fast subroutine calls. The competing Stanford University

Stanford University, officially Leland Stanford Junior University, is a private research university in Stanford, California. The campus occupies , among the largest in the United States, and enrolls over 17,000 students. Stanford is conside ...

design, MIPS, did not use this system, instead relying on the compiler to generate optimal subroutine call and return code. In common with most 32-bit designs, the i960 has a flat 32-bit memory space, with no memory segmentation

Memory segmentation is an operating system memory management technique of division of a computer's primary memory into segments or sections. In a computer system using segmentation, a reference to a memory location includes a value that ident ...

, except for the i960MX, which could support up to 226 "objects", each up to 232 bytes in size. The i960 architecture also anticipated a superscalar

A superscalar processor is a CPU that implements a form of parallelism called instruction-level parallelism within a single processor. In contrast to a scalar processor, which can execute at most one single instruction per clock cycle, a sup ...

implementation, with instructions being simultaneously dispatched to more than one unit within the processor.

It contains 32 of 32-bit register, a 512 byte of instruction cache, a stack frame cache, a high speed 32-bit multiplexed burst bus, and an interrupt controller.

i960 variants

80960MX, 80960MC

The "full" i960MX was never released for the non-military market, but the otherwise identical i960MC was used in high-end embedded applications. The i960MC included all of the features of the original BiiN system; but these were simply not mentioned in the specifications, leading some to wonder why the i960MC was so large and had so many pins labeled "no connect".80960KA, 80960KB

A version of the RISC core without memory management or an FPU became the i960KA, and the RISC core with an FPU became the i960KB. The versions were, however, identical internally—only the labeling was different. This meant the CPUs were much larger than necessary for the "actually supported" feature sets, and as a result, more expensive to manufacture than they needed to be. These processors contains more than 350,000 transistors. These processors can perform around 7.5 VAX MIPS. The 80960KB version is compatible withIEEE 754

The IEEE Standard for Floating-Point Arithmetic (IEEE 754) is a technical standard for floating-point arithmetic established in 1985 by the Institute of Electrical and Electronics Engineers (IEEE). The standard addressed many problems found ...

standard and can perform up to 4 MegaWhetstones. Both processors are available in 16 and 20 MHz using CHMOS-III technology. Both processors are packaged in 132-PGA. The 80960KA version is available for USD $230 and the 80960KB version is available for USD $390 in quantities of 100 respectfully.

The i960KA became successful as a low-cost 32-bit processor for the laser-printer market, as well as for early graphics terminals and other embedded applications. Its success paid for future generations, which were without the complex memory sub-system.

80960CA, 80960CF

The i960CA, first announced in July 1989, was the first pure RISC implementation of the i960 architecture. It featured a newly designed superscalar RISC core and added an unusual addressable on-chip cache, but lacked an FPU and MMU, as it was intended for high-performance embedded applications. The i960CA is widely considered to have been the first single-chipsuperscalar

A superscalar processor is a CPU that implements a form of parallelism called instruction-level parallelism within a single processor. In contrast to a scalar processor, which can execute at most one single instruction per clock cycle, a sup ...

RISC implementation. The C-series included only one ALU, but could dispatch and execute an arithmetic instruction, a memory reference, and a branch instruction at the same time, and sustain two instructions per cycle under certain circumstances. The first versions released ran at 33 MHz, and Intel promoted the chip as capable of 66 MIPS. The i960CA microarchitecture was designed in 1987–1988 and formally announced on September 12, 1989.

Later, in May 1992, came the i960CF, which included a larger instruction cache (4 KB instead of 1 KB) and added 1 KB of data cache, but was still without an FPU or MMU.

80960Jx

The 80960Jx is a processor for embedded applications. It features a 32-bit multiplexed address/data bus, instruction and data cache, 1K on-chip RAM, interrupt controller, and two independent 32-bit timers. The 80960Jx’s testability features included ONCE (on-circuit emulation) mode and boundary scan (JTAG

JTAG (named after the Joint Test Action Group which codified it) is an industry standard for verifying designs and testing printed circuit boards after manufacture.

JTAG implements standards for on-chip instrumentation in electronic design aut ...

).

80960HA, 80960HD, 80960HT

The 80960Hx processors offered upgraded performance from the Cx variants by offering clock multiplication, larger 16K instruction cache and 4k data cache, and a GMU. (Guarded Memory Unit). The HD variant had an internal 2x clock multiplication while the HT version has a 3x clock multiplication, allowing increased performance without external bus speed changes.80960VH

Announced in October 1998, the i960VH Embedded-PCI processor featured a 32-bit 33 MHz PCI bus and 100 MHz i960JT processor core. The core also featured 16 KB of instruction cache, 4 KB of data cache, and 1 KB of built-in RAM. Other core features included two 32-bit timers, programmable interrupt controller,I²C

I2C (Inter-Integrated Circuit, ), alternatively known as I2C or IIC, is a synchronous, multi-controller/multi-target (master/slave), packet switched, single-ended, serial communication bus invented in 1982 by Philips Semiconductors. It is wid ...

interface, and a two-channel DMA controller.

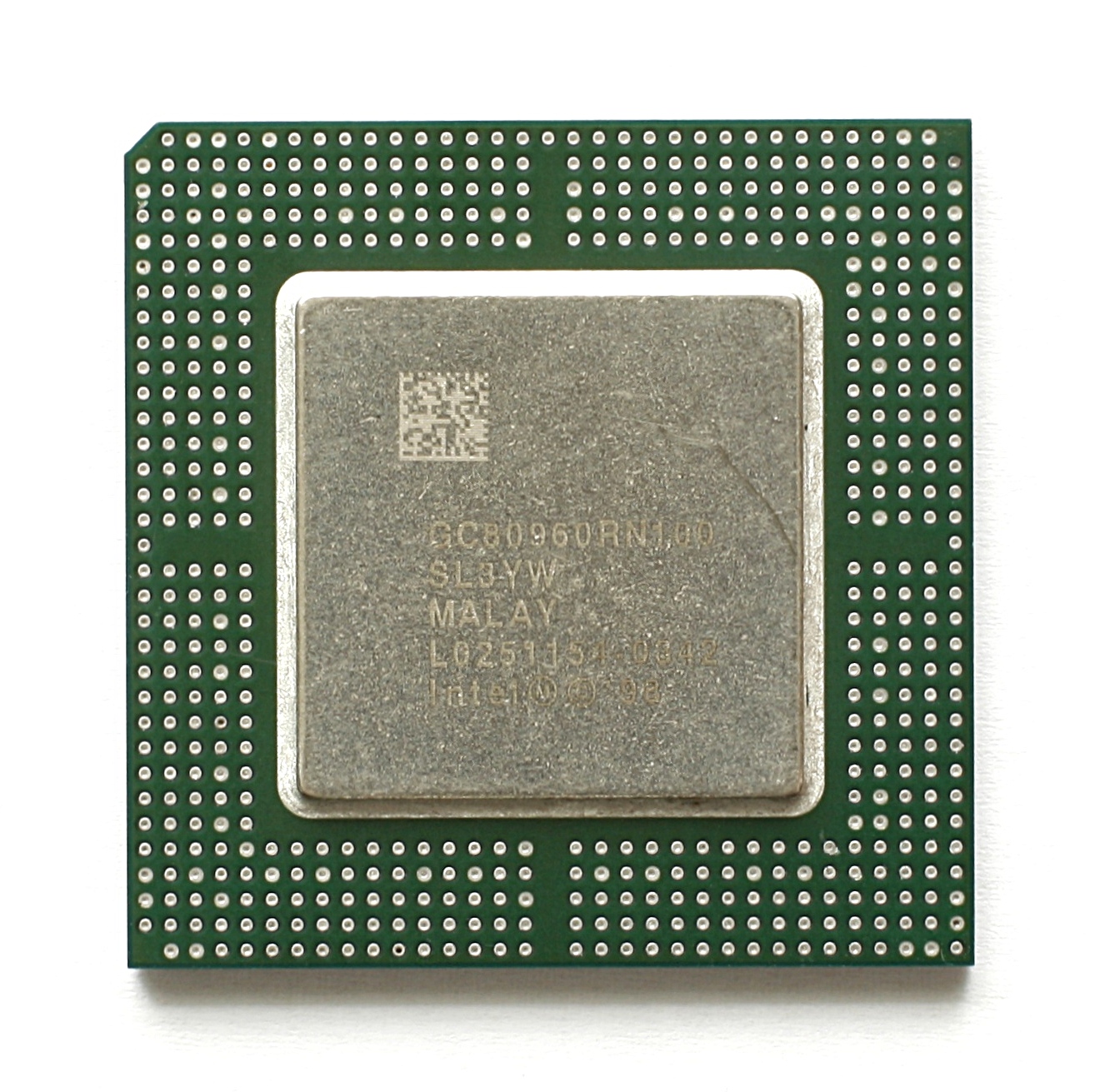

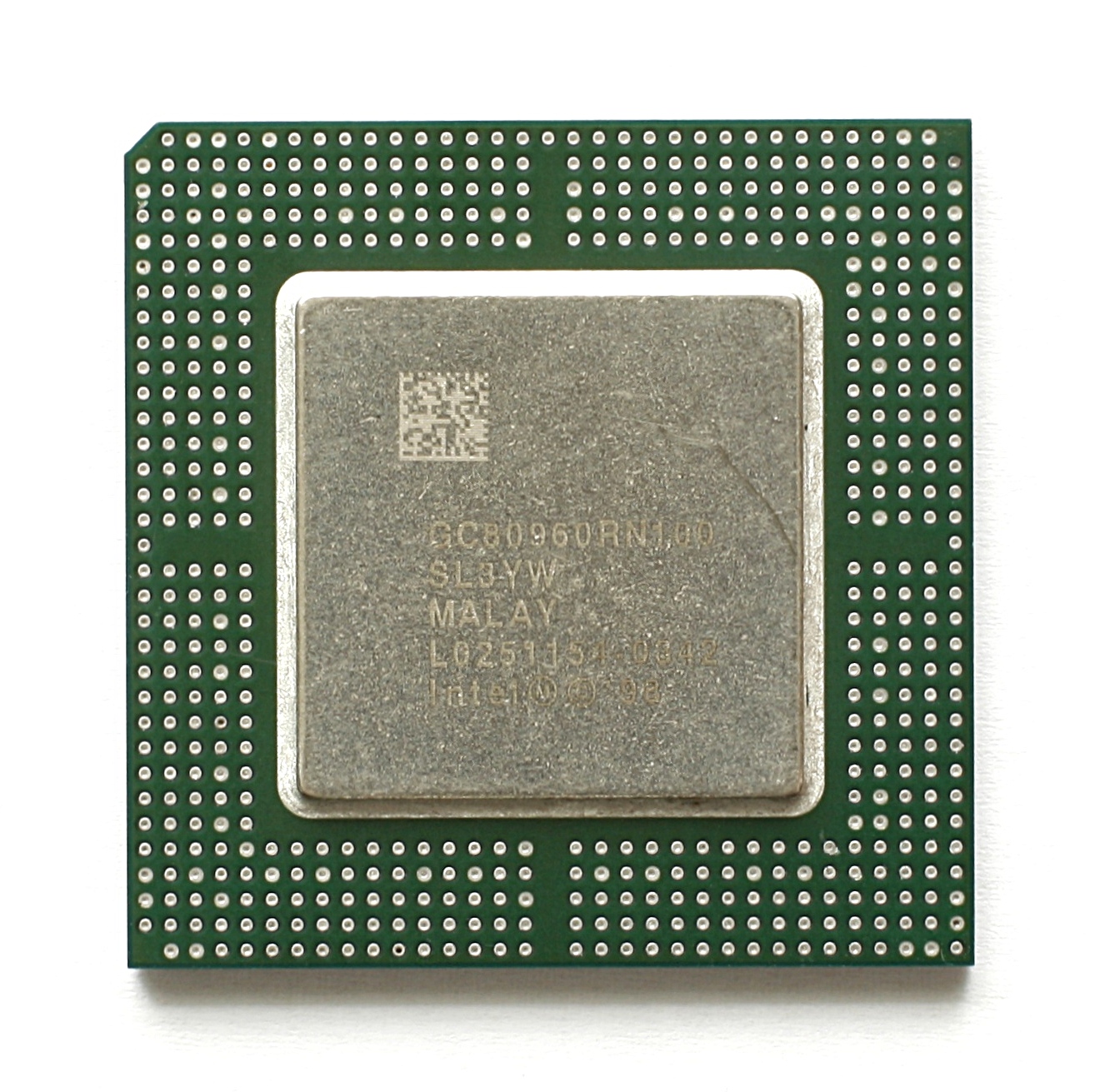

80960Rx

The 80960Rx processors were labeled as I/O Processors and included an implementation of the PCI Bus (2.1 or 2.2 depending on the variant) as well as a 80960Jx core. These could be used on motherboards to implement on-board PCI device as well as on PCI expansion cards. The RM/RN/RS variants used a JT core with a 3x bus to core multiplication to achieve 100 MHz internal clock speeds, while the RD variant used a JF core with 2x multiplication to achieve 66 MHz. The RP variant had a JF core that ran at the 33 MHz bus speed.Variant specifications

End of development

Intel attempted to bolster the i960 in the I/O device controller market with theI2O

Intelligent Input/Output (I2O) is a defunct computer input/output (I/O) specification. I2O was originally designed to make use of the Intel i960 microprocessor as the I/O offload engine, bringing channel I/O to the PC. I2O emerged from Intel in ...

standard, but this had little success and the design work was eventually ended. By the mid-1990s its price/performance ratio had fallen behind competing chips of more recent design, and Intel never produced a reduced-power-consumption version that could be used in battery-powered systems.

In 1990, the i960 team was redirected to be the "second team" working in parallel on future i386

The Intel 386, originally released as 80386 and later renamed i386, is a 32-bit microprocessor introduced in 1985. The first versions had 275,000 transistorsPentium Pro

The Pentium Pro is a sixth-generation x86 microprocessor developed and manufactured by Intel and introduced on November 1, 1995. It introduced the P6 microarchitecture (sometimes termed i686) and was originally intended to replace the original ...

. The i960 project was given to another smaller development team, essentially ensuring the end of its developmental life.

Current status

Because of its high performance in calculatingXOR

Exclusive or or exclusive disjunction is a logical operation that is true if and only if its arguments differ (one is true, the other is false).

It is symbolized by the prefix operator J and by the infix operators XOR ( or ), EOR, EXOR, , ...

values, i960 processors, such as the 80303, are often used in controllers for higher-end, RAID

Raid, RAID or Raids may refer to:

Attack

* Raid (military), a sudden attack behind the enemy's lines without the intention of holding ground

* Corporate raid, a type of hostile takeover in business

* Panty raid, a prankish raid by male college ...

-capable, SCSI

Small Computer System Interface (SCSI, ) is a set of standards for physically connecting and transferring data between computers and peripheral devices. The SCSI standards define commands, protocols, electrical, optical and logical interface ...

-disk-array, host-adapter cards as well as Digital Equipment/Compaq/HP's high-end SCSI and DSSI, and eventually Fibre Channel

Fibre Channel (FC) is a high-speed data transfer protocol providing in-order, lossless delivery of raw block data. Fibre Channel is primarily used to connect computer data storage to servers in storage area networks (SAN) in commercial data cen ...

HSx-series, standalone RAID controllers.

An i960RS chip also powers Adaptec

Adaptec was a computer storage company and remains a brand for computer storage products. The company was an independent firm from 1981 to 2010, at which point it was acquired by PMC-Sierra, which itself was later acquired by Microsemi, which itse ...

's AAR-2400A controller, which uses four commodity parallel ATA

Parallel ATA (PATA), originally , also known as IDE, is a standard interface designed for IBM PC-compatible computers. It was first developed by Western Digital and Compaq in 1986 for compatible hard drives and CD or DVD drives. The connect ...

drives to build an affordable RAID-5

In computer storage, the standard RAID levels comprise a basic set of RAID ("redundant array of independent disks" or "redundant array of inexpensive disks") configurations that employ the techniques of striping, mirroring, or parity to create la ...

protected fault-tolerant storage system for small PC servers and workstations.

The i960 was also used in some Brocade

Brocade is a class of richly decorative shuttle-woven fabrics, often made in colored silks and sometimes with gold and silver threads. The name, related to the same root as the word " broccoli", comes from Italian ''broccato'' meaning "emb ...

Fibre Channel

Fibre Channel (FC) is a high-speed data transfer protocol providing in-order, lossless delivery of raw block data. Fibre Channel is primarily used to connect computer data storage to servers in storage area networks (SAN) in commercial data cen ...

switches to run Fabric OS In storage area networking, Fabric OS is the firmware for Brocade Communications Systems's Fibre Channel switches and Fibre Channel directors. It is also known as FOS.

First generation

The first generation of Fabric OS was developed on top of a VxW ...

.

The i960 architecture is also used in slot machine

A slot machine (American English), fruit machine (British English) or poker machine (Australian English and New Zealand English) is a gambling machine that creates a game of chance for its customers. Slot machines are also known pejoratively a ...

s. Currently, they are found in IGT's Stepper S2000 family and i960 video family. It was also used as the main CPU of Sega

is a Japanese multinational video game and entertainment company headquartered in Shinagawa, Tokyo. Its international branches, Sega of America and Sega Europe, are headquartered in Irvine, California and London, respectively. Its division ...

's famous Model 2 series of arcade boards.

The Indian Air Force

The Indian Air Force (IAF) is the air force, air arm of the Indian Armed Forces. Its complement of personnel and aircraft assets ranks third amongst the air forces of the world. Its primary mission is to secure Indian airspace and to conduct ...

's HAL Tejas

The HAL Tejas is an Indian, single engine, delta wing, light multirole fighter designed by the Aeronautical Development Agency (ADA) in collaboration with Aircraft Research and Design Centre (ARDC) of Hindustan Aeronautics Limited (HAL) for ...

light combat aircraft's MMR (multi-mode radar) is said to use the i960. The HAL Tejas was introduced into service in 2015.

The Indian Space Research Organisation

The Indian Space Research Organisation (ISRO; ) is the national space agency of India, headquartered in Bengaluru. It operates under the Department of Space (DOS) which is directly overseen by the Prime Minister of India, while the Chairman o ...

(ISRO) is said to use the chip in its on-board computers in its launch vehicles.

The i960 processor is also used in Automatic Radar Plotting Aid (ARPA) interfacing boards in radar

Radar is a detection system that uses radio waves to determine the distance (''ranging''), angle, and radial velocity of objects relative to the site. It can be used to detect aircraft, Marine radar, ships, spacecraft, guided missiles, motor v ...

s from Kelvin Hughes

Hensoldt UK, formerly Kelvin Hughes, is a British company specialising in the design and manufacture of navigation and surveillance systems and a supplier of navigational data to both the commercial marine and government marketplace.

The company ...

.

The chip was used on some HP X-Terminals.

Some SATA

SATA (Serial AT Attachment) is a computer bus interface that connects host bus adapters to mass storage devices such as hard disk drives, optical drives, and solid-state drives. Serial ATA succeeded the earlier Parallel ATA (PATA) standard t ...

RAID

Raid, RAID or Raids may refer to:

Attack

* Raid (military), a sudden attack behind the enemy's lines without the intention of holding ground

* Corporate raid, a type of hostile takeover in business

* Panty raid, a prankish raid by male college ...

controllers use Intel's 80303 IOP (Intelligent I/O Processor), which integrates a PCI-to-PCI bridge, memory controller, and a 80960JT-100 CPU core.

The chip was used on the Alcatel-Lucent

Alcatel–Lucent S.A. () was a French–American global telecommunications equipment company, headquartered in Boulogne-Billancourt, France. It was formed in 2006 by the merger of France-based Alcatel and U.S.-based Lucent, the latter being a su ...

1000 ADSL

Asymmetric digital subscriber line (ADSL) is a type of digital subscriber line (DSL) technology, a data communications technology that enables faster data transmission over copper telephone lines than a conventional voiceband modem can provide. ...

broadband

In telecommunications, broadband is wide bandwidth data transmission which transports multiple signals at a wide range of frequencies and Internet traffic types, that enables messages to be sent simultaneously, used in fast internet connections. ...

modem

References

External links

i960 homepage at Intel

i960 images and descriptions at cpu-collection.de

BiiN CPU Architecture Reference Manual (describes i960MX instruction set)

authored by

Randal L. Schwartz

Randal L. Schwartz (born November 22, 1961), also known as merlyn, is an American author, system administrator and programming consultant. He has written several books on the Perl programming language, and plays a promotional role within the Per ...

{{DEFAULTSORT:Intel I960

Intel microcontrollers

I960

Superscalar microprocessors

32-bit microprocessors