|

Little-endian

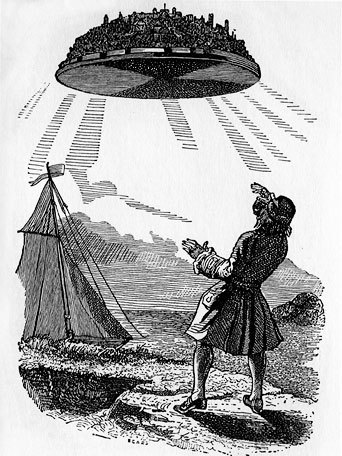

'' Jonathan_Swift.html" ;"title="Gulliver's Travels'' by Jonathan Swift">Gulliver's Travels'' by Jonathan Swift, the novel from which the term was coined In computing, endianness is the order in which bytes within a word (data type), word of digital data are transmitted over a data communication medium or Memory_address, addressed (by rising addresses) in computer memory, counting only byte significance compared to earliness. Endianness is primarily expressed as big-endian (BE) or little-endian (LE), terms introduced by Danny Cohen into computer science for data ordering in an Internet Experiment Note published in 1980. Also published at The adjective ''endian'' has its origin in the writings of 18th century Anglo-Irish writer Jonathan Swift. In the 1726 novel ''Gulliver's Travels'', he portrays the conflict between sects of Lilliputians divided into those breaking the shell of a boiled egg from the big end or from the little end. By analogy, a CPU may read a digital word b ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Gulliver's Travels

''Gulliver's Travels'', originally titled ''Travels into Several Remote Nations of the World. In Four Parts. By Lemuel Gulliver, First a Surgeon, and then a Captain of Several Ships'', is a 1726 prose satire by the Anglo-Irish writer and clergyman Jonathan Swift, satirising human nature and the imaginary "Imaginary voyage, travellers' tales" literary subgenre. It is Swift's best-known full-length work, one of the most famous classics of English literature, and popularised the fictional island of Lilliput and Blefuscu, Lilliput. The English poet and dramatist John Gay remarked, "It is universally read, from the cabinet council to the nursery." The book has been adapted for over a dozen films, movies, plays, and theatrical performances over the centuries. The book was an immediate success, and Swift claimed that he wrote ''Gulliver's Travels'' "to vex the world rather than divert it". Plot Part I: A Voyage to Lilliput The travel begins with a short preamble in which Lemuel Gu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Memory Address

In computing, a memory address is a reference to a specific memory location in memory used by both software and hardware. These addresses are fixed-length sequences of digits, typically displayed and handled as unsigned integers. This numerical representation is based on the features of CPU (such as the instruction pointer and incremental address registers). Programming language constructs often treat the memory like an array. Types Physical addresses A digital computer's main memory consists of many memory locations, each identified by a unique physical address (a specific code). The CPU or other devices can use these codes to access the corresponding memory locations. Generally, only system software (such as the BIOS, operating systems, and specialized utility programs like memory testers) directly addresses physical memory using machine code instructions or processor registers. These instructions tell the CPU to interact with a hardware component called the memory c ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Field (computer Science)

In data hierarchy, a field (data field) is a Variable (computer science), variable in a record (computer science), record. A record, also known as a data structure, allows logically related data to be identified by a single name. Identifying related data as a single group is central to the construction of understandable computer programs. The individual fields in a record may be accessed by name, just like any variable in a computer program. Each field in a record has two components. One component is the field's data type, datatype Declaration (computer programming), declaration. The other component is the field's identifier. Memory fields Fields may be stored in random access memory (RAM). The following Pascal (programming language), Pascal record definition has three field identifiers: firstName, lastName, and age. The two name fields have a datatype of an Array (data structure), array of Character (computing), character. The age field has a datatype of integer. type PersonRec ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Byte Addressing

Byte addressing in hardware architectures supports accessing individual bytes. Computers with byte addressing are sometimes called byte machines, in contrast to '' word-addressable'' architectures, ''word machines'', that access data by word. Background The basic unit of digital storage is a bit, storing a single 0 or 1. Many common instruction set architectures can address more than 8 bits of data at a time. For example, 32-bit x86 processors have 32-bit general-purpose registers and can handle 32-bit (4-byte) data in single instructions. However, data in memory may be of various lengths. Instruction sets that support byte addressing supports accessing data in units that are narrower than the word length. An eight-bit processor like the Intel 8008 addresses eight bits, but as this is the full width of the accumulator and other registers, this could be considered either byte-addressable or word-addressable. 32-bit x86 processors, which address memory in 8-bit units but have 3 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Address Space

In computing, an address space defines a range of discrete addresses, each of which may correspond to a network host, peripheral device, disk sector, a memory cell or other logical or physical entity. For software programs to save and retrieve stored data, each datum must have an address where it can be located. The number of address spaces available depends on the underlying address structure, which is usually limited by the computer architecture being used. Often an address space in a system with virtual memory corresponds to a highest level translation table, e.g., a segment table in IBM System/370. Address spaces are created by combining enough uniquely identified qualifiers to make an address unambiguous within the address space. For a person's physical address, the ''address space'' would be a combination of locations, such as a neighborhood, town, city, or country. Some elements of a data address space may be the same, but if any element in the address is different, ad ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Computer Memory

Computer memory stores information, such as data and programs, for immediate use in the computer. The term ''memory'' is often synonymous with the terms ''RAM,'' ''main memory,'' or ''primary storage.'' Archaic synonyms for main memory include ''core'' (for magnetic core memory) and ''store''. Main memory operates at a high speed compared to mass storage which is slower but less expensive per bit and higher in capacity. Besides storing opened programs and data being actively processed, computer memory serves as a Page cache, mass storage cache and write buffer to improve both reading and writing performance. Operating systems borrow RAM capacity for caching so long as it is not needed by running software. If needed, contents of the computer memory can be transferred to storage; a common way of doing this is through a memory management technique called ''virtual memory''. Modern computer memory is implemented as semiconductor memory, where data is stored within memory cell (com ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

32bit-Endianess

3 (three) is a number, numeral and digit. It is the natural number following 2 and preceding 4, and is the smallest odd prime number and the only prime preceding a square number. It has religious and cultural significance in many societies. Evolution of the Arabic digit The use of three lines to denote the number 3 occurred in many writing systems, including some (like Roman and Chinese numerals) that are still in use. That was also the original representation of 3 in the Brahmic (Indian) numerical notation, its earliest forms aligned vertically. However, during the Gupta Empire the sign was modified by the addition of a curve on each line. The Nāgarī script rotated the lines clockwise, so they appeared horizontally, and ended each line with a short downward stroke on the right. In cursive script, the three strokes were eventually connected to form a glyph resembling a with an additional stroke at the bottom: ३. The Indian digits spread to the Caliphate in the 9th ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

File Format

A file format is a Computer standard, standard way that information is encoded for storage in a computer file. It specifies how bits are used to encode information in a digital storage medium. File formats may be either proprietary format, proprietary or open format, open. Some file formats are designed for very particular types of data: Portable Network Graphics, PNG files, for example, store Raster graphics, bitmapped Graphics file format, images using lossless data compression. Other file formats, however, are designed for storage of several different types of data: the Ogg format can act as a container format (digital), container for different types of multimedia including any combination of sound, audio and video, with or without text (such as subtitles), and metadata. A text file can contain any stream of characters, including possible control characters, and is encoded in one of various Character encoding, character encoding schemes. Some file formats, such as HTML, sca ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

RISC-V

RISC-V (pronounced "risk-five") is an open standard instruction set architecture (ISA) based on established reduced instruction set computer (RISC) principles. The project commenced in 2010 at the University of California, Berkeley. It transferred to the RISC-V Foundation in 2015, and from there to RISC-V International, a Swiss non-profit entity, in November 2019. Similar to several other RISC ISAs, e.g. Amber (processor), Amber (ARMv2)(2001), SuperH#J_Core, J-Core(2015), OpenRISC(2000), or OpenSPARC(2005), RISC-V is offered under royalty-free open-source licenses. The documents defining the RISC-V instruction set architecture (ISA) are offered under a Creative Commons license or a BSD licenses, BSD License. Mainline support for RISC-V was added to the Linux 5.17 kernel in 2022, along with its toolchain. In July 2023, RISC-V, in its 64-bit computing, 64-bit variant called riscv64, was included as an official architecture of Linux distribution Debian, in its Debian version histor ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

ARM Architecture

ARM (stylised in lowercase as arm, formerly an acronym for Advanced RISC Machines and originally Acorn RISC Machine) is a family of reduced instruction set computer, RISC instruction set architectures (ISAs) for central processing unit, computer processors. Arm Holdings develops the ISAs and licenses them to other companies, who build the physical devices that use the instruction set. It also designs and licenses semiconductor intellectual property core, cores that implement these ISAs. Due to their low costs, low power consumption, and low heat generation, ARM processors are useful for light, portable, battery-powered devices, including smartphones, laptops, and tablet computers, as well as embedded systems. However, ARM processors are also used for desktop computer, desktops and server (computing), servers, including Fugaku (supercomputer), Fugaku, the world's fastest supercomputer from 2020 to 2022. With over 230 billion ARM chips produced, , ARM is the most widely used ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |

Internet Protocol Suite

The Internet protocol suite, commonly known as TCP/IP, is a framework for organizing the communication protocols used in the Internet and similar computer networks according to functional criteria. The foundational protocols in the suite are the Transmission Control Protocol (TCP), the User Datagram Protocol (UDP), and the Internet Protocol (IP). Early versions of this networking model were known as the Department of Defense (DoD) model because the research and development were funded by the United States Department of Defense through DARPA. The Internet protocol suite provides end-to-end data communication specifying how data should be packetized, addressed, transmitted, routed, and received. This functionality is organized into four abstraction layers, which classify all related protocols according to each protocol's scope of networking. An implementation of the layers for a particular application forms a protocol stack. From lowest to highest, the layers are the l ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] [Amazon] |