Charge trap flash (CTF) is a

semiconductor memory

Semiconductor memory is a digital electronic semiconductor device used for digital data storage, such as computer memory. It typically refers to devices in which data is stored within metal–oxide–semiconductor (MOS) memory cells on a si ...

technology used in creating

non-volatile

Non-volatile memory (NVM) or non-volatile storage is a type of computer memory that can retain stored information even after power is removed. In contrast, volatile memory needs constant power in order to retain data.

Non-volatile memory typ ...

NOR and NAND

flash memory

Flash memory is an Integrated circuit, electronic Non-volatile memory, non-volatile computer memory storage medium that can be electrically erased and reprogrammed. The two main types of flash memory, NOR flash and NAND flash, are named for t ...

. It is a type of

floating-gate MOSFET

The floating-gate MOSFET (FGMOS), also known as a floating-gate MOS transistor or floating-gate transistor, is a type of metal–oxide–semiconductor field-effect transistor (MOSFET) where the gate is electrically isolated, creating a floating no ...

memory technology, but differs from the conventional floating-gate technology in that it uses a

silicon nitride

Silicon nitride is a chemical compound of the elements silicon and nitrogen. (''Trisilicon tetranitride'') is the most thermodynamically stable and commercially important of the silicon nitrides, and the term ″''Silicon nitride''″ commonly re ...

film to store electrons rather than the doped

polycrystalline silicon

Polycrystalline silicon, or multicrystalline silicon, also called polysilicon, poly-Si, or mc-Si, is a high purity, polycrystalline form of silicon, used as a raw material by the solar photovoltaic and electronics industry.

Polysilicon is produc ...

typical of a floating-gate structure. This approach allows memory manufacturers to reduce manufacturing costs five ways:

# Fewer process steps are required to form a charge storage node

# Smaller process geometries can be used (therefore reducing chip size and cost)

# Multiple bits can be stored on a single flash memory cell

# Improved reliability

# Higher yield since the charge trap is less susceptible to point defects in the tunnel oxide layer

While the charge-trapping concept was around earlier, it wasn't until 2002 that

AMD

Advanced Micro Devices, Inc. (AMD) is an American multinational corporation and technology company headquartered in Santa Clara, California and maintains significant operations in Austin, Texas. AMD is a hardware and fabless company that de ...

and

Fujitsu produced high-volume charge-trapping flash memory. They began the commercial production of charge-trapping flash memory with the introduction of the GL NOR flash memory family. The same business, now operating under the

Spansion

Spansion Inc. was an American-based company that designed, developed, and manufactured flash memory, microcontrollers, mixed-signal and analog products, and system-on-chip (SoC) solutions.Reuters.Spansion Inc." July 26, 2010.By Mark LaPedus, EE ...

name, has produced charge trapping devices in high volume since that time. Charge trapping flash accounted for 30% of 2008's $2.5 billion NOR flash market.

Saifun Semiconductors, who licensed a large charge trapping technology portfolio to several companies, was acquired by Spansion in March 2008. From the late 2000s, CTF became a core component of 3D

V-NAND flash memory developed by

Toshiba

is a Japanese multinational electronics company headquartered in Minato, Tokyo. Its diversified products and services include power, industrial and social infrastructure systems, elevators and escalators, electronic components, semiconductors ...

and

Samsung Electronics

Samsung Electronics Co., Ltd. (SEC; stylized as SΛMSUNG; ) is a South Korean multinational major appliance and consumer electronics corporation founded on 13 January 1969 and headquartered in Yeongtong District, Suwon, South Korea. It is curr ...

.

Origins

In 1957, Frosch and Derick were able to manufacture the first silicon dioxide field effect transistors at Bell Labs, the first transistors in which drain and source were adjacent at the surface. Subsequently,

Dawon Kahng

Dawon Kahng (; May 4, 1931 – May 13, 1992) was a Korean-American electrical engineer and inventor, known for his work in solid-state electronics. He is best known for inventing the MOSFET (metal–oxide–semiconductor field-effect transisto ...

led a paper demonstrating a working

MOSFET

upright=1.3, Two power MOSFETs in amperes">A in the ''on'' state, dissipating up to about 100 watt">W and controlling a load of over 2000 W. A matchstick is pictured for scale.

In electronics, the metal–oxide–semiconductor field- ...

with their Bell Labs team in 1960. The team included E. E. LaBate and E. I. Povilonis who fabricated the device; M. O. Thurston, L. A. D’Asaro, and J. R. Ligenza who developed the diffusion processes, and H. K. Gummel and R. Lindner who characterized the device.

Later, Kahng went on to invent the

floating-gate MOSFET

The floating-gate MOSFET (FGMOS), also known as a floating-gate MOS transistor or floating-gate transistor, is a type of metal–oxide–semiconductor field-effect transistor (MOSFET) where the gate is electrically isolated, creating a floating no ...

with

Simon Min Sze

Simon Min Sze, or Shi Min (; 21 March 1936 – 6 November 2023), was a Taiwanese-American electrical engineer. He is best known for inventing the floating-gate MOSFET with Korean electrical engineer Dawon Kahng in 1967.

Early life and educat ...

at Bell Labs, and they proposed its use as a

floating-gate

The floating-gate MOSFET (FGMOS), also known as a floating-gate MOS transistor or floating-gate transistor, is a type of metal–oxide–semiconductor field-effect transistor (MOSFET) where the gate is electrically isolated, creating a floating no ...

(FG)

memory cell, in 1967. This was the first form of

non-volatile memory

Non-volatile memory (NVM) or non-volatile storage is a type of computer memory that can retain stored information even after power is removed. In contrast, volatile memory needs constant power in order to retain data.

Non-volatile memory typ ...

based on the injection and storage of charges in a floating-gate MOSFET,

which later became the basis for

EPROM

An EPROM (rarely EROM), or erasable programmable read-only memory, is a type of programmable read-only memory (PROM) integrated circuit, chip that retains its data when its power supply is switched off. Computer memory that can retrieve stored d ...

(erasable

PROM

A promenade dance or prom is a formal dance party for graduating high school students at the end of the school year.

Students participating in the prom will typically vote for a ''prom king'' and ''prom queen''. Other students may be honored ...

),

EEPROM

EEPROM or E2PROM (electrically erasable programmable read-only memory) is a type of non-volatile memory. It is used in computers, usually integrated in microcontrollers such as smart cards and remote keyless systems, or as a separate chip d ...

(electrically erasable PROM) and

flash memory

Flash memory is an Integrated circuit, electronic Non-volatile memory, non-volatile computer memory storage medium that can be electrically erased and reprogrammed. The two main types of flash memory, NOR flash and NAND flash, are named for t ...

technologies.

The charge-trapping concept was first presented by John Szedon and Ting L. Chu in 1967.

In late 1967, a

Sperry Sperry may refer to:

Places

In the United States:

* Sperry, Iowa, community in Des Moines County

* Sperry, Missouri

*Sperry, Oklahoma, town in Tulsa County

* Sperry Chalet, historic backcountry chalet, Glacier National Park, Montana

* Sperry Glaci ...

research team led by H.A. Richard Wegener invented the

metal–nitride–oxide–semiconductor transistor (MNOS transistor), a type of MOSFET in which the

oxide

An oxide () is a chemical compound containing at least one oxygen atom and one other element in its chemical formula. "Oxide" itself is the dianion (anion bearing a net charge of −2) of oxygen, an O2− ion with oxygen in the oxidation st ...

layer is replaced by a double layer of

nitride

In chemistry, a nitride is a chemical compound of nitrogen. Nitrides can be inorganic or organic, ionic or covalent. The nitride anion, N3−, is very elusive but compounds of nitride are numerous, although rarely naturally occurring. Some nitr ...

and oxide.

Nitride

In chemistry, a nitride is a chemical compound of nitrogen. Nitrides can be inorganic or organic, ionic or covalent. The nitride anion, N3−, is very elusive but compounds of nitride are numerous, although rarely naturally occurring. Some nitr ...

was used as a trapping layer instead of a floating gate, but its use was limited as it was considered inferior to a floating gate. The MNOS transistor device could be programmed through the application of a 50-volt forward or reverse bias between the gate and the channel to trap charges that would impact the threshold voltage of the transistor.

Charge trap (CT) memory was introduced with MNOS devices in the late 1960s. It had a device structure and operating principles similar to floating-gate (FG) memory, but the main difference is that the charges are stored in a conducting material (typically a doped

polysilicon

Polycrystalline silicon, or multicrystalline silicon, also called polysilicon, poly-Si, or mc-Si, is a high purity, polycrystalline form of silicon, used as a raw material by the solar photovoltaic and electronics industry.

Polysilicon is produ ...

layer) in FG memory, whereas CT memory stored charges in localized traps within a

dielectric

In electromagnetism, a dielectric (or dielectric medium) is an Insulator (electricity), electrical insulator that can be Polarisability, polarised by an applied electric field. When a dielectric material is placed in an electric field, electric ...

layer (typically made of

silicon nitride

Silicon nitride is a chemical compound of the elements silicon and nitrogen. (''Trisilicon tetranitride'') is the most thermodynamically stable and commercially important of the silicon nitrides, and the term ″''Silicon nitride''″ commonly re ...

).

Charge trap EEPROM

By 1974, charge trap technology was used as a storage mechanism in

electrically erasable programmable read-only memory

EEPROM or E2PROM (electrically erasable programmable read-only memory) is a type of non-volatile memory. It is used in computers, usually integrated in microcontrollers such as smart cards and remote keyless systems, or as a separate chip d ...

(EEPROM), and was an alternative to the standard

floating-gate MOSFET

The floating-gate MOSFET (FGMOS), also known as a floating-gate MOS transistor or floating-gate transistor, is a type of metal–oxide–semiconductor field-effect transistor (MOSFET) where the gate is electrically isolated, creating a floating no ...

technology. In 1977, P.C.Y. Chen of

Fairchild Camera and Instrument published a paper detailing the invention of

SONOS

Sonos, Inc. is an American audio equipment manufacturer headquartered in Santa Barbara, California. The company was founded in 2002 by John MacFarlane, Craig Shelburne, Tom Cullen, and Trung Mai.

Sonos has partnered with over 100 companies th ...

, a

MOSFET

upright=1.3, Two power MOSFETs in amperes">A in the ''on'' state, dissipating up to about 100 watt">W and controlling a load of over 2000 W. A matchstick is pictured for scale.

In electronics, the metal–oxide–semiconductor field- ...

technology with far less demanding program and erase conditions and longer charge storage. This improvement led to manufacturable EEPROM devices based on charge-trapping SONOS in the 1980s.

Charge trap flash experiments

In 1991, Japanese

NEC

is a Japanese multinational information technology and electronics corporation, headquartered at the NEC Supertower in Minato, Tokyo, Japan. It provides IT and network solutions, including cloud computing, artificial intelligence (AI), Inte ...

researchers including N. Kodama, K. Oyama and Hiroki Shirai developed a type of

flash memory

Flash memory is an Integrated circuit, electronic Non-volatile memory, non-volatile computer memory storage medium that can be electrically erased and reprogrammed. The two main types of flash memory, NOR flash and NAND flash, are named for t ...

that incorporated a charge trap method. In 1998, Israeli engineer Boaz Eitan of

Saifun Semiconductors (later acquired by

Spansion

Spansion Inc. was an American-based company that designed, developed, and manufactured flash memory, microcontrollers, mixed-signal and analog products, and system-on-chip (SoC) solutions.Reuters.Spansion Inc." July 26, 2010.By Mark LaPedus, EE ...

)

patented

A patent is a type of intellectual property that gives its owner the legal right to exclude others from making, using, or selling an invention for a limited period of time in exchange for publishing an enabling disclosure of the invention."A ...

a flash memory technology named

NROM that took advantage of a charge trapping layer to replace the

floating gate used in conventional flash memory designs. Two important innovations appear in this patent: the localization of the injected negative and positive charges close to the cell's drain/source terminals, and utilizing a reverse read concept to detect the cell's stored data on either end of the charge trap. These two new ideas enabled high cycling thus allowing reliable charge trap flash products to be produced for the first time since the charge trapping concept was invented 30 years earlier. Furthermore, using these concepts it is possible to create two separate physical bits per cell, doubling the capacity of stored data per cell.

In 2000, an

Advanced Micro Devices

Advanced Micro Devices, Inc. (AMD) is an American multinational corporation and technology company headquartered in Santa Clara, California and maintains significant operations in Austin, Texas. AMD is a Information technology, hardware and F ...

(AMD) research team led by Richard M. Fastow, Egyptian engineer Khaled Z. Ahmed and Jordanian engineer Sameer Haddad (who later joined Spansion) demonstrated a charge trap mechanism for

NOR flash

Flash memory is an electronic non-volatile computer memory storage medium that can be electrically erased and reprogrammed. The two main types of flash memory, NOR flash and NAND flash, are named for the NOR and NAND logic gates. Both use ...

memory cells. These innovations were further improved at AMD and

Fujitsu in 2002 (and later by Spansion), and first put into volume production by these companies in what was called “MirrorBit Flash memory.”

Spansion MirrorBit Flash memory

Charge trapping flash (CTF) was commercialized by

AMD

Advanced Micro Devices, Inc. (AMD) is an American multinational corporation and technology company headquartered in Santa Clara, California and maintains significant operations in Austin, Texas. AMD is a hardware and fabless company that de ...

and

Fujitsu in 2002. That year, AMD (in a division later spun off as Spansion) announced a new flash memory technology it called "MirrorBit". Spansion used this product to reduce manufacturing costs and extend the density range of NOR Flash memory past that of conventional NOR flash and to match the cost of the

multi-level cell

In electronics, a multi-level cell (MLC) is a memory cell (computing), memory cell capable of storing more than a single bit of information, compared to a single-level cell (SLC), which can store only one bit per memory cell. A memory cell typical ...

NOR flash being manufactured by

Intel

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California, and Delaware General Corporation Law, incorporated in Delaware. Intel designs, manufactures, and sells computer compo ...

.

The MirrorBit cell uses a charge trapping layer not only as a substitute for a conventional floating gate, but it also takes advantage of the non-conducting nature of the charge storage nitride to allow two bits to share the same memory cell. Shown in Figure 1 the bits reside at opposite ends of the cell and can be read by running a current through the channel in different directions.

Products have been successfully made to combine this approach with multilevel cell technology to contain four bits on a cell.

Charge trapping operation

Like the floating gate memory cell, a charge trapping cell uses a variable charge between the control gate and the channel to change the threshold voltage of the transistor. The mechanisms to modify this charge are relatively similar between the floating gate and the charge trap, and the read mechanisms are also very similar.

Charge trapping vs floating gate mechanisms

In a charge trapping flash, electrons are stored in a trapping layer just as they are stored in the floating gate in a standard flash memory, EEPROM, or

EPROM

An EPROM (rarely EROM), or erasable programmable read-only memory, is a type of programmable read-only memory (PROM) integrated circuit, chip that retains its data when its power supply is switched off. Computer memory that can retrieve stored d ...

. The key difference is that the charge trapping layer is an insulator, while the floating gate is a conductor.

High write loads in a flash memory cause stress on the tunnel oxide layer creating small disruptions in the crystal lattice called "oxide defects". If a large number of such disruptions are created a short circuit develops between the floating gate and the transistor's channel and the floating gate can no longer hold a charge. This is the root cause of flash wear-out (see

Flash memory#Memory wear), which is specified as the chip's “endurance.” In order to reduce the occurrence of such short circuits, floating gate flash is manufactured using a thick tunnel oxide (~100Å), but this slows erase when

Fowler-Nordheim tunneling

Field electron emission, also known as field-induced electron emission, field emission (FE) and electron field emission, is the emission of electrons from a material placed in an electrostatic field. The most common context is field emission from ...

is used and forces the design to use a higher tunneling voltage, which puts new burdens on other parts of the chip.

A charge trapping cell is relatively immune to such difficulties, since the charge trapping layer is an insulator.

A short circuit created by an oxide defect between the charge trapping layer and the channel will drain off only the electrons in immediate contact with the short, leaving the other electrons in place to continue to control the threshold voltage of the transistor. Since short circuits are less of a concern, a thinner tunnel oxide layer can be used (50-70Å) increasing the trapping layer's coupling to the channel and leading to a faster program speed (with localized trapped charges) and erasing with lower tunneling voltages. The lower tunneling voltages, in turn, place less stress on the tunnel oxide layer, leading to fewer lattice disruptions.

Another important benefit of using a charge trapping cell is that the thin charge trapping layer reduces capacitive coupling between neighboring cells to improve performance and scalability.

Getting the charge onto the charge trapping layer

Electrons are moved onto the charge trapping layer similarly to the way that floating gate NOR flash is programmed, through channel hot electron (CHE) injection mechanism also known as

Hot-carrier injection

Hot carrier injection (HCI) is a phenomenon in solid-state electronic devices where an electron or a “hole” gains sufficient kinetic energy to overcome a potential barrier necessary to break an interface state. The term "hot" refers to the ...

. In brief, a high voltage is placed between the control gate while a medium-high voltage is applied on the source and the drain while a current is induced from the source to the drain. Those electrons that have gained sufficient energy in traversing through the high-field region near the drain will boil off from the channel to be injected into the charge trapping layer where they come to rest.

Removing a charge from the charge trapping layer

Charge Trapping flash is erased via hot hole injection (see

Hot-carrier injection

Hot carrier injection (HCI) is a phenomenon in solid-state electronic devices where an electron or a “hole” gains sufficient kinetic energy to overcome a potential barrier necessary to break an interface state. The term "hot" refers to the ...

) as opposed to the Fowler–Nordheim tunneling approach used in both NAND and NOR flash for erasure. This process uses a field, rather than the current used in FN, to move holes toward the charge trapping layer to remove the charge.

Manufacturing charge trapping flash

Charge trapping flash is similar in manufacture to floating gate flash with certain exceptions that serve to simplify manufacturing.

Materials differences from floating gate

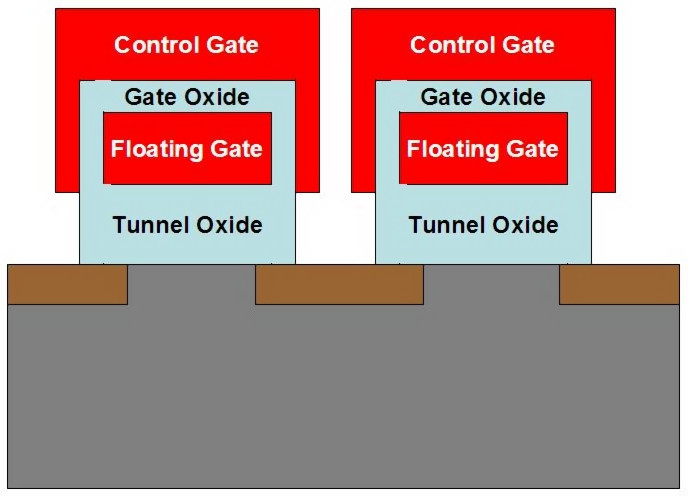

Both floating gate flash and charge trapping flash use a stacked gate structure in which a floating gate or charge trapping layer lies immediately above the channel, and below a control gate. The floating gate or charge trapping layer is insulated from the channel by a tunnel oxide layer and from the control gate by a gate oxide layer. Materials for all of these layers are the same with the exception of the storage layer, which is conductive polysilicon for the floating gate structure and is typically

silicon nitride

Silicon nitride is a chemical compound of the elements silicon and nitrogen. (''Trisilicon tetranitride'') is the most thermodynamically stable and commercially important of the silicon nitrides, and the term ″''Silicon nitride''″ commonly re ...

for the charge trap.

Relationship of charge trapping to silicon nanocrystals

Freescale Semiconductor

Freescale Semiconductor, Inc. was an American semiconductor manufacturer. It was created by the divestiture of the Semiconductor Products Sector of Motorola in 2004. Freescale focused their integrated circuit products on the automotive, embedde ...

manufactures a somewhat similar technology the company calls "Thin Film Storage" in its

microcontroller

A microcontroller (MC, uC, or μC) or microcontroller unit (MCU) is a small computer on a single integrated circuit. A microcontroller contains one or more CPUs (processor cores) along with memory and programmable input/output peripherals. Pro ...

or MCU line. The Freescale approach uses silicon nanocrystals as conductive islands in a nonconductive layer of silicon oxide.

Like the more conventional

silicon nitride

Silicon nitride is a chemical compound of the elements silicon and nitrogen. (''Trisilicon tetranitride'') is the most thermodynamically stable and commercially important of the silicon nitrides, and the term ″''Silicon nitride''″ commonly re ...

charge trap, electrons do not flow from one side of the floating gate to the other, extending the cell's wear.

This nanocrystal approach is being manufactured in volume by Freescale and charge trapping storage in general is in development at ST Microelectronics, Philips, Renesas, Samsung, Toshiba, Atmel, and Spansion.

Process differences from Floating Gate

Since the nitride charge trapping layer is nonconductive, it does not need to be patterned – all the charge traps are already insulated from each other. This can be used to simplify manufacturing.

Floating gate structures have required more elaborate gate dielectrics for the past few process generations and today commonly use an ONO (oxide-nitride-oxide) structure which is more complex to manufacture and is unnecessary in a charge-trapping flash.

One advantage of the nitride layer is that it is less sensitive to high temperature fabrication processing than is the polysilicon used in a floating gate. This simplifies processing of the layers above the charge trap.

MirrorBit Flash memory

Spansion's MirrorBit Flash and Saifun's NROM are two flash memories that use a charge trapping mechanism in nitride to store two bits onto the same cell effectively doubling the memory capacity of a chip. This is done by placing charges on either side of the charge trap layer. The cell is read by using forward and reverse currents through the channel to read either side of the charge trap.

MirrorBit operation – getting 2 bits onto the cell

During CHE programming (figure 2) the hot electrons are injected from the channel into the charge trapping layer toward the biased drain end of the channel, but not from the floating source end of the channel. By allowing the transistor's source and drain to switch from one end of the channel to the other, charges can be injected and stored into the charge trapping layer over either end of the channel.

In a similar way, one end of the charge trapping cell can be erased by placing the erasing field at one end or the other of the channel, allowing the other end to float as shown in figure 3. Band-to-band Hot Hole Erase creates holes that are trapped locally some of which recombine with electrons to remove the charge from that end of the charge trap.

Reading 2 bits from the cell

The MirrorBit read is performed very simply by reversing the source and drain contacts. The junction depletion region extending from the drain side shields the channel from the charge on the side of the charge trapping cell that overlies the drain. The net result of this is that the drain-side charge has little effect on the current running through the channel, while the source-side charge determines the threshold of the transistor.

When source and drain are reversed, the opposite side's charge determines the transistor's threshold.

This way two different charge levels at either end of the charge trapping cell will cause two different currents to flow through the cell, depending on the direction of the current flow.

Later developments

Charge trapping NAND – Samsung and others

Samsung Electronics

Samsung Electronics Co., Ltd. (SEC; stylized as SΛMSUNG; ) is a South Korean multinational major appliance and consumer electronics corporation founded on 13 January 1969 and headquartered in Yeongtong District, Suwon, South Korea. It is curr ...

in 2006 disclosed its research into the use of Charge Trapping Flash to allow continued scaling of NAND technology using cell structures similar to the planar structures in use at that time. The technology depends on a

SONOS

Sonos, Inc. is an American audio equipment manufacturer headquartered in Santa Barbara, California. The company was founded in 2002 by John MacFarlane, Craig Shelburne, Tom Cullen, and Trung Mai.

Sonos has partnered with over 100 companies th ...

(silicon–oxide–nitride–oxide–silicon) or MONOS (metal-ONOS) capacitor structure, storing the information in charge traps in the nitride layer.

Samsung disclosed two cell structures: TANOS (Titanium, Alumina, Nitride, Oxide, Silicon) for 40 nm, where researchers believed that the existing 3D cap structure (described in detail later in this article) could not be manufactured, and THNOS, in which the aluminum oxide would be replaced with an undisclosed

high-k dielectric material. The high-k material was expected to yield longer retention times than the aluminum oxide structure.

In a cap structure the control gate is extended to form a barrier between adjacent floating gates in a conventional floating gate cell.

Over the following five years many device designers found ways to push the cap structure to increasingly tighter process geometries, successfully producing NAND at the 30 nm node with this approach.

Charge trapping is still viewed as a future technology for NAND flash, but it is being considered more for vertical structures than for planar cells.

Why NAND needs charge trapping technology

NAND flash has been scaling very aggressively (figure 4). As processes migrate, the width of the interface of the control gate and the floating gate shrinks in proportion to the square of the shrink, and the spacing between floating gates shrinks in proportion to the process shrink, but the floating gate's thickness remains the same (the thinner the floating gate is made the less tolerant the cell becomes to electron loss). This means that the coupling between adjacent floating gates becomes larger than the coupling between the control gate and the floating gate, leading to data corruption between adjacent bits.

As processes continue to shrink, this becomes increasingly problematic. For this reason the control gate in modern NAND flash has been reconfigured to cap the floating gate. In a cap structure the control gate is extended to form a barrier between adjacent floating gates in a conventional floating gate cell (see figure 5). This serves to reduce coupling to the adjacent floating gate while increasing the coupling between the floating gate and the control gate. One drawback is that the control gate couples to the channel, so measures must be taken to minimize this coupling.

It was believed in 2006 that the existing floating gate cap structure could not be manufactured at processes smaller than the 50 nm node due to difficulties in producing the complex three-layer ONO gate oxide that these devices require.

Samsung even announced in late 2006 that by 2008 it would put such a device into production at the 40 nm process node, but over the five years following this announcement many device designers found ways to push the cap structure to increasingly tighter process geometries, successfully producing NAND down to 20 nm node with this approach.

The charge trapping approach is still viewed as a future for NAND flash for processes smaller than 20 nm and is being considered for both planar as well as vertical 3D structures.

When this change might occur

Today SanDisk asserts that the company expects to continue to use conventional NAND structures into a second node in the 10–19 nm range. This implies that standard device structures could stay in place until the industry reaches 10 nm, however the challenges of producing a reliable floating gate become more severe with each process shrink.

On the other hand, the

International Technology Roadmap for Semiconductors

The International Technology Roadmap for Semiconductors (ITRS) is a set of documents that was coordinated and organized by Semiconductor Research Corporation and produced by a group of experts in the semiconductor industry. These experts were rep ...

(ITRS) process technology roadmap's 2010 Process Integration, Devices, and Structures (PIDS) tables show adoption of charge trapping starting at 22 nm in 2012, and becoming mainstream in 2014 with the 20 nm process.

It is possible that a planar charge trapping cell will be used for future processes. No manufacturers have yet disclosed their processes for geometries smaller than 19 nm.

Charge trapping layers for vertical structures

Vertical structures are seen as a logical next step for NAND flash, once further horizontal scaling becomes inviable. Since vertical features cannot be etched sideways, a charge trapping layer becomes a very interesting way to build a vertical NAND flash string.

Toshiba

is a Japanese multinational electronics company headquartered in Minato, Tokyo. Its diversified products and services include power, industrial and social infrastructure systems, elevators and escalators, electronic components, semiconductors ...

and

Samsung Electronics

Samsung Electronics Co., Ltd. (SEC; stylized as SΛMSUNG; ) is a South Korean multinational major appliance and consumer electronics corporation founded on 13 January 1969 and headquartered in Yeongtong District, Suwon, South Korea. It is curr ...

have disclosed prototypes for vertical charge trapping NAND structures.

Toshiba's BiCS and Samsung's 3D NAND

Toshiba in 2007 and Samsung in 2009 announced the development of 3D

V-NAND, a means of building a standard NAND flash bit string vertically rather than horizontally to increase the number of bits in a given area of silicon.

A rough idea of the cross section of this is shown in figure 6. In this drawing the red portions represent conductive polysilicon, the blue is silicon dioxide insulating layers, and the yellow is the nitride charge trapping layer.

The vertical structures (only one shown) are cylinders that implement a channel that is wrapped in alternating dielectric and charge trapping layers (blue and yellow). To manufacture such a device layers of conducting polysilicon and silicon dioxide dielectric are deposited first on top of a silicon substrate that contains standard CMOS logic elements. A trench is then etched and its walls are deposited first with silicon dioxide (blue), then

silicon nitride

Silicon nitride is a chemical compound of the elements silicon and nitrogen. (''Trisilicon tetranitride'') is the most thermodynamically stable and commercially important of the silicon nitrides, and the term ″''Silicon nitride''″ commonly re ...

(yellow), then another silicon dioxide (blue) layer, forming the gate dielectric, the charge trap, and the tunnel dielectric in that order. Finally the hole is filled with conducting polysilicon (red) which forms the channel. The alternating layers of conductive polysilicon function as the control gates in this structure.

This structure takes advantage of the fact that the charge trap layer does not need to be insulated between each control gate, so it need not be etched in the vertical direction.

Charge trapping in embedded memories

One advantage that charge trapping flash has over other technologies is that it can be relatively easily embedded with a standard logic process. A standard logic process can be converted to a logic-plus-flash process through the addition of three more high voltage masks and three more core CTF masks, and none of these six masks is a critical layer (i.e. needs to use the most advanced part of the process). All other logic processes can be shared directly.

Bandgap-Engineered Charge-Trapping Memory Devices

In ITRS PIDS 2013, it was clearly mentioned that bandgap engineered charge-trapping devices are needed to resolve the retention and erase dilemma. SONOS using a simple tunnel oxide, however, is not suitable for NAND application-once electrons are trapped in deep SiN trap levels they are difficult to detrap even under high electric field. In order to erase the device quickly holes in the substrate are injected into the SiN to neutralize the electron charge. Since the hole barrier for SiO2 is high (~4.1 eV), hole injection efficiency is poor and sufficient hole current is only achievable by using very thin tunnel oxide (~ 2 nm). Such thin tunnel oxide, however, results in poor data retention because direct hole tunneling from the substrate under the weak built-in field caused by storage electrons cannot be stopped (the rate of direct tunneling is a strong function of the barrier thickness but only weakly depends on the electric field, thus the weak built-in field by charge storage is sufficient to cause direct hole tunneling from the substrate which ruins the data retention). Several variations of SONOS have been proposed. Tunnel dielectric engineering concepts are used to modify the tunneling barrier properties to create "variable thickness" tunnel dielectric. For example, triple ultra-thin (1–2 nm) layers of ONO are introduced to replace the single oxide (BE-SONOS)

. T. Lue, et al, IEDM 2005 Under high electric field, the upper two layers of oxide and nitride are offset above the Si valence band, and substrate holes readily tunnel through the bottom thin oxide and inject into the thick SiN trapping layer above. In data storage mode, the weak electric field does not offset the triple layer and both electrons in the SiN and holes in the substrate are blocked by the total thickness of the triple layer. Later BE-SONOS is added high-K (Al2O3) and metal gate to enhance the erase performances, the so-called BE-MANOS

. C. Lai, et al, NVSMW 2007 It is suggested to add a buffer oxide in between high-K Al2O3 and SiN to improve the retention. Right now the mass production 3D NAND adopts a similar structure of BE-MANOS, with some variations of detail recipe tuning by each individual companies. The concept of bandgap engineered for tunneling barrier is recognized as a necessary path for charge-trapping devices.

Although charge trapping NAND can help the GCR and FG cross talk issues and thus promises scaling below 20nm it does not help the fundamental limitations such as word line breakdown and too few electrons. Therefore, in the

roadmap trend it occupies a transition role between planar FG and 3D NAND. When charge trapping devices are used to build 3D NAND, the larger device size naturally solves the electron number and the word line breakdown issues.

Further reading

*

*

*

*

References

{{Reflist

Non-volatile memory

Arab inventions

Egyptian inventions

Israeli inventions

Japanese inventions

MOSFETs

The MirrorBit cell uses a charge trapping layer not only as a substitute for a conventional floating gate, but it also takes advantage of the non-conducting nature of the charge storage nitride to allow two bits to share the same memory cell. Shown in Figure 1 the bits reside at opposite ends of the cell and can be read by running a current through the channel in different directions.

Products have been successfully made to combine this approach with multilevel cell technology to contain four bits on a cell.

The MirrorBit cell uses a charge trapping layer not only as a substitute for a conventional floating gate, but it also takes advantage of the non-conducting nature of the charge storage nitride to allow two bits to share the same memory cell. Shown in Figure 1 the bits reside at opposite ends of the cell and can be read by running a current through the channel in different directions.

Products have been successfully made to combine this approach with multilevel cell technology to contain four bits on a cell.