Pentium Pro on:

[Wikipedia]

[Google]

[Amazon]

The Pentium Pro is a sixth-generation

The lead architect of Pentium Pro was Fred Pollack who was specialized in superscalarity and had also worked as the lead engineer of the

The lead architect of Pentium Pro was Fred Pollack who was specialized in superscalarity and had also worked as the lead engineer of the

sandpile.org

- IA-32 implementation - Intel P6 * Clockrate: 150, 166, 180, 200 MHz, (capable of 233 MHz on some motherboards) * First release: November 1995

* L1 cache: 16, 16 KB (data + instructions)

* L2 cache: 512 KB external chip on CPU module clocked at CPU-speed

* Socket: Socket 8

* Multiplier: Locked at 5×

* Front-side bus: 60 and 66 MHz

* VCore: 3.1–3.3 V (has on-board voltage regulator)

* Fabrication: 0.25 μm

* Clockrate: Based on the Deschutes-generation Pentium II

* First release: 1997

* Supports MMX technology

* L1 cache: 16, 16 KB (data + instructions)

* L2 cache: 512 KB external chip on CPU module clocked at CPU-speed

* Socket: Socket 8

* Multiplier: Locked at 5×

* Front-side bus: 60 and 66 MHz

* VCore: 3.1–3.3 V (has on-board voltage regulator)

* Fabrication: 0.25 μm

* Clockrate: Based on the Deschutes-generation Pentium II

* First release: 1997

* Supports MMX technology

Backside Bus

searchstorage.techtarget.com

Intel Pentium Pro images and descriptions

cpu-collection.de

CPU-INFO: Intel Pentium Pro, indepth processor history

web.archive.org {{Intel processors, p6 Computer-related introductions in 1995 Intel x86 microprocessors Superscalar microprocessors 32-bit microprocessors

x86

x86 (also known as 80x86 or the 8086 family) is a family of complex instruction set computer (CISC) instruction set architectures initially developed by Intel based on the Intel 8086 microprocessor and its 8088 variant. The 8086 was introd ...

microprocessor

A microprocessor is a computer processor where the data processing logic and control is included on a single integrated circuit, or a small number of integrated circuits. The microprocessor contains the arithmetic, logic, and control circu ...

developed and manufactured by Intel

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California. It is the world's largest semiconductor chip manufacturer by revenue, and is one of the developers of the x86 seri ...

and introduced on November 1, 1995. It introduced the P6 microarchitecture

The P6 microarchitecture is the sixth-generation Intel x86 microarchitecture, implemented by the Pentium Pro microprocessor that was introduced in November 1995. It is frequently referred to as i686. It was succeeded by the NetBurst microarch ...

(sometimes termed i686) and was originally intended to replace the original Pentium

Pentium is a brand used for a series of x86 architecture-compatible microprocessors produced by Intel. The original Pentium processor from which the brand took its name was first released on March 22, 1993. After that, the Pentium II and Pe ...

in a full range of applications. While the Pentium and Pentium MMX had 3.1 and 4.5 million transistor

upright=1.4, gate (G), body (B), source (S) and drain (D) terminals. The gate is separated from the body by an insulating layer (pink).

A transistor is a semiconductor device used to Electronic amplifier, amplify or electronic switch, switch e ...

s, respectively, the Pentium Pro contained 5.5 million transistors. Later, it was reduced to a more narrow role as a server and high-end desktop processor and was used in supercomputer

A supercomputer is a computer with a high level of performance as compared to a general-purpose computer. The performance of a supercomputer is commonly measured in floating-point operations per second ( FLOPS) instead of million instructions ...

s like ASCI Red

ASCI Red (also known as ASCI Option Red or TFLOPS) was the first computer built under the Accelerated Strategic Computing Initiative ( ASCI), the supercomputing initiative of the United States government created to help the maintenance of the ...

, the first computer to reach the trillion ''floating point operations per second'' (teraFLOPS

In computing, floating point operations per second (FLOPS, flops or flop/s) is a measure of computer performance, useful in fields of scientific computations that require floating-point calculations. For such cases, it is a more accurate meas ...

) performance mark. The Pentium Pro was capable of both dual- and quad-processor configurations. It only came in one form factor, the relatively large rectangular Socket 8

The Socket 8 CPU socket was used exclusively with the Intel Pentium Pro and Pentium II Overdrive computer processors. Intel discontinued Socket 8 in favor of Slot 1 with the introduction of the Pentium II and Slot 2 with the release of ...

. The Pentium Pro was succeeded by the Pentium II Xeon

Xeon ( ) is a brand of x86 microprocessors designed, manufactured, and marketed by Intel, targeted at the non-consumer workstation, server, and embedded system markets. It was introduced in June 1998. Xeon processors are based on the same arc ...

in 1998.

Microarchitecture

The lead architect of Pentium Pro was Fred Pollack who was specialized in superscalarity and had also worked as the lead engineer of the

The lead architect of Pentium Pro was Fred Pollack who was specialized in superscalarity and had also worked as the lead engineer of the Intel iAPX 432

The iAPX 432 (''Intel Advanced Performance Architecture'') is a discontinued computer architecture introduced in 1981. It was Intel's first 32-bit processor design. The main processor of the architecture, the ''general data processor'', is imp ...

.

Summary

The Pentium Pro incorporated a new microarchitecture, different from the Pentium's P5 microarchitecture. It has a decoupled, 14-stage superpipelined architecture which used an instruction pool. The Pentium Pro ( P6) implemented many radical architectural differences mirroring other contemporaryx86

x86 (also known as 80x86 or the 8086 family) is a family of complex instruction set computer (CISC) instruction set architectures initially developed by Intel based on the Intel 8086 microprocessor and its 8088 variant. The 8086 was introd ...

designs such as the NexGen Nx586 and Cyrix 6x86

The Cyrix 6x86 is a line of sixth-generation, 32-bit x86 microprocessors designed and released by Cyrix in 1995. Cyrix, being a fabless company, had the chips manufactured by IBM and SGS-Thomson. The 6x86 was made as a direct competitor to Int ...

. The Pentium Pro pipeline had extra decode stages to dynamically translate IA-32

IA-32 (short for "Intel Architecture, 32-bit", commonly called i386) is the 32-bit version of the x86 instruction set architecture, designed by Intel and first implemented in the 80386 microprocessor in 1985. IA-32 is the first incarnation o ...

instructions into buffered micro-operation

In computer central processing units, micro-operations (also known as micro-ops or μops, historically also as micro-actions) are detailed low-level instructions used in some designs to implement complex machine instructions (sometimes termed m ...

sequences which could then be analysed, reordered, and renamed in order to detect parallelizable operations that may be issued to more than one execution unit

In computer engineering, an execution unit (E-unit or EU) is a part of the central processing unit (CPU) that performs the operations and calculations as instructed by the computer program. It may have its own internal control sequence unit (not ...

at once. The Pentium Pro thus featured out of order execution

In computer engineering, out-of-order execution (or more formally dynamic execution) is a paradigm used in most high-performance central processing units to make use of instruction cycles that would otherwise be wasted. In this paradigm, a process ...

, including speculative execution

Speculative execution is an optimization technique where a computer system performs some task that may not be needed. Work is done before it is known whether it is actually needed, so as to prevent a delay that would have to be incurred by doing ...

via register renaming

In computer architecture, register renaming is a technique that abstracts logical registers from physical registers.

Every logical register has a set of physical registers associated with it.

When a machine language instruction refers to a partic ...

. It also had a wider 36-bit address bus

In computer architecture, a bus (shortened form of the Latin '' omnibus'', and historically also called data highway or databus) is a communication system that transfers data between components inside a computer, or between computers. This e ...

, usable by Physical Address Extension

In computing, Physical Address Extension (PAE), sometimes referred to as Page Address Extension,

is a memory management feature for the x86 architecture. PAE was first introduced by Intel in the Pentium Pro, and later by AMD in the Athlon proces ...

(PAE), allowing it to access up to 64 GB of memory.

The Pentium Pro has an 8 KB instruction cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, which ...

, from which up to 16 bytes are fetched on each cycle and sent to the instruction decoder

A central processing unit (CPU), also called a central processor, main processor or just processor, is the electronic circuitry that executes instructions comprising a computer program. The CPU performs basic arithmetic, logic, controlling, an ...

s. There are three instruction decoders. The decoders are unequal in ability: only one can decode any x86 instruction, while the other two can only decode simple x86 instructions. This restricts the Pentium Pro's ability to decode multiple instructions simultaneously, limiting superscalar execution. x86 instructions are decoded into 118-bit micro-operation

In computer central processing units, micro-operations (also known as micro-ops or μops, historically also as micro-actions) are detailed low-level instructions used in some designs to implement complex machine instructions (sometimes termed m ...

s (micro-ops). The micro-ops are reduced instruction set computer (RISC)-like; that is, they encode an operation, two sources, and a destination. The general decoder can generate up to four micro-ops per cycle, whereas the simple decoders can generate one micro-op each per cycle. Thus, x86 instructions that operate on the memory (e.g., add this register to this location in the memory) can only be processed by the general decoder, as this operation requires a minimum of three micro-ops. Likewise, the simple decoders are limited to instructions that can be translated into one micro-op. Instructions that require more micro-ops than four are translated with the assistance of a sequencer, which generates the required micro-ops over multiple clock cycles. The Pentium Pro was the first processor in the x86-family to support upgradeable microcode

In processor design, microcode (μcode) is a technique that interposes a layer of computer organization between the central processing unit (CPU) hardware and the programmer-visible instruction set architecture of a computer. Microcode is a laye ...

under BIOS

In computing, BIOS (, ; Basic Input/Output System, also known as the System BIOS, ROM BIOS, BIOS ROM or PC BIOS) is firmware used to provide runtime services for operating systems and programs and to perform hardware initialization during the ...

and/or operating system

An operating system (OS) is system software that manages computer hardware, software resources, and provides common services for computer programs.

Time-sharing operating systems schedule tasks for efficient use of the system and may also in ...

(OS) control.

Micro-ops exit the re-order buffer (ROB) and enter a reserve station (RS), where they await dispatch to the execution units. In each clock cycle, up to five micro-ops can be dispatched to five execution units. The Pentium Pro has a total of six execution units: two integer units, one floating-point unit

In computing, floating-point arithmetic (FP) is arithmetic that represents real numbers approximately, using an integer with a fixed precision, called the significand, scaled by an integer exponent of a fixed base. For example, 12.345 can b ...

(FPU), a load unit, store address unit, and a store data unit. One of the integer units shares the same ports as the FPU, and therefore the Pentium Pro can only dispatch one integer micro-op and one floating-point micro-op, or two integer micro-ops per a cycle, in addition to micro-ops for the other three execution units. Of the two integer units, only the one that shares the path with the FPU on port 0 has the full complement of functions such as a barrel shifter, multiplier, divider, and support for LEA instructions. The second integer unit, which is connected to port 1, does not have these facilities and is limited to simple operations such as add, subtract, and the calculation of branch target addresses.

The FPU executes floating-point operations. Addition and multiplication are pipelined and have a latency of three and five cycles, respectively. Division and square-root are not pipelined and are executed in separate units that share the FPU's ports. Division and square root have a latency of 18-36 and 29-69 cycles, respectively. The smallest number is for single precision (32-bit) floating-point numbers and the largest for extended precision (80-bit) numbers. Division and square root can operate simultaneously with adds and multiplies, preventing them from executing only when the result has to be stored in the ROB.

After the microprocessor was released, a bug was discovered in the floating point unit

Floating may refer to:

* a type of dental work performed on horse teeth

* use of an isolation tank

* the guitar-playing technique where chords are sustained rather than scratched

* ''Floating'' (play), by Hugh Hughes

* Floating (psychological ...

, commonly called the "Pentium Pro and Pentium II FPU bug" and by Intel as the "flag erratum". The bug occurs under some circumstances during floating point-to-integer conversion when the floating point number will not fit into the smaller integer format, causing the FPU to deviate from its documented behaviour. The bug is considered to be minor and occurs under such special circumstances that very few, if any, software programs are affected.

The Pentium Pro P6 microarchitecture

The P6 microarchitecture is the sixth-generation Intel x86 microarchitecture, implemented by the Pentium Pro microprocessor that was introduced in November 1995. It is frequently referred to as i686. It was succeeded by the NetBurst microarch ...

was used in one form or another by Intel for more than a decade. The pipeline would scale from its initial 150 MHz start, all the way up to 1.4 GHz with the "Tualatin" Pentium III

The Pentium III (marketed as Intel Pentium III Processor, informally PIII or P3) brand refers to Intel's 32-bit x86 desktop and mobile CPUs based on the sixth-generation P6 microarchitecture introduced on February 28, 1999. The brand's initial p ...

. The design's various traits would continue after that in the derivative core called "Banias

Banias or Banyas ( ar, بانياس الحولة; he, בניאס, label=Modern Hebrew; Judeo-Aramaic, Medieval Hebrew: פמייס, etc.; grc, Πανεάς) is a site in the Golan Heights near a natural spring, once associated with the Greek g ...

" in Pentium M

The Pentium M is a family of mobile 32-bit single-core x86 microprocessors (with the modified Intel P6 microarchitecture) introduced in March 2003 and forming a part of the Intel Carmel notebook platform under the then new Centrino brand. The ...

and Intel Core

Intel Core is a line of streamlined midrange consumer, workstation and enthusiast computer central processing units (CPUs) marketed by Intel Corporation. These processors displaced the existing mid- to high-end Pentium processors at the time ...

( Yonah), which itself would evolve into the Core microarchitecture

The Intel Core microarchitecture (provisionally referred to as Next Generation Micro-architecture, and developed as Merom) is a multi-core processor microarchitecture launched by Intel in mid-2006. It is a major evolution over the Yonah, the p ...

( Core 2 processor) in 2006 and onward.

Instruction set

The Pentium Pro (P6) introduced new instructions into the Intel range; the CMOVxx (‘conditional move’) instructions can move a value that is either the contents of a register or memory location into another register or not, according to some predicate logical condition xx on the flags register, xx being a flags predicate code as given in the condition for conditional jump instructions. So for example CMOVNE moves a specified value into a register or not depending on whether the NE (not-equal) condition is true in the flags register ie Z flag = 0. This allows the evaluation of if-then-else operations and for example the ? : operation in C. These instructions give a performance boost by allowing the avoidance of costly jump and branch instructions. In eg CMOVxx destreg1, source_operand2 the first operand is the destination register, the second the source register or memory location. The second operand unfortunately can not be an immediate (in-line constant) value and such a constant would have to be placed in a register first. The predicate code xx can take the full range of values as allowed in conditional branches. A second development was the documentation of the UD2 illegal instruction. This op code is reserved and guaranteed to cause an illegal instruction exception on the P6 and all later processors. This allows developers to easily crash the current program in a future-proof fashion when a bug is detected by software.Performance

Despite being advanced for the time, the Pentium Pro's out-of-order register renaming architecture had trouble running16-bit

16-bit microcomputers are microcomputers that use 16-bit microprocessors.

A 16-bit register can store 216 different values. The range of integer values that can be stored in 16 bits depends on the integer representation used. With the two mos ...

code and mixed code (8-bit

In computer architecture, 8-bit Integer (computer science), integers or other Data (computing), data units are those that are 8 bits wide (1 octet (computing), octet). Also, 8-bit central processing unit (CPU) and arithmetic logic unit (ALU) arc ...

with 16-bit (8/16), or 16-bit with 32-bit

In computer architecture, 32-bit computing refers to computer systems with a processor, memory, and other major system components that operate on data in 32-bit units. Compared to smaller bit widths, 32-bit computers can perform large calculation ...

(16/32), as using partial registers cause frequent pipeline flushing. Specific use of partial registers was then a common performance optimization, as it incurred no performance penalty on pre-P6 Intel processors; also, the dominant operating systems at the time of the Pentium Pro's release were 16-bit DOS

DOS is shorthand for the MS-DOS and IBM PC DOS family of operating systems.

DOS may also refer to:

Computing

* Data over signalling (DoS), multiplexing data onto a signalling channel

* Denial-of-service attack (DoS), an attack on a communicat ...

, and mixed 16/32-bit Windows 3.1x

Windows 3.1 is a major release of Microsoft Windows. It was released to manufacturing on April 6, 1992, as a successor to Windows 3.0.

Like its predecessors, the Windows 3.1 series ran as a shell on top of MS-DOS. Codenamed Janus, Windows 3 ...

and Windows 95

Windows 95 is a consumer-oriented operating system developed by Microsoft as part of its Windows 9x family of operating systems. The first operating system in the 9x family, it is the successor to Windows 3.1x, and was released to manufacturin ...

(although the latter requires a 32-bit 80386 CPU, much of its code is still 16-bit for performance reasons, such as USER.exe). This, with the high cost of Pentium Pro systems, led to tepid sales among PC buyers at the time. To fully use the Pentium Pro's P6 microarchitecture

The P6 microarchitecture is the sixth-generation Intel x86 microarchitecture, implemented by the Pentium Pro microprocessor that was introduced in November 1995. It is frequently referred to as i686. It was succeeded by the NetBurst microarch ...

, a fully 32-bit operating system is needed, such as Windows NT

Windows NT is a proprietary graphical operating system

An operating system (OS) is system software that manages computer hardware, software resources, and provides common services for computer programs.

Time-sharing operating systems sc ...

, Linux

Linux ( or ) is a family of open-source Unix-like operating systems based on the Linux kernel, an operating system kernel first released on September 17, 1991, by Linus Torvalds. Linux is typically packaged as a Linux distribution, which ...

, Unix

Unix (; trademarked as UNIX) is a family of multitasking, multiuser computer operating systems that derive from the original AT&T Unix, whose development started in 1969 at the Bell Labs research center by Ken Thompson, Dennis Ritchie, and ot ...

, or OS/2

OS/2 (Operating System/2) is a series of computer operating systems, initially created by Microsoft and IBM under the leadership of IBM software designer Ed Iacobucci. As a result of a feud between the two companies over how to position OS/2 ...

. The performance issues on legacy code were later partly mitigated by Intel with the Pentium II.

Compared to RISC microprocessors, the Pentium Pro, when introduced, slightly outperformed the fastest RISC microprocessors on integer performance when running the SPECint95 benchmark, but floating-point performance was significantly lower, half that of some RISC microprocessors. The Pentium Pro's integer performance lead disappeared rapidly, first overtaken by the MIPS Technologies

MIPS Technologies, Inc., formerly MIPS Computer Systems, Inc., was an American fabless semiconductor design company that is most widely known for developing the MIPS architecture and a series of RISC CPU chips based on it. MIPS provides proc ...

R10000

The R10000, code-named "T5", is a RISC microprocessor implementation of the MIPS IV instruction set architecture (ISA) developed by MIPS Technologies, Inc. (MTI), then a division of Silicon Graphics, Inc. (SGI). The chief designers are Chris Rowe ...

in January 1996, and then by Digital Equipment Corporation

Digital Equipment Corporation (DEC ), using the trademark Digital, was a major American company in the computer industry from the 1960s to the 1990s. The company was co-founded by Ken Olsen and Harlan Anderson in 1957. Olsen was president unt ...

's EV56 variant of the Alpha 21164

The Alpha 21164, also known by its code name, EV5, is a microprocessor developed and fabricated by Digital Equipment Corporation that implemented the Alpha instruction set architecture (ISA). It was introduced in January 1995, succeeding the Alp ...

.

Reviewers quickly noted the very slow writes to video memory as the weak spot of the P6 platform, with performance here being as low as 10% of an identically clocked Pentium system in benchmarks such as VIDSPEED. Methods to circumvent this included setting VESA drawing to system memory instead of video memory in games such as '' Quake'', and later on utilities such as FASTVID emerged, which could double performance in certain games by enabling the write combining

Write combining (WC) is a computer bus technique for allowing data to be combined and temporarily stored in a buffer the write combine buffer (WCB) to be released together later in burst mode instead of writing (immediately) as single bits or sma ...

features of the CPU. memory type range register

Memory type range registers (MTRRs) are a set of processor supplementary capability control registers that provide system software with control of how accesses to memory ranges by the CPU are cached. It uses a set of programmable model-specifi ...

s (MTRRs) are set automatically by Windows video drivers starting from ~1997, and there the improved cache/memory subsystem and FPU performance caused it to outclass the Pentium clock-for-clock in the emerging 3D games of the mid–to–late 1990s, particularly when using NT4. However, its lack of MMX implementation reduces performance in multimedia applications that made use of those instructions.

Caching

Likely Pentium Pro's most noticeable addition was its on-packageL2 cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, whic ...

, which ranged from 256 KB at introduction to 1 MB in 1997. At the time, manufacturing technology did not feasibly allow a large L2 cache to be integrated into the processor core. Intel instead placed the L2 die(s) separately in the package which still allowed it to run at the same clock speed as the CPU core. Additionally, unlike most motherboard-based cache schemes that shared the main system bus with the CPU, the Pentium Pro's cache had its own back-side bus

In personal computer microprocessor architecture, a back-side bus (BSB), or backside bus, was a computer bus used on early Intel platforms to connect the CPU to CPU cache memory, usually off-die L2. If a design utilizes it along with a front-sid ...

(called ''dual independent bus

A system bus is a single Bus (computing), computer bus that connects the major components of a computer system,

combining the functions of a Memory bus, data bus to carry information, an address bus to determine where it should be sent or read fro ...

'' by Intel). Because of this, the CPU could read main memory and cache concurrently, greatly reducing a traditional bottleneck. The cache was also "non-blocking", meaning that the processor could issue more than one cache request at a time (up to 4), reducing cache-miss penalties. (This is an example of MLP, Memory Level Parallelism.) These properties combined to produce an L2 cache that was immensely faster than the motherboard-based caches of older processors. This cache alone gave the CPU an advantage in input/output performance over older x86

x86 (also known as 80x86 or the 8086 family) is a family of complex instruction set computer (CISC) instruction set architectures initially developed by Intel based on the Intel 8086 microprocessor and its 8088 variant. The 8086 was introd ...

CPUs. In multiprocessor configurations, Pentium Pro's integrated cache skyrocketed performance in comparison to architectures which had each CPU sharing a central cache.

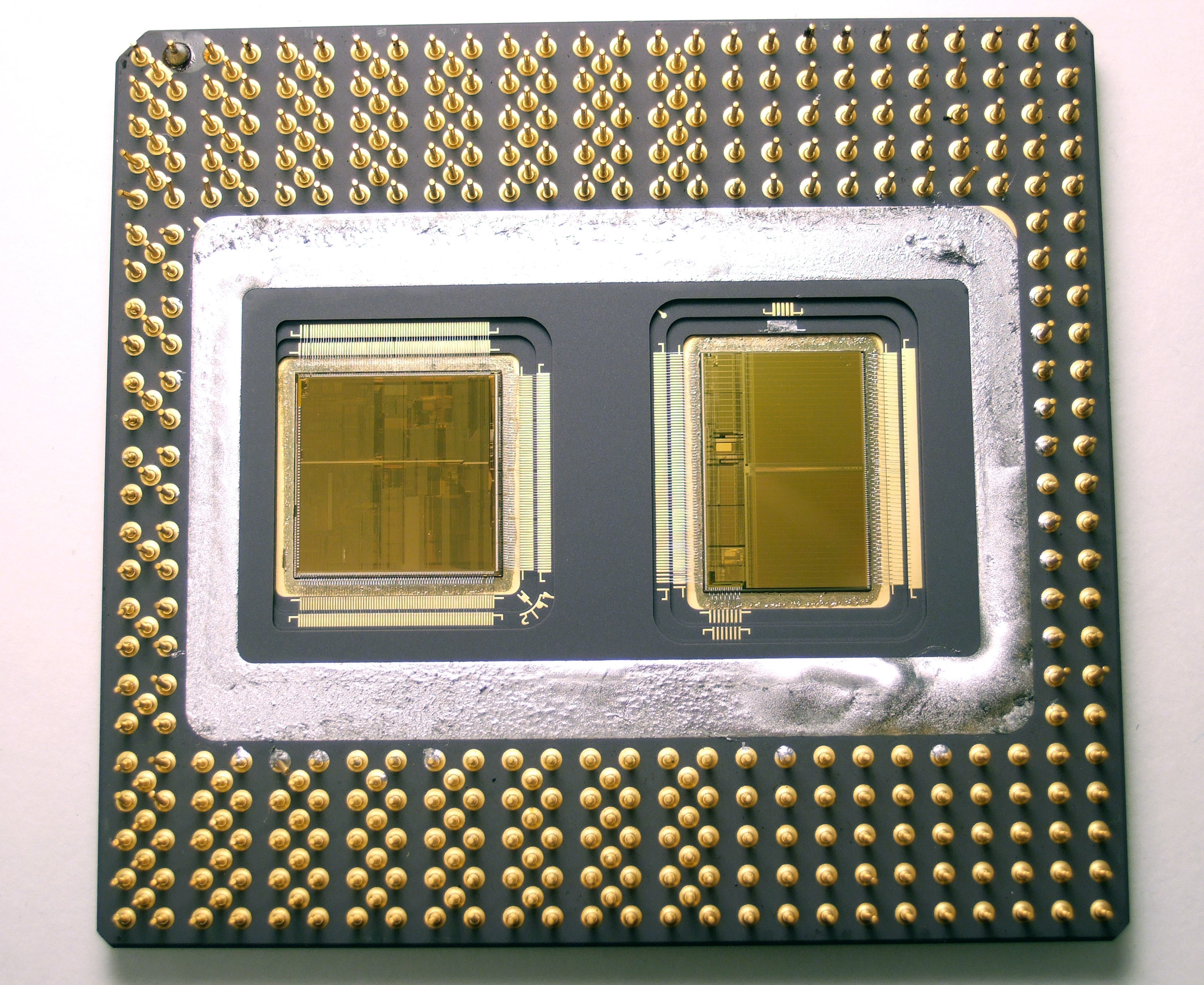

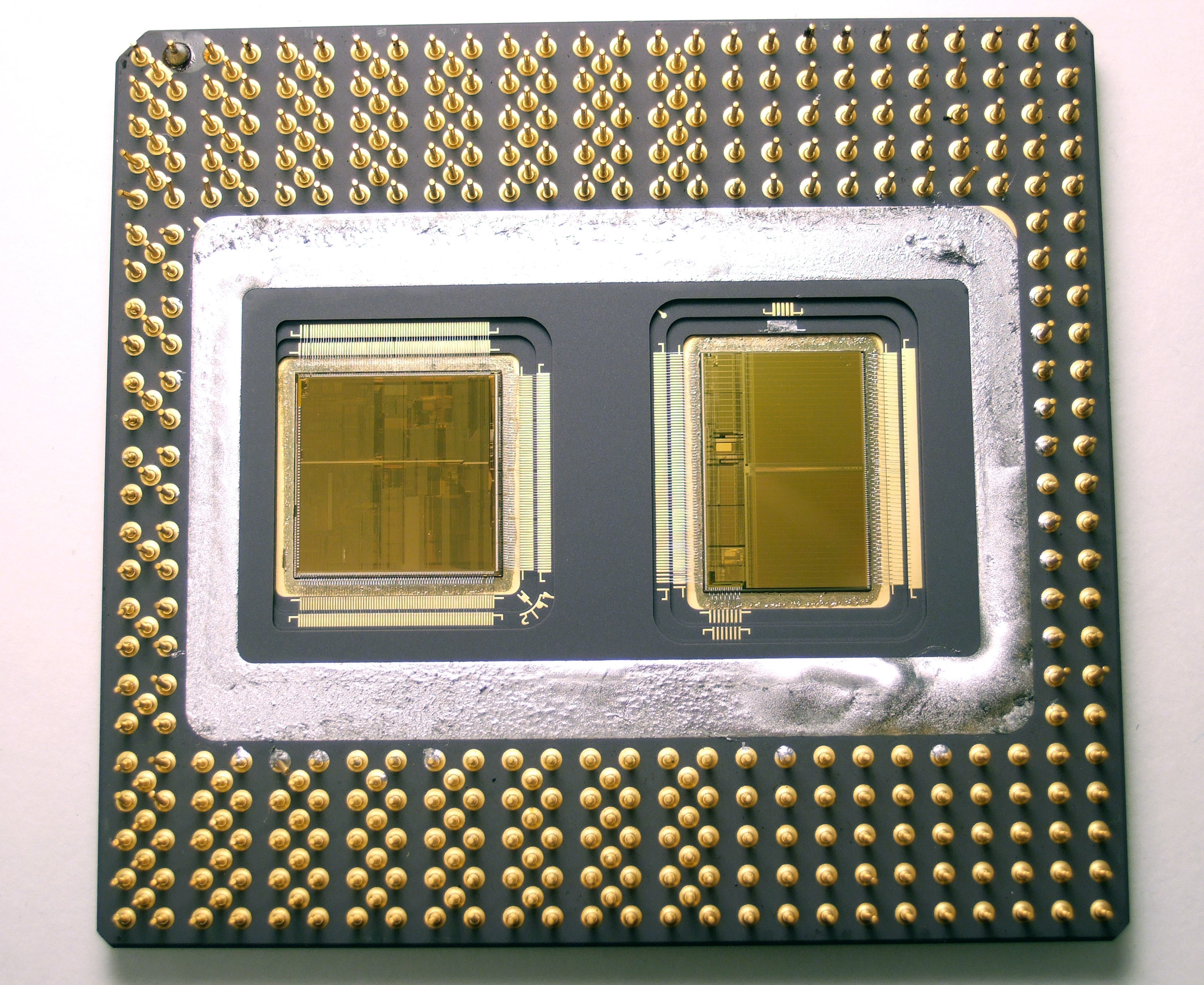

However, this far faster L2 cache did come with some complications. The Pentium Pro's "on-package cache" arrangement was unique. The processor and the cache were on separate dies in the same package and connected closely by a full-speed bus. The two or three dies had to be bonded together early in the production process, before testing was possible. This meant that a single, tiny flaw in either die made it necessary to discard the entire assembly, which was one of the reasons for the Pentium Pro's relatively low production yield and high cost. All versions of the chip were expensive, those with 1024 KB being particularly so, since it required two 512 KB cache dies as well as the processor die.

Available models

Pentium Pro clock speeds were 150, 166, 180 or 200 MHz with a 60 or 66 MHzexternal bus

In computer architecture, a bus (shortened form of the Latin '' omnibus'', and historically also called data highway or databus) is a communication system that transfers data between components inside a computer, or between computers. This e ...

clock. Some users chose to overclock

In computing, overclocking is the practice of increasing the clock rate of a computer to exceed that certified by the manufacturer. Commonly, operating voltage is also increased to maintain a component's operational stability at accelerated spe ...

their Pentium Pro chips, with the 200 MHz version often being run at 233 MHz, the 180 MHz version often being run at 200 MHz, and the 150 MHz version often being run at 166 MHz. The chip was popular in symmetric multiprocessing configurations, with dual and quad SMP server and workstation setups being commonplace.

In Intel's "Family/Model/Stepping" scheme, the Pentium Pro is family 6, model 1, and its Intel Product code is 80521.

Fabrication

The process used to fabricate the Pentium Pro processor die and its separate cache memory die changed, leading to a combination of processes used in the same package: * The 133 MHz Pentium Pro prototype processor die was fabricated in a 0.6 μm BiCMOS process. * The 150 MHz Pentium Pro processor die was fabricated in a 0.50 μmBiCMOS

Bipolar CMOS (BiCMOS) is a semiconductor technology that integrates two semiconductor technologies, those of the bipolar junction transistor and the CMOS (complementary metal-oxide-semiconductor) logic gate, into a single integrated circuit. In ...

process.

* The 166, 180, and 200 MHz Pentium Pro processor die was fabricated in a 0.35 μm BiCMOS process.

* The 256 KB L2 cache die was fabricated in a 0.50 μm BiCMOS process.

* The 512 and 1024 KB L2 cache die was fabricated in a 0.35 μm BiCMOS process.

Packaging

The Pentium Pro (up to 512 KB cache) is packaged in a ceramic multi-chip module (MCM). The MCM contains two underside cavities in which the microprocessor die and its companion cache die reside. The dies are bonded to a heat slug, whose exposed top helps the heat from the dies to be transferred more directly to cooling apparatus such as a heat sink. The dies are connected to the package using conventional wire bonding. The cavities are capped with a ceramic plate. The Pentium Pro with 1 MB of cache uses a plastic MCM. Instead of two cavities, there is only one, in which the three dies reside, bonded to the package instead of a heat slug. The cavities are filled in with epoxy. The MCM has 387 pins, of which approximately half are arranged in a pin grid array (PGA) and half in an interstitial pin grid array (IPGA). The packaging was designed forSocket 8

The Socket 8 CPU socket was used exclusively with the Intel Pentium Pro and Pentium II Overdrive computer processors. Intel discontinued Socket 8 in favor of Slot 1 with the introduction of the Pentium II and Slot 2 with the release of ...

.

Upgrade paths

In 1998, the 300/333 MHzPentium II Overdrive The Pentium OverDrive was a microprocessor marketing brand name used by Intel, to cover a variety of consumer upgrade products sold in the mid-1990s. It was originally released for 486 motherboards, and later some Pentium sockets. Intel dropped the ...

processor for Socket 8 was released. Featuring double L1 and 512 KB of full-speed L2 cache, it was produced by Intel as a drop-in upgrade option for owners of Pentium Pro systems. However, it only supported two-way glueless

In electronics, glue logic is the custom logic circuitry used to interface a number of off-the-shelf integrated circuits. This is often achieved using common, inexpensive 7400- or 4000-series components. In more complex cases, a programmable l ...

multiprocessing, not four-way or higher, which did not make it a usable upgrade for quad-processor systems. These specially packaged Pentium II Xeon processors were used to upgrade ASCI Red

ASCI Red (also known as ASCI Option Red or TFLOPS) was the first computer built under the Accelerated Strategic Computing Initiative ( ASCI), the supercomputing initiative of the United States government created to help the maintenance of the ...

, which became the first computer to reach the teraFLOPS performance mark with the Pentium Pro processor and then the first to exceed 2 teraFLOPS after the upgrade to Pentium II Xeon processors.

As Slot 1

Slot 1 refers to the physical and electrical specification for the connector used by some of Intel's microprocessors, including the Pentium Pro, Celeron, Pentium II and the Pentium III. Both single and dual processor configurations were impleme ...

motherboards became prevalent, several manufacturers released slocket adapters, such as the Tyan M2020, Asus C-P6S1, Tekram P6SL1, and the Abit KP6. The sockets allowed Pentium Pro processors to be used with Slot 1 motherboards. The Intel 440FX chipset explicitly supported both Pentium Pro and Pentium II processors, but the Intel 440BX

The Intel 440BX (codenamed Seattle) is a chipset from Intel, supporting Pentium II, Pentium III, and Celeron processors. It is also known as the i440BX and was released in April 1998. The official part number is 82443BX.

Features

The 440BX origi ...

and later Slot 1 chipsets did not explicitly support the Pentium Pro, so the Socket 8 slockets did not see wide use. Slockets, in the form of Socket 370

Socket 370 (also known as the PGA370 socket) is a CPU socket first used by Intel for Pentium III and Celeron processors to first complement and later replace the older Slot 1 CPU interface on personal computers. The "370" refers to the number of ...

to Slot 1 adapters, saw renewed popularity when Intel introduced Socket 370 Celeron

Celeron is Intel's brand name for low-end IA-32 and x86-64 computer microprocessor models targeted at low-cost personal computers.

Celeron processors are compatible with IA-32 software. They typically offer less performance per clock speed com ...

and Pentium III

The Pentium III (marketed as Intel Pentium III Processor, informally PIII or P3) brand refers to Intel's 32-bit x86 desktop and mobile CPUs based on the sixth-generation P6 microarchitecture introduced on February 28, 1999. The brand's initial p ...

processors.

Core specifications

Pentium Pro

* L1 cache: 8, 8 KB (data, instructions) *L2 cache

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from the main memory. A cache is a smaller, faster memory, located closer to a processor core, whic ...

: 256, 512 KB (one die) or 1024 KB (two 512 KB dies) in a multi-chip module

A multi-chip module (MCM) is generically an electronic assembly (such as a package with a number of conductor terminals or "pins") where multiple integrated circuits (ICs or "chips"), semiconductor dies and/or other discrete components are in ...

clocked at CPU-speed

* Socket: Socket 8

The Socket 8 CPU socket was used exclusively with the Intel Pentium Pro and Pentium II Overdrive computer processors. Intel discontinued Socket 8 in favor of Slot 1 with the introduction of the Pentium II and Slot 2 with the release of ...

* Front-side bus

A front-side bus (FSB) is a computer communication interface (bus) that was often used in Intel-chip-based computers during the 1990s and 2000s. The EV6 bus served the same function for competing AMD CPUs. Both typically carry data between the ...

: 60 and 66 MHz

* VCore: 3.1–3.3 V

* Fabrication: 0.50 μm or 0.35 BiCMOS

Bipolar CMOS (BiCMOS) is a semiconductor technology that integrates two semiconductor technologies, those of the bipolar junction transistor and the CMOS (complementary metal-oxide-semiconductor) logic gate, into a single integrated circuit. In ...

- IA-32 implementation - Intel P6 * Clockrate: 150, 166, 180, 200 MHz, (capable of 233 MHz on some motherboards) * First release: November 1995

Pentium II Overdrive

* L1 cache: 16, 16 KB (data + instructions)

* L2 cache: 512 KB external chip on CPU module clocked at CPU-speed

* Socket: Socket 8

* Multiplier: Locked at 5×

* Front-side bus: 60 and 66 MHz

* VCore: 3.1–3.3 V (has on-board voltage regulator)

* Fabrication: 0.25 μm

* Clockrate: Based on the Deschutes-generation Pentium II

* First release: 1997

* Supports MMX technology

* L1 cache: 16, 16 KB (data + instructions)

* L2 cache: 512 KB external chip on CPU module clocked at CPU-speed

* Socket: Socket 8

* Multiplier: Locked at 5×

* Front-side bus: 60 and 66 MHz

* VCore: 3.1–3.3 V (has on-board voltage regulator)

* Fabrication: 0.25 μm

* Clockrate: Based on the Deschutes-generation Pentium II

* First release: 1997

* Supports MMX technology

Bus and multiprocessor capabilities

The Pentium Pro used GTL+ signaling in its front-side bus. The Pentium Pro could be used by itself on up to four-way designs. Eight-way Pentium Pro computers were also built, but these used multiple buses. The design of the Pentium Pro bus was influenced byFuturebus

Futurebus, or IEEE 896, is a computer bus standard, intended to replace all local bus connections in a computer, including the CPU, memory, plug-in cards and even, to some extent, LAN links between machines. The effort started in 1979 and didn't c ...

, the Intel iAPX 432

The iAPX 432 (''Intel Advanced Performance Architecture'') is a discontinued computer architecture introduced in 1981. It was Intel's first 32-bit processor design. The main processor of the architecture, the ''general data processor'', is imp ...

bus, and elements of the Intel i960

Intel's i960 (or 80960) was a RISC-based microprocessor design that became popular during the early 1990s as an embedded microcontroller. It became a best-selling CPU in that segment, along with the competing AMD 29000. In spite of its success, ...

bus. Futurebus has been intended as an advanced bus to replace VMEbus

VMEbus (Versa Module Europa or Versa Module Eurocard bus) is a computer bus standard, originally developed for the Motorola 68000 line of CPUs, but later widely used for many applications and standardized by the IEC as ANSI/IEEE 1014-1987. I ...

used with the Motorola 68000

The Motorola 68000 (sometimes shortened to Motorola 68k or m68k and usually pronounced "sixty-eight-thousand") is a 16/32-bit complex instruction set computer (CISC) microprocessor, introduced in 1979 by Motorola Semiconductor Products Sector ...

from the late 1970s, but it stagnated in standardization committee for more than a decade if you count all the twists and turns. Intel's iAPX 432 initiative was also a commercial failure, but in the process they did learn how to build a split-transaction bus to support a cacheless multiprocessor system. The i960 had further developed the split-transaction iAPX 432 bus to include a cache coherency protocol, ending up with a feature set highly reminiscent of the original Futurebus ambitions.

The lead architect of i960 was superscalarity specialist Fred Pollack who was also the lead engineer of the Intel iAPX 432 and the lead architect of the i686 chip, the Pentium Pro. He was no doubt intimately familiar with all this history. The Pentium Pro was designed to include the 4-way SMP split-transaction cache-coherent bus as a mandatory feature of every chip produced. This also served to deny competition access to the socket to produce cloned processors.

While the Pentium Pro was not successful as a machine for the masses, due to poor 16-bit support for Windows 95, it did become highly successful in the file server space due to its advanced, integrated bus design, introducing many advanced features that had formerly only been available in the pricey workstation segment into the commodity marketplace.

Pentium Pro/6th generation competitors

*AMD K5

The K5 is AMD's first x86 processor to be developed entirely in-house. Introduced in March 1996, its primary competition was Intel's Pentium microprocessor. The K5 was an ambitious design, closer to a Pentium Pro than a Pentium regarding techn ...

and K6

* Cyrix 6x86

The Cyrix 6x86 is a line of sixth-generation, 32-bit x86 microprocessors designed and released by Cyrix in 1995. Cyrix, being a fabless company, had the chips manufactured by IBM and SGS-Thomson. The 6x86 was made as a direct competitor to In ...

and MII

A Mii ( ) is a customizable avatar used on several Nintendo video game consoles and mobile apps. Miis were first introduced on the Wii console in 2006 and later appeared on the 3DS, Wii U, the Switch, and various apps for smart devices. Miis c ...

* IDT WinChip

The WinChip series was a low-power Socket 7-based x86 processor designed by Centaur Technology and marketed by its parent company IDT.

Overview

Design

The design of the WinChip was quite different from other processors of the time. Instead o ...

* Intel P5 Pentium

Pentium is a brand used for a series of x86 architecture-compatible microprocessors produced by Intel. The original Pentium processor from which the brand took its name was first released on March 22, 1993. After that, the Pentium II and Pe ...

, co-existed with Pentium Pro for several years

See also

*List of Intel Pentium II microprocessors

The Pentium II is a sixth-generation CPU from Intel targeted at the consumer market.

Desktop processors "Klamath" (350 nm)

* All models support: MMX

* L2 cache is off-die and runs at 50% CPU speed

* Part numbers prefixed with a B are for bo ...

* List of Intel Pentium Pro microprocessors

References

External links

Backside Bus

searchstorage.techtarget.com

Intel Pentium Pro images and descriptions

cpu-collection.de

CPU-INFO: Intel Pentium Pro, indepth processor history

web.archive.org {{Intel processors, p6 Computer-related introductions in 1995 Intel x86 microprocessors Superscalar microprocessors 32-bit microprocessors