LPC Bus on:

[Wikipedia]

[Google]

[Amazon]

The Low Pin Count (LPC) bus is a

The Low Pin Count (LPC) bus is a

The LPC bus was introduced by

The LPC bus was introduced by

(Revision 6.0; September 1, 1995) One line is shared by all LPC devices and the host. Like the LAD lines, this has a weak pull-up which will maintain it high if no device is driving it. * CLKRUN# (open-collector): Signal used to restart the clock in systems that can stop it for power management. Not required if the host does not stop the clock. May be connected to the equivalent PCI signal. * LPME# (open-collector): Power management event, to wake the system from a sleep state. Equivalent to the PCI bus PME# signal. * LSMI# (open-collector): System management interrupt request. This is only required if an LPC device needs to trigger an SMI# in response to a bus access (e.g. to perform software emulation of a missing hardware peripheral). Otherwise, the slower SERIRQ protocol can be used to request an SMI. * LPCPD# (unidirectional, from host): Optional output from the host to warn the LPC device that power is about to be removed and it should not make any interrupt or DMA requests.

"Modding the XBox"

section "Details of the LPC".

Serialized IRQ Support For PCI Systems

used by the LPC bus

Open-Source LPC Host and Peripheral Cores

{{Computer-bus Computer-related introductions in 1998 Computer buses Computer hardware standards

The Low Pin Count (LPC) bus is a

The Low Pin Count (LPC) bus is a computer bus

In computer architecture, a bus (historically also called a data highway or databus) is a communication system that transfers data between components inside a computer or between computers. It encompasses both hardware (e.g., wires, optical ...

used on IBM-compatible personal computer

A personal computer, commonly referred to as PC or computer, is a computer designed for individual use. It is typically used for tasks such as Word processor, word processing, web browser, internet browsing, email, multimedia playback, and PC ...

s to connect low-bandwidth devices to the CPU

A central processing unit (CPU), also called a central processor, main processor, or just processor, is the primary processor in a given computer. Its electronic circuitry executes instructions of a computer program, such as arithmetic, log ...

, such as the BIOS

In computing, BIOS (, ; Basic Input/Output System, also known as the System BIOS, ROM BIOS, BIOS ROM or PC BIOS) is a type of firmware used to provide runtime services for operating systems and programs and to perform hardware initialization d ...

ROM (BIOS ROM was moved to the Serial Peripheral Interface

Serial Peripheral Interface (SPI) is a de facto standard (with many variants) for synchronous serial communication, used primarily in embedded systems for short-distance wired communication between integrated circuits.

SPI follows a master� ...

(SPI) bus in 2006), "legacy" I/O devices (integrated into Super I/O

Super I/O (sometimes Multi-IO) is a class of I/O controller integrated circuits that began to be used on personal computer motherboards in the late 1980s, originally as add-in cards, later embedded on the motherboards. A super I/O chip combine ...

, Embedded Controller

An Embedded Controller (EC) is a microcontroller in computers that handles various system tasks. Now it is usually merged with Super I/O, especially on mobile platforms (such as laptops).

Tasks

An embedded controller can have the following t ...

, CPLD

A complex programmable logic device (CPLD) is a programmable logic device with complexity between that of PALs and FPGAs, and architectural features of both. The main building block of the CPLD is a macrocell, which contains logic implementi ...

, and/or IPMI chip), and Trusted Platform Module

A Trusted Platform Module (TPM) is a secure cryptoprocessor that implements the ISO/IEC 11889 standard. Common uses are verifying that the boot process starts from a trusted combination of hardware and software and storing disk encryption keys.

...

(TPM). "Legacy" I/O devices usually include serial and parallel

Parallel may refer to:

Mathematics

* Parallel (geometry), two lines in the Euclidean plane which never intersect

* Parallel (operator), mathematical operation named after the composition of electrical resistance in parallel circuits

Science a ...

ports, PS/2 keyboard

Keyboard may refer to:

Text input

* Keyboard, part of a typewriter

* Computer keyboard

** Keyboard layout, the software control of computer keyboards and their mapping

** Keyboard technology, computer keyboard hardware and firmware

Music

* Mus ...

, PS/2 mouse

A mouse (: mice) is a small rodent. Characteristically, mice are known to have a pointed snout, small rounded ears, a body-length scaly tail, and a high breeding rate. The best known mouse species is the common house mouse (''Mus musculus'' ...

, and floppy disk controller

A floppy-disk controller (FDC) is a hardware component that directs and controls reading from and writing to a computer's floppy disk drive (FDD). It has evolved from a discrete set of components on one or more circuit boards to a special-purpo ...

.

Most PC motherboard

A motherboard, also called a mainboard, a system board, a logic board, and informally a mobo (see #Nomenclature, "Nomenclature" section), is the main printed circuit board (PCB) in general-purpose computers and other expandable systems. It ho ...

s with an LPC bus have either a Platform Controller Hub

The Platform Controller Hub (PCH) is a family of Intel's single-chip chipsets, first introduced in 2009. It is the successor to the Intel Hub Architecture, which used two chipsa northbridge and southbridge, and first appeared in the Intel 5 Se ...

(PCH) or a southbridge chip, which acts as the host and controls the LPC bus. All other devices connected to the physical wires of the LPC bus are peripherals.

Overview

Intel

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California, and Delaware General Corporation Law, incorporated in Delaware. Intel designs, manufactures, and sells computer compo ...

in 1998 as a software-compatible substitute for the Industry Standard Architecture

Industry Standard Architecture (ISA) is the 16-bit internal bus (computing), bus of IBM PC/AT and similar computers based on the Intel 80286 and its immediate successors during the 1980s. The bus was (largely) backward compatible with the 8-bi ...

(ISA) bus. It resembles ISA to software, although physically it is quite different. The ISA bus has a 16-bit

16-bit microcomputers are microcomputers that use 16-bit microprocessors.

A 16-bit register can store 216 different values. The range of integer values that can be stored in 16 bits depends on the integer representation used. With the two ...

data bus and a 24-bit address bus that can be used for both 16-bit I/O port addresses and 24-bit memory addresses; both run at speeds up to 8.33 MHz

The hertz (symbol: Hz) is the unit of frequency in the International System of Units (SI), often described as being equivalent to one event (or cycle) per second. The hertz is an SI derived unit whose formal expression in terms of SI base u ...

. The LPC bus uses a heavily multiplexed

In telecommunications and computer networking, multiplexing (sometimes contracted to muxing) is a method by which multiple analog or digital signals are combined into one signal over a shared medium. The aim is to share a scarce resource— ...

four-bit-wide bus operating at four times the clock speed (33.3 MHz) to transfer addresses and data with similar performance.

LPC's main advantage is that the basic bus requires only seven signals, greatly reducing the number of pins required on peripheral chips. An integrated circuit using LPC will need 30 to 72 fewer pins than its ISA equivalent. This also makes the bus easier to route on crowded modern motherboards. The clock rate was chosen to match that of PCI

PCI may refer to:

Business and economics

* Payment card industry, businesses associated with debit, credit, and other payment cards

** Payment Card Industry Data Security Standard, a set of security requirements for credit card processors

* Prov ...

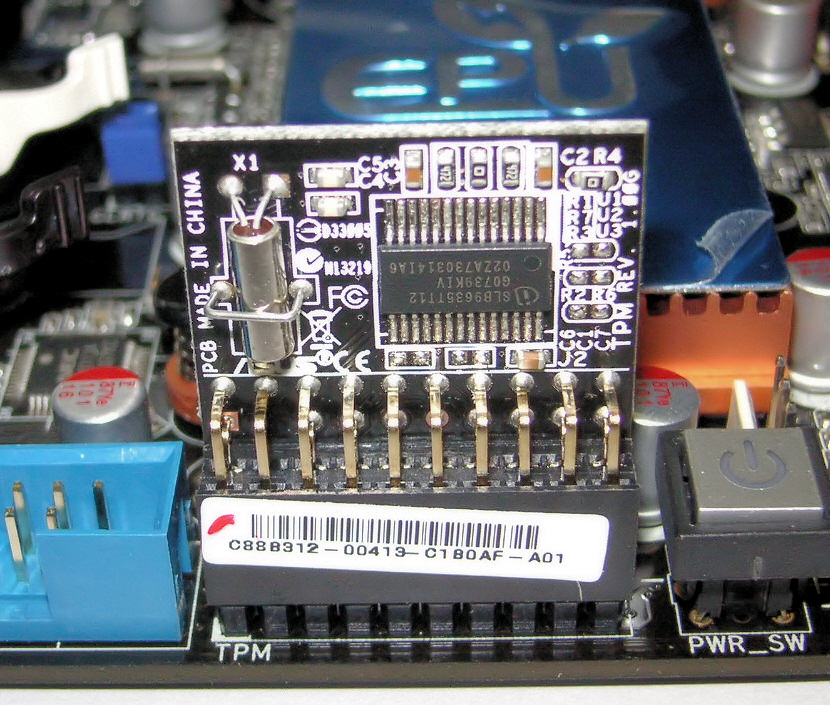

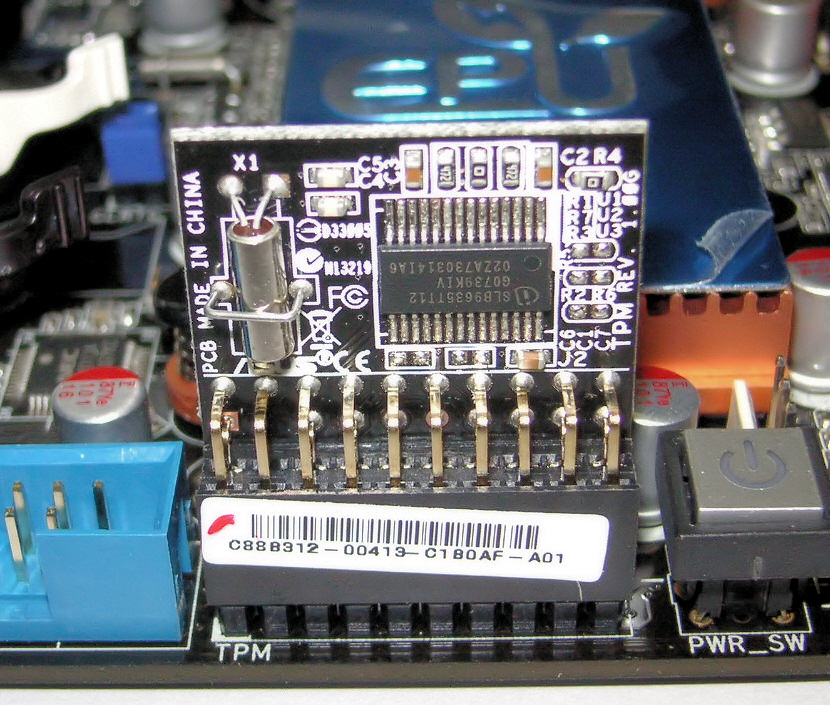

in order to further ease integration. Also, LPC is intended to be a motherboard-only bus; there is no standardized connector in common use, though Intel defines one for use for debug modules. A small number of LPC peripheral daughterboard

In computing, an expansion card (also called an expansion board, adapter card, peripheral card or accessory card) is a printed circuit board that can be inserted into an electrical connector, or expansion slot (also referred to as a bus sl ...

s are available, with pinouts proprietary to the motherboard vendor: Trusted Platform Modules (TPMs), POST card

In computing, a POST card is a plug-in diagnostic Expansion card, interface card that displays progress and error codes generated during power-on self-test (POST) of a computer. It is used to troubleshoot computers that do not Booting, start ...

s for displaying BIOS diagnostic codes, and ISA-compatible serial port

A serial port is a serial communication Interface (computing), interface through which information transfers in or out sequentially one bit at a time. This is in contrast to a parallel port, which communicates multiple bits simultaneously in Pa ...

peripherals for industrial use. Device discovery is not supported; since only motherboard devices or specific models of TPM are connected, the host firmware (BIOS, UEFI

Unified Extensible Firmware Interface (UEFI, as an acronym) is a Specification (technical standard), specification for the firmware Software architecture, architecture of a computing platform. When a computer booting, is powered on, the UEFI ...

) image will include a static description of any devices and their I/O addresses expected to be present on a particular motherboard.

Signals

LPC control signals areactive-low

In digital circuits, a logic level is one of a finite number of states that a digital signal can inhabit. Logic levels are usually represented by the voltage difference between the signal and ground, although other standards exist. The range of ...

, as indicated by the "#" symbol in their names. Signals are divided into three categories:

* Unidirectional. These are driven from a single source at all times.

* Open-collector

Open collector, open drain, open emitter, and open source refer to integrated circuit (IC) output pin configurations that process the IC's internal function through a transistor with an exposed terminal that is internally unconnected (i.e. "open ...

. These are low-speed signals which are pulled up (to the inactive state) by the host when not in use, and may be pulled down by any device.

* Bidirectional. These high-speed signals are actively driven high for one cycle whenever a device is done using them, after which weak pull-up resistor

In electronic logic circuits, a pull-up resistor (PU) or pull-down resistor (PD) is a resistor used to ensure a known state for a signal. More specifically, a pull-up resistor or pull-down resistor ensures that a wire will have a high logic lev ...

s hold them high until another device begins using them.

The LPC specification defines seven mandatory signals required for bidirectional data transfer:

* LCLK (unidirectional, from host): 33.3 MHz clock. May be connected to the conventional PCI

Peripheral Component Interconnect (PCI) is a local computer bus for attaching hardware devices in a computer and is part of the PCI Local Bus standard. The PCI bus supports the functions found on a processor bus but in a standardized format ...

clock (PCICLK), thereby not requiring a dedicated pin on the host (south bridge). Like PCI, other signals are driven after the falling edge of LCLK, and received after the rising edge.

* LRESET# (open-collector): Active-low bus reset. May be connected to PCIRST#.

* LFRAME# (unidirectional, from host): This active-low signal indicates the beginning of an LPC bus transaction. Only the host may initiate bus transactions.

* LAD :0'' (bidirectional): These four bidirectional signals carry multiplexed address, data, and other information.

There are six additional signals defined, which are optional for LPC devices that do not require their functionality, but support for the first two is mandatory for the host:

* LDRQ# (unidirectional, from device): DMA/bus master request. This is an output from a device that wants to perform direct memory access, either via the Intel 8237

Intel 8237 is a direct memory access (DMA) controller, a part of the MCS 85 microprocessor family. It enables data transfer between memory and the I/O with reduced load on the system's main processor by providing the memory with control signals ...

compatible DMA controller, or the LPC-specific bus master protocol. The host must provide one corresponding input pin per device that needs it (minimum two).

* SERIRQ (bidirectional): Serialized Intel 8259

The Intel 8259 is a programmable interrupt controller (PIC) designed for the Intel 8085 and Intel 8086, 8086 microprocessors. The initial part was 8259, a later A suffix version was upward compatible and usable with the 8086 or Intel 8088, 8088 ...

compatible interrupt signal.Serialized IRQ Support For PCI Systems(Revision 6.0; September 1, 1995) One line is shared by all LPC devices and the host. Like the LAD lines, this has a weak pull-up which will maintain it high if no device is driving it. * CLKRUN# (open-collector): Signal used to restart the clock in systems that can stop it for power management. Not required if the host does not stop the clock. May be connected to the equivalent PCI signal. * LPME# (open-collector): Power management event, to wake the system from a sleep state. Equivalent to the PCI bus PME# signal. * LSMI# (open-collector): System management interrupt request. This is only required if an LPC device needs to trigger an SMI# in response to a bus access (e.g. to perform software emulation of a missing hardware peripheral). Otherwise, the slower SERIRQ protocol can be used to request an SMI. * LPCPD# (unidirectional, from host): Optional output from the host to warn the LPC device that power is about to be removed and it should not make any interrupt or DMA requests.

Timing and performance

The LPC bus derives its electrical conventions from those ofconventional PCI

Peripheral Component Interconnect (PCI) is a local computer bus for attaching hardware devices in a computer and is part of the PCI Local Bus standard. The PCI bus supports the functions found on a processor bus but in a standardized format ...

. In particular, it shares the restriction that two idle cycles are required to "turn around" any bus signal so that a different device is "speaking". In the first, the bus is actively driven high. In the second, the bus is undriven and held high by the pull-up resistors. A new device may begin sending data over the bus on the third cycle. LPC operations spend a large fraction of their time performing such turn-arounds.

As mentioned, the LPC bus is designed to have performance similar to the ISA bus. The exact data transfer rates depend on the type of bus access (I/O, memory, DMA, firmware

In computing

Computing is any goal-oriented activity requiring, benefiting from, or creating computer, computing machinery. It includes the study and experimentation of algorithmic processes, and the development of both computer hardware, h ...

) performed and by the speed of the host and the LPC device. All bus cycles spend a majority of their time in overhead rather than data transfer—except the 16- and 128-byte firmware read cycles, which have 17 cycles of overhead but 32 and 256 cycles (respectively) of data transfer, achieving throughputs of and . The next fastest bus cycle defined in the standard, the 32-bit ISA-style DMA write cycle, spends only 8 of 20 total clock cycles transferring data (the other 12 cycles are overhead), achieving up to 6.67 MB/s.

One of the slowest bus cycles is a simple memory read or write, where only 2 of the 17 clock cycles (plus any wait states imposed by the device) transfer data, for a transfer rate of 1.96 MB/s.

Transaction structure

LPC transactions begin on a low-to-high transition of LFRAME#. While LFRAME# is low, the host places a 4-bit START code on the LAD lines. The code sent on the last cycle before LFRAME# transitions high defines the following bus transaction. Normally, the host only holds LFRAME# low for a single clock cycle, for efficiency. An exception is the abort transaction, which may begin even in the middle of another operation. The host pulls LFRAME# low for a minimum of four clock cycles, during which any devices must cease to drive the LAD bus. On the fourth cycle, the host drives LAD high (to 1111). Upon the high-to-low transition of LFRAME#, the bus is reset to an idle state. In almost all other cases, LPC transactions use the following general structure: * START code * Transaction type and address from host * Data from host (if a write) * Bus turnaround (2 cycles) * SYNC from device (1 or more cycles) * Data from device (if a read) * Bus turnaround (2 cycles) DMA transfers differ somewhat. may have multiple SYNC and data phases. § Bus master DMA has a bus turnaround immediately following the START code and no final turnaround, The SYNC phase allows the device to insertwait state

A wait state is a delay experienced by a computer processor when accessing external memory or another device that is slow to respond.

Computer microprocessors generally run much faster than the computer's other subsystems, which hold the data the ...

s in the transaction. There are six possible SYNC values, all with even parity (even Hamming weight

The Hamming weight of a string (computer science), string is the number of symbols that are different from the zero-symbol of the alphabet used. It is thus equivalent to the Hamming distance from the all-zero string of the same length. For the mo ...

). Three of them end the SYNC phase, while the other three cause the host to wait for another SYNC nibble:

* 0000: Ready. The device is ready to proceed with the transaction. For DMA cycles, this also clears the DMA request (DREQ) signal.

* 0011: ''(not used)''

* 0101: Short wait. Another SYNC cycle follows. At most 8 short wait cycles are permitted.

* 0110: Long wait. Like short wait, but the wait may be long (e.g. Enhanced Parallel Port

IEEE 1284, also known as the Centronics port, is a standard that defines bi-directional parallel communications between computers and other devices. It was originally developed in the 1970s by Centronics before its Institute of Electrical and ...

operations)

* 1001: Ready more. A DMA-only code that signals "Ready" ''and'' the device requests additional DMA cycles (DREQ remains asserted).

* 1010: Error. The device is ready to proceed, but there was some serious error (such as a parity error) with the transfer. This is equivalent to the ISA bus IOCHK# or PCI bus SERR# signals. In the case of a read, data follows but is likely to be corrupted.

* 1100: ''(not used)''

* 1111: Device not present. If no device responds to the transaction, the host will see this code and can abort the transaction. To accommodate slow devices, up to 2 cycles of this code are permitted before the transaction is aborted.

Applications

Intel designed the LPC bus so that the system BIOS image could be stored in a single flash memory chip directly connected to the LPC bus. Intel also made it possible to put operating system images and software applications on a single flash memory chip directly connected to the LPC bus, as an alternative to aParallel ATA

Parallel ATA (PATA), originally , also known as Integrated Drive Electronics (IDE), is a standard interface designed for IBM PC-compatible computers. It was first developed by Western Digital and Compaq in 1986 for compatible hard drives and C ...

port.

A CPLD

A complex programmable logic device (CPLD) is a programmable logic device with complexity between that of PALs and FPGAs, and architectural features of both. The main building block of the CPLD is a macrocell, which contains logic implementi ...

or FPGA

A field-programmable gate array (FPGA) is a type of configurable integrated circuit that can be repeatedly programmed after manufacturing. FPGAs are a subset of logic devices referred to as programmable logic devices (PLDs). They consist of a ...

can implement an LPC host or peripheral.

The original Xbox game console has an LPC debug port

A debug port is a diagnostic interface (akin to a computer port) included in an electronic system or integrated circuit to aid design, fabrication, development, bootstrapping, configuration, debugging, and post-sale in-system programming. In ge ...

that can be used to force the Xbox to boot new code.

O. Theis"Modding the XBox"

section "Details of the LPC".

ISA-compatible operation

All ISA-compatible LPC bus transactions use START code of 0000. During the first cycle with LFRAME# high again, the host drives a "cycle type/direction" (CTDIR) field: two bits indicating the type (I/O, memory, or DMA) and one bit indicating the direction (read from device, or write to device) of the transfer to follow. This is followed by the transfer address field, whose size depends on the type of cycle: * For I/O access, the address is 16 bits, transferred most-significant nibble first over 4 cycles. * For system memory access, the address is 32 bits, transferred most-significant nibble first over 8 cycles. * For ISA-compatible DMA accesses, there is no address ''per se'', but a two clock cycles transfer a nibble containing the DMA channel number, and a second nibble giving the transfer size. The memory address is programmed into the ISA-style DMA controller in the chipset or the CPU outside of the LPC bus. See below.ISA-compatible reads and writes

Memory and I/O accesses are allowed as single-byte accesses only, and operate as described in :: address, data from host if write, turnaround, SYNC, data from device if read. If the host attempts a transfer to an unused address, no device will drive the SYNC cycles and the host will see 1111 on the LAD bus. After seeing three cycles of 1111 (two cycles are allowed, in addition to the two turn-around cycles, for a slow device to decode the address and begin driving SYNC patterns), the host will abort the operation.ISA-compatible DMA

ThePlatform Controller Hub

The Platform Controller Hub (PCH) is a family of Intel's single-chip chipsets, first introduced in 2009. It is the successor to the Intel Hub Architecture, which used two chipsa northbridge and southbridge, and first appeared in the Intel 5 Se ...

(PCH) chip or the southbridge chip acts as the host and controls the LPC bus. It also acts as the central DMA controller for devices on that bus if the memory controller is in the chipset. In CPUs that contain their own memory controller(s), the DMA controller is located in the CPU. For compatibility with software originally written for systems with the ISA bus, the DMA controller contains the circuit equivalents of "legacy" onboard peripherals of the IBM PC/AT

The IBM Personal Computer AT (model 5170, abbreviated as IBM AT or PC/AT) was released in 1984 as the fourth model in the IBM Personal Computer line, following the IBM PC/XT and its IBM Portable PC variant. It was designed around the Intel 8028 ...

architecture, such as the two programmable interrupt controllers, the programmable interval timer

In computing and in embedded systems, a programmable interval timer (PIT) is a counter that generates an output signal when it reaches a programmed count. The output signal may trigger an interrupt.

Common features

PITs may be one-shot or periodi ...

, and two ISA DMA controllers, which are all involved in " ISA-style DMA".

ISA-compatible DMA uses an Intel 8237-compatible DMA controller on the host, which keeps track of the location and length of the memory buffer, as well as the direction of the transfer. The device simply requests service from a given DMA channel number, and the host performs a DMA access on the LPC bus.

The request is made by a virtual ISA-compatible DMA request (DRQ) line, which is emulated using the device's LDRQ# signal to indicate transitions on the emulated DRQ line. This is done with 6-bit requests on the LDRQ# signal: a 0 start bit, the 3-bit DMA channel number (most significant bit first), one bit of new request level (almost always 1, indicating that a DMA transfer is requested), and a final 1 stop bit. The host responds by performing a DMA cycle at the next available opportunity. DMA cycles are named based on the direction of ''memory'' access, so a "read" is a transfer ''to'' the LPC device, and a "write" is a transfer ''from'' the LPC device.

The "address" consists of 6 bits sent as two nibbles: a 3-bit channel number and 1-bit terminal count indication (the ISA bus's TC pin, or the 8237's EOP# output), followed by a 2-bit transfer size.

By default, DMA channels 0–3 perform 8-bit transfers, and channels 5–7 perform 16-bit transfers; but an LPC-specific extension allows 1-, 2-, or 4-byte transfers on any channel. When a multi-byte transfer is performed, each byte has its own SYNC field, as described below.

A normal SYNC "ready" pattern of 0000 (or an error pattern of 1010) also causes a deassertion of the corresponding emulated DMA request signal; the host will stop DMA after the immediately following byte until the device makes another DMA request via the LDRQ# signal. A SYNC pattern of 1001 indicates that the host should consider he device's DMA request still active; the host will continue with any remaining bytes in this transfer or start another transfer, as appropriate, without a separate request via LDRQ#.

For a DMA write, where data is transferred from the device, the SYNC field is followed by the 8 bits of data and another SYNC field, until the host-specified length for this transfer is reached, or the device stops the transfer. A two-cycle turnaround field completes the transaction. For a DMA read, where data is transferred to the device, the SYNC field is followed by a turnaround, and the data—turnaround—sync—turnaround sequence repeats for each byte transferred.

Serialized interrupts

Interrupts are transmitted over a single shared SERIRQ line using the "serialized interrupts for PCI" protocol originally developed for the PCI bus. The host periodically sends interrupt packets, within which each interrupt request is assigned a 1-clock time slot, separated by 2-clock turnaround cycles. The initial synchronization is done by the host. As a simplified example: * The host drives the SERIRQ line low for four to eight clocks, followed by a 2-clock turnaround cycle: SERIRQ is driven high for 1 clock, then floats high for the second turnaround clock. * If a device needs to request IRQ#6, it waits for 6×3=18 clocks, then drives SERIRQ low for one clock and high for another. The devices can recognize the beginning of the frame because only the host will ever drive the line low for more than one cycle. The host identifies the interrupt by counting the number of clocks cycles: if it sees the SERIRQ line driven low at the eighteenth clock, then IRQ 18/3=6 is asserted. The number of interrupt slots is system-specific, with 17 being a typical number: 16 ISA-compatible interrupts (IRQ0–IRQ15), plus NMI. After the final interrupt slot, the host appends a "stop" signal consisting of two or three low cycles followed by two turnaround cycles. In "continuous" mode, the host periodically initiates a new packet. There is also a "quiet" mode in which a device requests a new packet by driving SERIRQ low for one clock cycle. The host then continues driving the line low for the other seven clocks. From this point on, the protocol is the same. The mode is controlled by the length of the host's stop signal at the end of each packet. If it consists of three clocks of low signal, continuous mode follows and only the host may begin a new packet. If the stop signal consists of two low clocks, quiet mode follows and any device may initiate an interrupt packet.LPC non-ISA transactions

START field values other than 0000 or 1111 are used to indicate various non-ISA-compatible transfers. The supported transfers are:START = 1101, 1110: Firmware memory read and write

This allows the firmware (BIOS) to be located outside the usual peripheral address space. These transfers are similar to ISA-compatible transfers, except that: * There is no CTDIR field; the direction is encoded in the START field (1101 for read, 1110 for write). * The first 4 address bits are defined as a device select (IDSEL) field to allow the selection of one firmware hub out of many. For example, a second firmware hub can be used to hold a backup BIOS in case the primary BIOS is corrupted by malware or a bad flash. * The remaining 28 address bits define the address within the device, most significant nibble first. * The address is followed by a size field. Supported read/write sizes are 1, 2, and 4 bytes. Sizes of 16 and 128 bytes are supported for read only. * The data is transferred in one continuous burst, with no wait states. There is only one SYNC field for the whole transfer.START = 0010, 0011: Bus master DMA

Up to two devices on an LPC bus can request a bus master transfer by using the LDRQ# signal to request use of the reserved DMA channel 4. In this case, the host will begin a transfer with a special START field of 0010 for bus master 0 or 0011 for bus master 1, followed immediately by two turnaround cycles to hand the bus to the device requesting the bus master DMA cycle. Following the turnaround cycles, the transfer proceeds very much like a host-initiated ISA-compatible transfer with the roles reversed: * The device sends a one-cycle CTDIR field (only I/O and memory transfer types are permitted). * The device sends an address (16 or 32 bits, depending on the type). It is transferred most significant nibble first. * The device sends a one-cycle transfer size field, encoding 8, 16 or 32 bits. * In the case of a write, the data follows. Unlike ISA-compatible DMA cycles, the data is transferred in one burst, with no more wait states. * Then come two turn-around cycles while the LAD bus is handed back to the host. * A variable-length SYNC field is inserted, under control of the host. * In the case of a read, the data provided by the host follows. This differs from 16-bit ISA bus mastering because LPC bus mastering requires a 32-bit memory address when performing a memory transfer, does not use an ISA-style DMA channel, and can support 8, 16, or 32-bit transfers; while 16-bit ISA bus mastering requires a 24-bit memory address when performing a memory transfer, requires the use of an ISA-style DMA channel, and cannot perform 32-bit transfers.START = 0101: TPM Locality access

Trusted Platform Module 2.0 specifications define special TPM-Read cycles and TPM-Write cycles that are based on the I/O Read and the I/O Write cycles.. These cycles use a START field with the formerly-reserved value of 0101, followed by a CTDIR nibble and 16-bit I/O address just like an ISA-compatible write. These cycles are used when using a TPM's locality facility.Supported peripherals

The LPC bus specification limits what type of peripherals may be connected to it. It only allows devices that belong to the following classes of devices: super I/O devices,nonvolatile BIOS memory

Nonvolatile BIOS memory refers to a small Memory (computers), memory on personal computer, PC motherboards that is used to store BIOS settings. It is traditionally called CMOS RAM because it uses a volatile memory, volatile, low-power CMOS, co ...

, firmware hubs, audio devices, and embedded controllers. Furthermore, each class is restricted on which bus cycles are allowed for each class.

Super I/O devices and audio devices are allowed to accept I/O cycles, accept ISA-style third-party DMA cycles, and generate bus master cycles. Generic-application memory devices like nonvolatile BIOS memory

Nonvolatile BIOS memory refers to a small Memory (computers), memory on personal computer, PC motherboards that is used to store BIOS settings. It is traditionally called CMOS RAM because it uses a volatile memory, volatile, low-power CMOS, co ...

and LPC flash devices are allowed to accept memory cycles. Firmware hubs are allowed to accept firmware memory cycles. Embedded controllers are allowed to accept I/O cycles and generate bus master cycles. Some ISA cycles that were deemed not useful to these classes were removed. They include host-initiated two-byte memory cycles and host-initiated two-byte I/O cycles. These removed transfer types could be initiated by the host on ISA buses but not on LPC buses. The host would have to simulate two-byte cycles by splitting them up into two one-byte cycles. The ISA bus has a similar concept because the original 8-bit ISA bus required 16-bit cycles to be split up. Therefore, the 16-bit ISA bus automatically split 16-bit cycles into 8-bit cycles for the benefit of 8-bit ISA peripherals unless the ISA device being targeted by a 16-bit memory or I/O cycle asserted a signal that told the bus that it could accept the requested 16-bit transfer without assistance from an ISA cycle splitter. ISA-style bus mastering has been replaced in the LPC bus with a bus mastering protocol that does not rely on the ISA-style DMA controllers at all. This was done in order to remove ISA's limit on what type of bus master cycles a device is allowed to initiate on which DMA channel. The ISA-style bus cycles that were inherited by LPC from ISA are one-byte host-initiated I/O bus cycles, one-byte host-initiated memory cycles, and one- or two-byte host-initiated ISA-style DMA cycles.

However, some non-ISA bus cycles were added. Cycles that were added to improve the performance of devices beside firmware hubs include LPC-style one-, two-, and four-byte bus master memory cycles; one-, two-, and four-byte bus master I/O cycles; and 32-bit third-party DMA which conforms to all of the restrictions of ISA-style third-party DMA except for the fact that it can do 32-bit transfers. Any device that is allowed to accept traditional ISA-style DMA is also allowed to use this 32-bit ISA-style DMA. The host could initiate 32-bit ISA-style DMA cycles, while peripherals could initiate bus master cycles. Firmware hubs consumed firmware cycles that were designed just for firmware hubs so that firmware addresses and normal memory-mapped I/O addresses could overlap without conflict. Firmware memory reads could read 1, 2, 4, 16, or 128 bytes at once. Firmware memory writes could write one, two or four bytes at once.

The LPC bus does not support ISA expansion cards.

See also

*List of interface bit rates

A list is a set of discrete items of information collected and set forth in some format for utility, entertainment, or other purposes. A list may be memorialized in any number of ways, including existing only in the mind of the list-maker, but ...

* Legacy Plug and Play

* Option ROM

* Serial Peripheral Interface

Serial Peripheral Interface (SPI) is a de facto standard (with many variants) for synchronous serial communication, used primarily in embedded systems for short-distance wired communication between integrated circuits.

SPI follows a master� ...

* (eSPI), the successor of the LPC bus.

References

External links

Serialized IRQ Support For PCI Systems

used by the LPC bus

Open-Source LPC Host and Peripheral Cores

{{Computer-bus Computer-related introductions in 1998 Computer buses Computer hardware standards