Kendall Square Research on:

[Wikipedia]

[Google]

[Amazon]

Kendall Square Research (KSR) was a

"BUSINESS TECHNOLOGY; Pools of Memory, Waves of Dispute" John Markoff, The New York Times - 29 January 1992

1986 establishments in Massachusetts 1994 disestablishments in Massachusetts American companies established in 1986 American companies disestablished in 1994 Computer companies established in 1986 Computer companies disestablished in 1994 Companies based in Cambridge, Massachusetts Defunct computer companies based in Massachusetts Defunct computer companies of the United States Defunct computer hardware companies Supercomputers

supercomputer

A supercomputer is a computer with a high level of performance as compared to a general-purpose computer. The performance of a supercomputer is commonly measured in floating-point operations per second ( FLOPS) instead of million instructions ...

company headquartered originally in Kendall Square

Kendall Square is a neighborhood in Cambridge, Massachusetts. The square itself at the intersection of Main Street and Broadway. It also refers to the broad business district east of Portland Street, northwest of the Charles River, north of MIT ...

in Cambridge, Massachusetts

Cambridge ( ) is a city in Middlesex County, Massachusetts, United States. As part of the Boston metropolitan area, the cities population of the 2020 U.S. census was 118,403, making it the fourth most populous city in the state, behind Boston, ...

in 1986, near Massachusetts Institute of Technology

The Massachusetts Institute of Technology (MIT) is a private land-grant research university in Cambridge, Massachusetts. Established in 1861, MIT has played a key role in the development of modern technology and science, and is one of the ...

(MIT). It was co-founded by Steven Frank and Henry Burkhardt III, who had formerly helped found Data General

Data General Corporation was one of the first minicomputer firms of the late 1960s. Three of the four founders were former employees of Digital Equipment Corporation (DEC).

Their first product, 1969's Data General Nova, was a 16-bit minicomputer ...

and Encore Computer

Encore Computer was an early pioneer in the parallel computing market, based in Marlborough, Massachusetts. Although offering several system designs beginning in 1985, they were never as well known as other companies in this field such as Pyrami ...

and was one of the original team that designed the PDP-8

The PDP-8 is a 12-bit computing, 12-bit minicomputer that was produced by Digital Equipment Corporation, Digital Equipment Corporation (DEC). It was the first commercially successful minicomputer, with over 50,000 units being sold over the model's ...

. KSR produced two models of supercomputer, the KSR1 and KSR2. It went bankrupt in 1994.

Technology

The KSR systems ran a specially customized version of theOSF/1

OSF/1 is a variant of the Unix operating system developed by the Open Software Foundation during the late 1980s and early 1990s. OSF/1 is one of the first operating systems to have used the Mach kernel developed at Carnegie Mellon University, and ...

operating system

An operating system (OS) is system software that manages computer hardware, software resources, and provides common services for computer programs.

Time-sharing operating systems schedule tasks for efficient use of the system and may also in ...

, a Unix

Unix (; trademarked as UNIX) is a family of multitasking, multiuser computer operating systems that derive from the original AT&T Unix, whose development started in 1969 at the Bell Labs research center by Ken Thompson, Dennis Ritchie, and ot ...

variant, with programs compiled by a KSR-specific port of the Green Hills Software

Green Hills Software is a privately owned company that builds operating systems and programming tools for embedded systems. The firm was founded in 1982 by Dan O'Dowd and Carl Rosenberg. Its world headquarters are in Santa Barbara, California.

...

C and FORTRAN compilers. The architecture

Architecture is the art and technique of designing and building, as distinguished from the skills associated with construction. It is both the process and the product of sketching, conceiving, planning, designing, and constructing building ...

was shared memory

In computer science, shared memory is memory that may be simultaneously accessed by multiple programs with an intent to provide communication among them or avoid redundant copies. Shared memory is an efficient means of passing data between progr ...

implemented as a cache-only memory architecture

Cache only memory architecture (COMA) is a computer memory organization for use in multiprocessors in which the local memories (typically DRAM) at each node are used as cache. This is in contrast to using the local memories as actual main memory, ...

or "COMA". Being all cache, memory dynamically migrated and replicated in a coherent manner based on the access pattern of individual processors. The processors were arranged in a hierarchy of rings, and the operating system mediated process migration and device access. Instruction decode was hardwired, and pipelining was used. Each KSR1 processor was a custom 64-bit

In computer architecture, 64-bit Integer (computer science), integers, memory addresses, or other Data (computing), data units are those that are 64 bits wide. Also, 64-bit central processing unit, CPUs and arithmetic logic unit, ALUs are those ...

reduced instruction set computing

In computer engineering, a reduced instruction set computer (RISC) is a computer designed to simplify the individual instructions given to the computer to accomplish tasks. Compared to the instructions given to a complex instruction set comput ...

(RISC) CPU clocked at 20 MHz and capable of a peak output of 20 million instructions per second

Instructions per second (IPS) is a measure of a computer's processor speed. For complex instruction set computers (CISCs), different instructions take different amounts of time, so the value measured depends on the instruction mix; even for compa ...

(MIPS) and 40 million floating-point operations per second (MFLOPS

In computing, floating point operations per second (FLOPS, flops or flop/s) is a measure of computer performance, useful in fields of scientific computations that require floating-point calculations. For such cases, it is a more accurate meas ...

). Up to 1088 of these processors could be arranged in a single system, with a minimum of eight. The KSR2 doubled the clock rate to 40 MHz and supported over 5000 processors. The KSR-1 chipset was fabricated by Sharp Corporation

is a Japanese multinational corporation that designs and manufactures electronic products, headquartered in Sakai-ku, Sakai, Osaka Prefecture. Since 2016 it has been majority owned by the Taiwan-based Foxconn Group. Sharp employs more than 5 ...

while the KSR-2 chipset was built by Hewlett-Packard

The Hewlett-Packard Company, commonly shortened to Hewlett-Packard ( ) or HP, was an American multinational information technology company headquartered in Palo Alto, California. HP developed and provided a wide variety of hardware components ...

.

Software

Besides the traditional scientific applications, KSR withOracle Corporation

Oracle Corporation is an American multinational computer technology corporation headquartered in Austin, Texas. In 2020, Oracle was the third-largest software company in the world by revenue and market capitalization. The company sells da ...

, addressed the massively parallel database market for commercial applications. The KSR-1 and -2 supported Micro Focus COBOL

COBOL (; an acronym for "common business-oriented language") is a compiled English-like computer programming language designed for business use. It is an imperative, procedural and, since 2002, object-oriented language. COBOL is primarily us ...

and C/C++

C++ (pronounced "C plus plus") is a high-level general-purpose programming language created by Danish computer scientist Bjarne Stroustrup as an extension of the C programming language, or "C with Classes". The language has expanded significan ...

programming languages, and the Oracle database

Oracle Database (commonly referred to as Oracle DBMS, Oracle Autonomous Database, or simply as Oracle) is a multi-model database management system produced and marketed by Oracle Corporation.

It is a database commonly used for running online t ...

and the MATISSE OODBMS

An object database or object-oriented database is a database management system in which information is represented in the form of objects as used in object-oriented programming. Object databases are different from relational databases which are ...

from ADB, Inc. Their own product, the KSR Query Decomposer, complemented the functions of the Oracle product for SQL uses. The TUXEDO transaction monitor for OLTP was also provided. The KAP program (Kuck & Associate Preprocessor) provided for pre-processing for source code

In computing, source code, or simply code, is any collection of code, with or without comments, written using a human-readable programming language, usually as plain text. The source code of a program is specially designed to facilitate the wo ...

analysis

Analysis ( : analyses) is the process of breaking a complex topic or substance into smaller parts in order to gain a better understanding of it. The technique has been applied in the study of mathematics and logic since before Aristotle (38 ...

and parallelization

Parallel computing is a type of computation in which many calculations or processes are carried out simultaneously. Large problems can often be divided into smaller ones, which can then be solved at the same time. There are several different fo ...

. The runtime environment was termed PRESTO, and was a POSIX

The Portable Operating System Interface (POSIX) is a family of standards specified by the IEEE Computer Society for maintaining compatibility between operating systems. POSIX defines both the system- and user-level application programming interf ...

compliant multithreading manager.

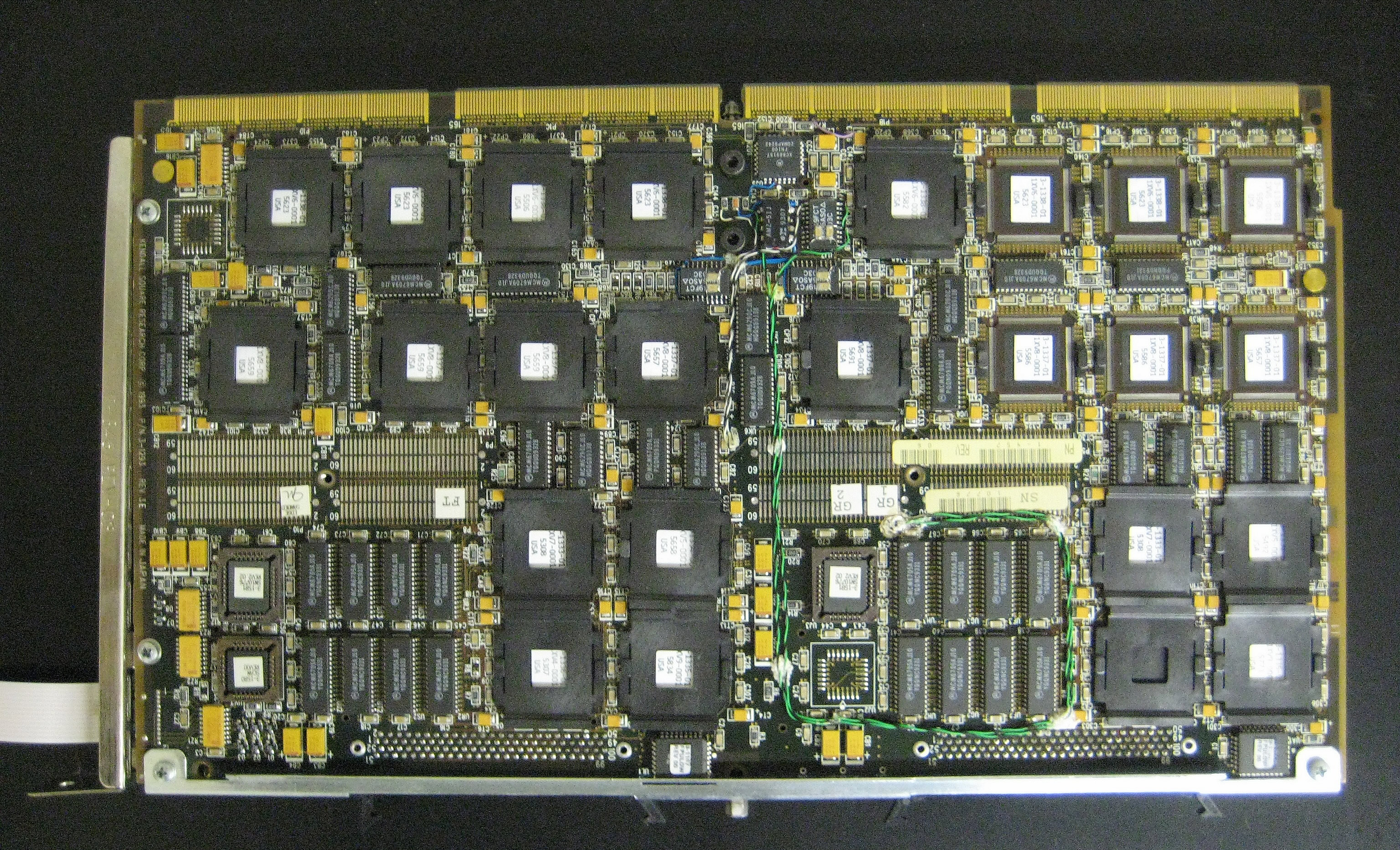

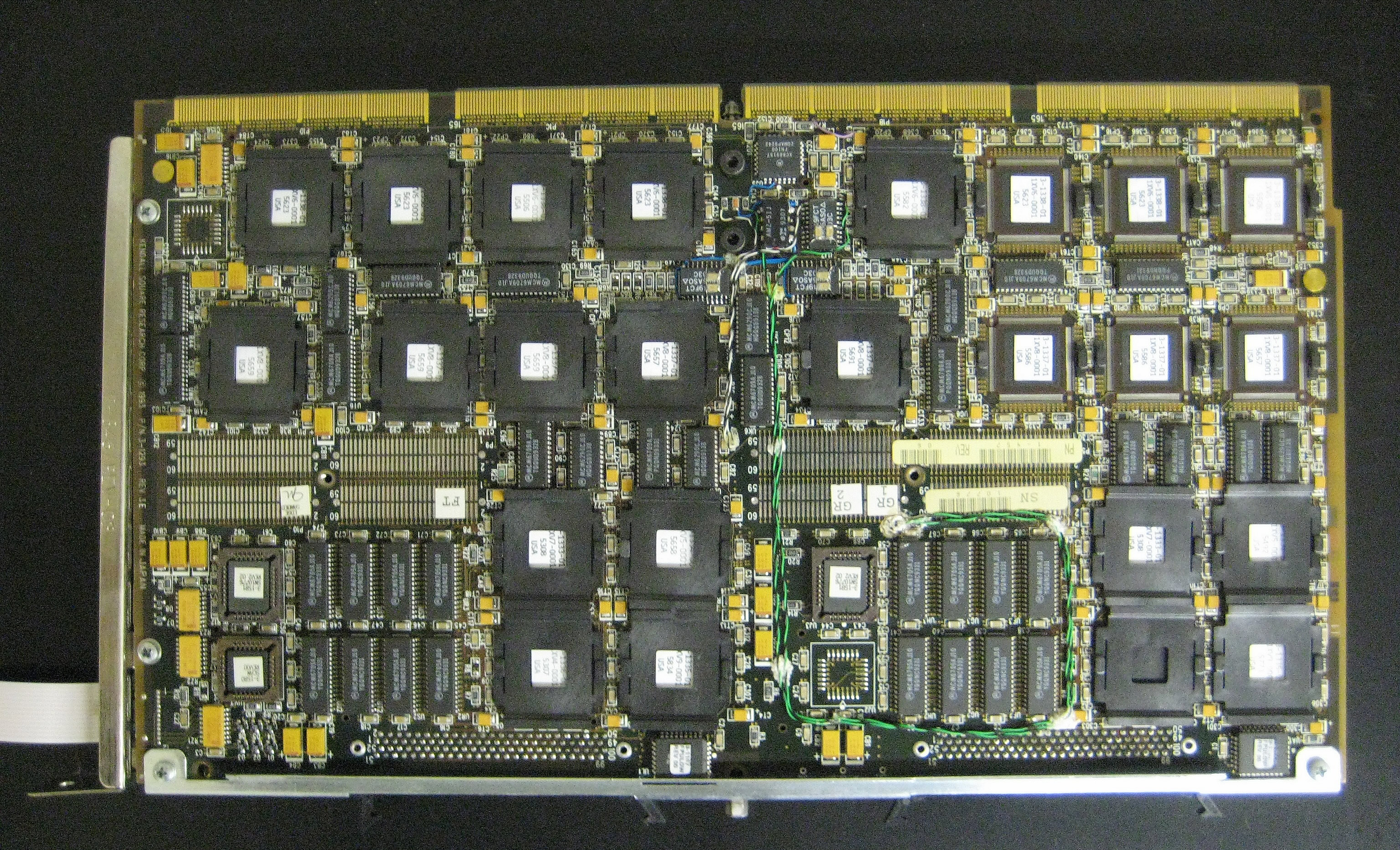

Hardware

The KSR-1 processor was implemented as a four-chip set in 1.2 micrometer complementary metal–oxide–semiconductor (CMOS

Complementary metal–oxide–semiconductor (CMOS, pronounced "sea-moss", ) is a type of metal–oxide–semiconductor field-effect transistor (MOSFET) fabrication process that uses complementary and symmetrical pairs of p-type and n-type MOSFE ...

). These chips were: the cell execution unit, the floating point unit

Floating may refer to:

* a type of dental work performed on horse teeth

* use of an isolation tank

* the guitar-playing technique where chords are sustained rather than scratched

* ''Floating'' (play), by Hugh Hughes

* Floating (psychological phe ...

, the arithmetic logic unit

In computing, an arithmetic logic unit (ALU) is a Combinational logic, combinational digital circuit that performs arithmetic and bitwise operations on integer binary numbers. This is in contrast to a floating-point unit (FPU), which operates on ...

, and the external I/O unit (XIO). The CEU handled instruction fetch (two per clock), and all operations involving memory, such as loads and stores. 40-bit addresses were used, going to full 64-bit addresses later. The integer unit had 32, 64-bit-wide registers. The floating point

In computing, floating-point arithmetic (FP) is arithmetic that represents real numbers approximately, using an integer with a fixed precision, called the significand, scaled by an integer exponent of a fixed base. For example, 12.345 can be ...

unit is discussed below. The XIO had the capacity of 30 MB/s throughput to I/O devices. It included 64 control and data registers.

The KSR processor was a 2-wide VLIW, with instructions of 6 types: memory reference (load and store), execute, control flow, memory control, I/O, and inserted. Execute instructions included arithmetic, logical, and type conversion. They were usually triadic register

Register or registration may refer to:

Arts entertainment, and media Music

* Register (music), the relative "height" or range of a note, melody, part, instrument, etc.

* ''Register'', a 2017 album by Travis Miller

* Registration (organ), th ...

in format. Control flow refers to branches and jumps. Branch instructions

Instruction or instructions may refer to:

Computing

* Instruction, one operation of a processor within a computer architecture instruction set

* Computer program, a collection of instructions

Music

* Instruction (band), a 2002 rock band from Ne ...

were two cycles. The programmer (or compiler) could implicitly control the ''quashing'' behavior of the subsequent two instructions that would be initiated during the branch. The choices were: always retain the results, retain results if branch test is true, or retain results if branch test is false. Memory control provided synchronization primitives. I/O instructions were provided. Inserted instructions were forced into a flow by a coprocessor

A coprocessor is a computer processor used to supplement the functions of the primary processor (the CPU). Operations performed by the coprocessor may be floating-point arithmetic, graphics, signal processing, string processing, cryptography o ...

. Inserted load and store were used for direct memory access

Direct memory access (DMA) is a feature of computer systems and allows certain hardware subsystems to access main system memory independently of the central processing unit (CPU).

Without DMA, when the CPU is using programmed input/output, it is t ...

(DMA) transfers. Inserted memory instructions were used to maintain cache coherency. New coprocessors could be interfaced with the inserted instruction mechanism. IEEE standard floating point arithmetic was supported. Sixty-four 64-bit wide registers were included.

The following example of KSR assembly performs an indirect procedure call to an address held in the procedure's constant block, saving the return address in register c14. It also saves the frame pointer, loads integer register zero with the value 3, and increments integer register 31 without changing the condition codes. Most instructions have a delay slot

In computer architecture, a delay slot is an instruction slot being executed without the effects of a preceding instruction. The most common form is a single arbitrary instruction located immediately after a branch instruction on a RISC or DSP ar ...

of 2 cycles and the delay slots are not interlock

An interlock is a feature that makes the state of two mechanisms or functions mutually dependent. It may be used to prevent undesired states in a finite-state machine, and may consist of any electrical, electronic, or mechanical devices or system ...

ed, so must be scheduled explicitly, else the resulting hazard

A hazard is a potential source of harm

Harm is a moral and legal concept.

Bernard Gert construes harm as any of the following:

* pain

* death

* disability

* mortality

* loss of abil ity or freedom

* loss of pleasure.

Joel Feinberg giv ...

means wrong values are sometimes loaded.

finop ; movb8_8 %i2,%c10 finop ; cxnop finop ; cxnop add8.ntr 75,%i31,%i31 ; ld8 8(%c10),%c4 finop ; st8 %fp,504(%sp) finop ; cxnop movi8 3, %i0 ; jsr %c14,16(%c4)In the KSR design, all of the memory was treated as cache. The design called for no ''home'' location- to reduce storage overheads and to software transparently, dynamically migrate/replicate memory based on where it was be utilized; A

Harvard architecture

The Harvard architecture is a computer architecture with separate storage and signal pathways for instructions and data. It contrasts with the von Neumann architecture, where program instructions and data share the same memory and pathways.

...

, separate bus

A bus (contracted from omnibus, with variants multibus, motorbus, autobus, etc.) is a road vehicle that carries significantly more passengers than an average car or van. It is most commonly used in public transport, but is also in use for cha ...

for instructions and memory was used. Each node board contained 256 KB of I-cache and D-cache, essentially primary cache. At each node was 32 MB of memory for main cache. The system level architecture was shared virtual memory, which was physically distributed in the machine. The programmer or application only saw one contiguous address space, which was spanned by a 40-bit address. Traffic between nodes traveled at up to 4 gigabytes per second. The 32 megabytes per node, in aggregate, formed the physical memory of the machine.

Specialized input/output

In computing, input/output (I/O, or informally io or IO) is the communication between an information processing system, such as a computer, and the outside world, possibly a human or another information processing system. Inputs are the signals ...

processors could be used in the system, providing scalable I/O. A 1088 node KSR1 could have 510 I/O channels with an aggregate in excess of 15 GB/s. Interfaces such as Ethernet

Ethernet () is a family of wired computer networking technologies commonly used in local area networks (LAN), metropolitan area networks (MAN) and wide area networks (WAN). It was commercially introduced in 1980 and first standardized in 198 ...

, FDDI

Fiber Distributed Data Interface (FDDI) is a standard for data transmission in a local area network.

It uses optical fiber as its standard underlying physical medium, although it was also later specified to use copper cable, in which case it m ...

, and HIPPI were supported.

History

As the company scaled up quickly to enter production, they moved in the late 1980s to 170 Tracer Lane,Waltham, Massachusetts

Waltham ( ) is a city in Middlesex County, Massachusetts, United States, and was an early center for the labor movement as well as a major contributor to the American Industrial Revolution. The original home of the Boston Manufacturing Company, th ...

.

KSR refocused its efforts from the scientific to the commercial marketplace, with emphasis on parallel relational databases and OLTP operations. It then got out of the hardware business, but continued to market some of its data warehousing and analysis software products.

The first KSR1 system was installed in 1991. With new processor hardware, new memory hardware and a novel memory architecture, a new compiler port, a new port of a relatively new operating system, and exposed memory hazards, early systems were noted for frequent system crashes. KSR called their cache-only memory architecture

Cache only memory architecture (COMA) is a computer memory organization for use in multiprocessors in which the local memories (typically DRAM) at each node are used as cache. This is in contrast to using the local memories as actual main memory, ...

(COMA) by the trade name ''Allcache''; reliability problems with early systems earned it the nickname ''Allcrash'', although memory was not necessarily the root cause of crashes. A few KSR1 models were sold, and as the KSR2 was being rolled out, the company collapsed amid accounting irregularities involving the overstatement of revenue.

KSR used a proprietary processor because 64-bit processors were not commercially available. However, this put the small company in the difficult position of doing both processor design and system design. The KSR processors were introduced in 1991 at 20 MHz and 40 MFlops. At that time, the 32-bit Intel 80486

The Intel 486, officially named i486 and also known as 80486, is a microprocessor. It is a higher-performance follow-up to the Intel 386. The i486 was introduced in 1989. It represents the fourth generation of binary compatible CPUs following the ...

ran at 50 MHz and 50 MFlops. When the 64-bit DEC Alpha

Alpha (original name Alpha AXP) is a 64-bit reduced instruction set computer (RISC) instruction set architecture (ISA) developed by Digital Equipment Corporation (DEC). Alpha was designed to replace 32-bit VAX complex instruction set computers ...

was introduced in 1992, it ran at up to 192 MHz and 192 MFlops, while the 1992 KSR2 ran at 40 MHz and 80 MFlops.

One customer of the KSR2, the Pacific Northwest National Laboratory

Pacific Northwest National Laboratory (PNNL) is one of the United States Department of Energy national laboratories, managed by the Department of Energy's (DOE) Office of Science. The main campus of the laboratory is in Richland, Washington.

O ...

, a United States Department of Energy

The United States Department of Energy (DOE) is an executive department of the U.S. federal government that oversees U.S. national energy policy and manages the research and development of nuclear power and nuclear weapons in the United Stat ...

facility, purchased an enormous number of spare parts, and kept their machines running for years after the demise of KSR.

KSR, along with many of its competitors (see below), went bankrupt during the collapse of the supercomputer market in the early 1990s. KSR went out of business in February 1994, when their stock was delisted from the stock exchange.

Competition

KSR's competitors included MasPar Computer Corporation,Thinking Machines

Thinking Machines Corporation was a supercomputer manufacturer and artificial intelligence (AI) company, founded in Waltham, Massachusetts, in 1983 by Sheryl Handler and W. Daniel "Danny" Hillis to turn Hillis's doctoral work at the Massachuset ...

, Meiko Scientific

Meiko Scientific Ltd. was a British supercomputer company based in Bristol, founded by members of the design team working on the Inmos transputer microprocessor.

History

In 1985, when Inmos management suggested the release of the transputer b ...

, and various old-line (and still surviving) companies like IBM and Intel

Intel Corporation is an American multinational corporation and technology company headquartered in Santa Clara, California. It is the world's largest semiconductor chip manufacturer by revenue, and is one of the developers of the x86 seri ...

.

References

{{ReflistFurther reading

"BUSINESS TECHNOLOGY; Pools of Memory, Waves of Dispute" John Markoff, The New York Times - 29 January 1992

1986 establishments in Massachusetts 1994 disestablishments in Massachusetts American companies established in 1986 American companies disestablished in 1994 Computer companies established in 1986 Computer companies disestablished in 1994 Companies based in Cambridge, Massachusetts Defunct computer companies based in Massachusetts Defunct computer companies of the United States Defunct computer hardware companies Supercomputers