The Grain 128a

stream cipher was first purposed at Symmetric Key Encryption Workshop (SKEW) in 2011

as an improvement of the predecessor Grain 128, which added security enhancements and optional message authentication using the Encrypt & MAC approach. One of the important features of the

Grain family is that the throughput can be increased at the expense of additional hardware. Grain 128a is designed by Martin Ågren,

Martin Hell, Thomas Johansson and Willi Meier.

Description of the cipher

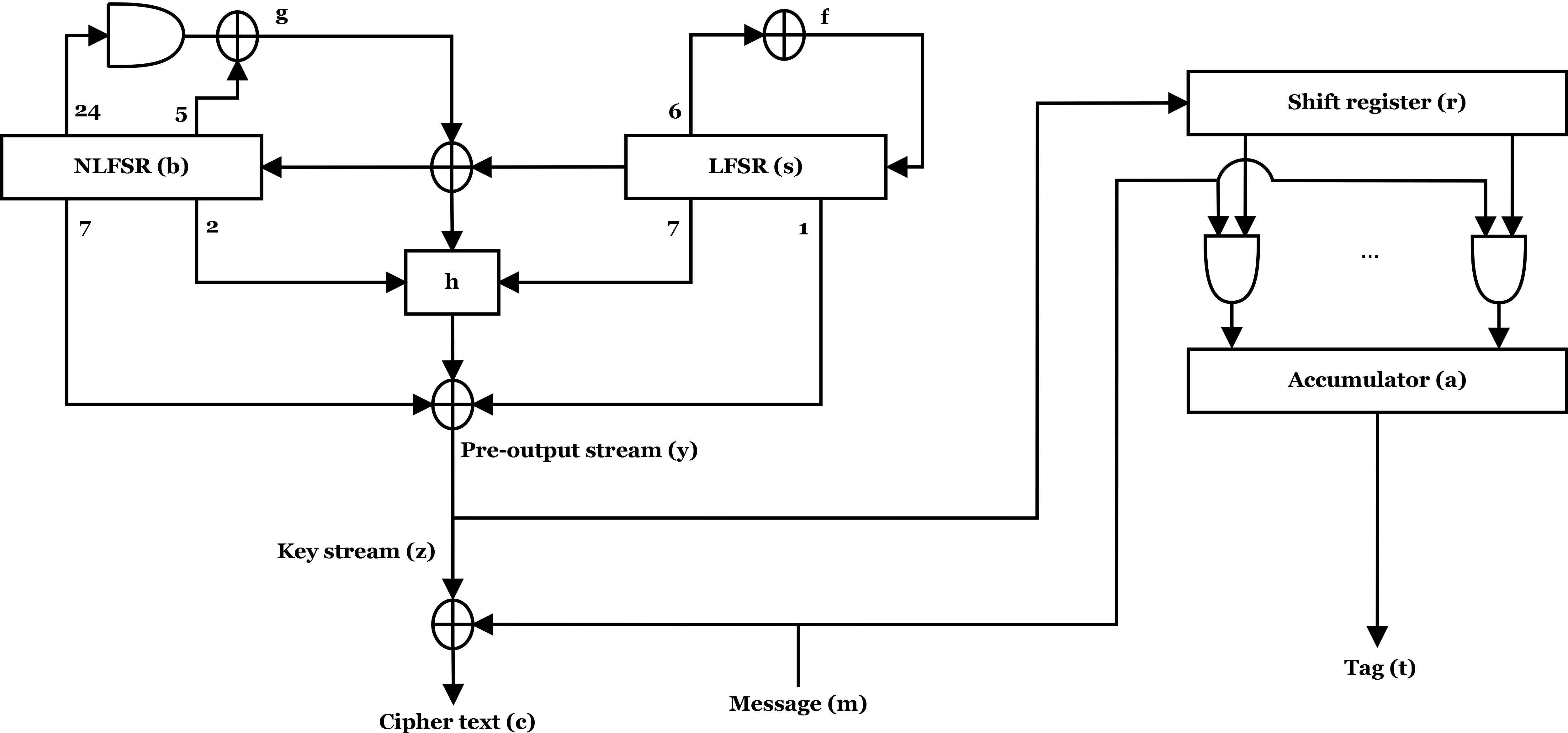

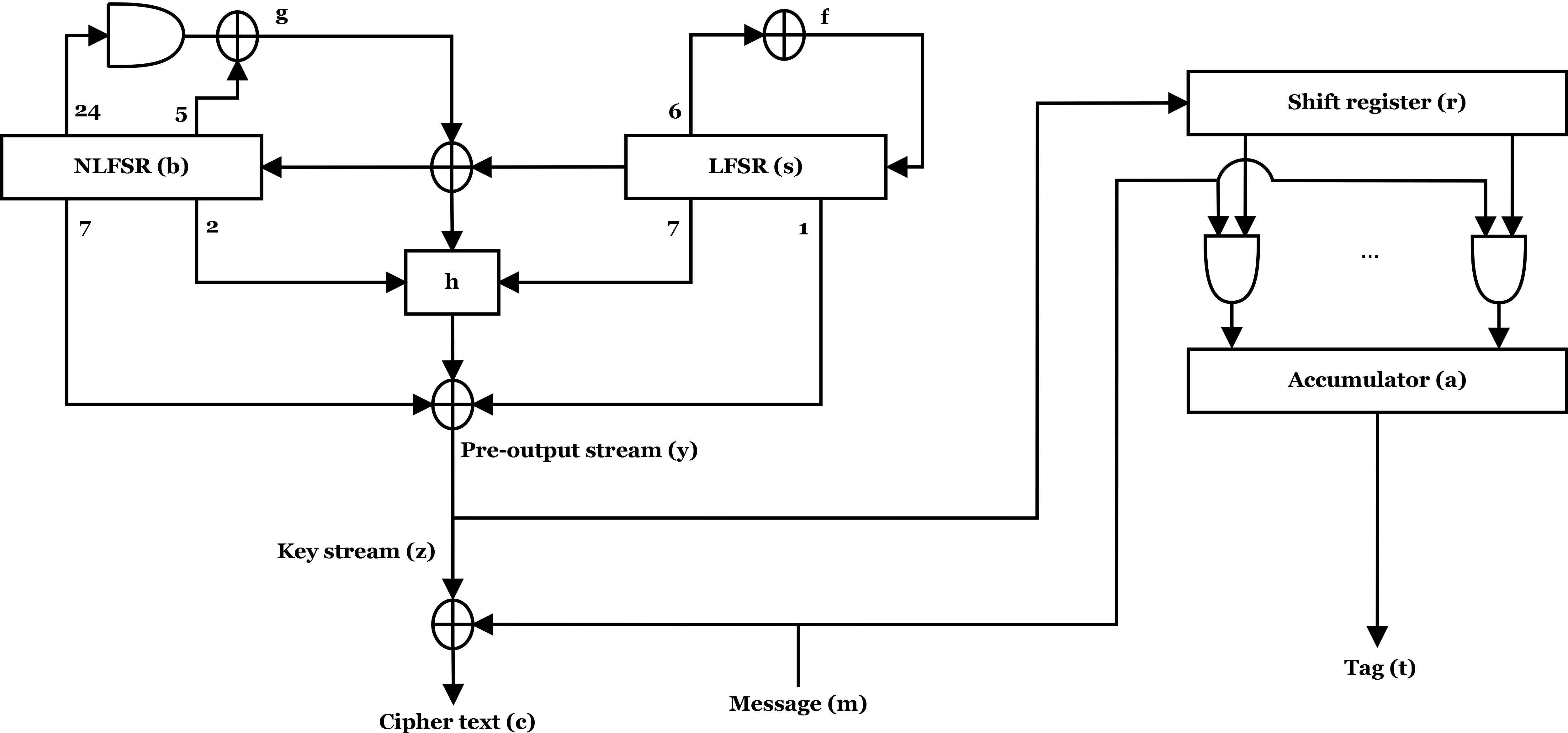

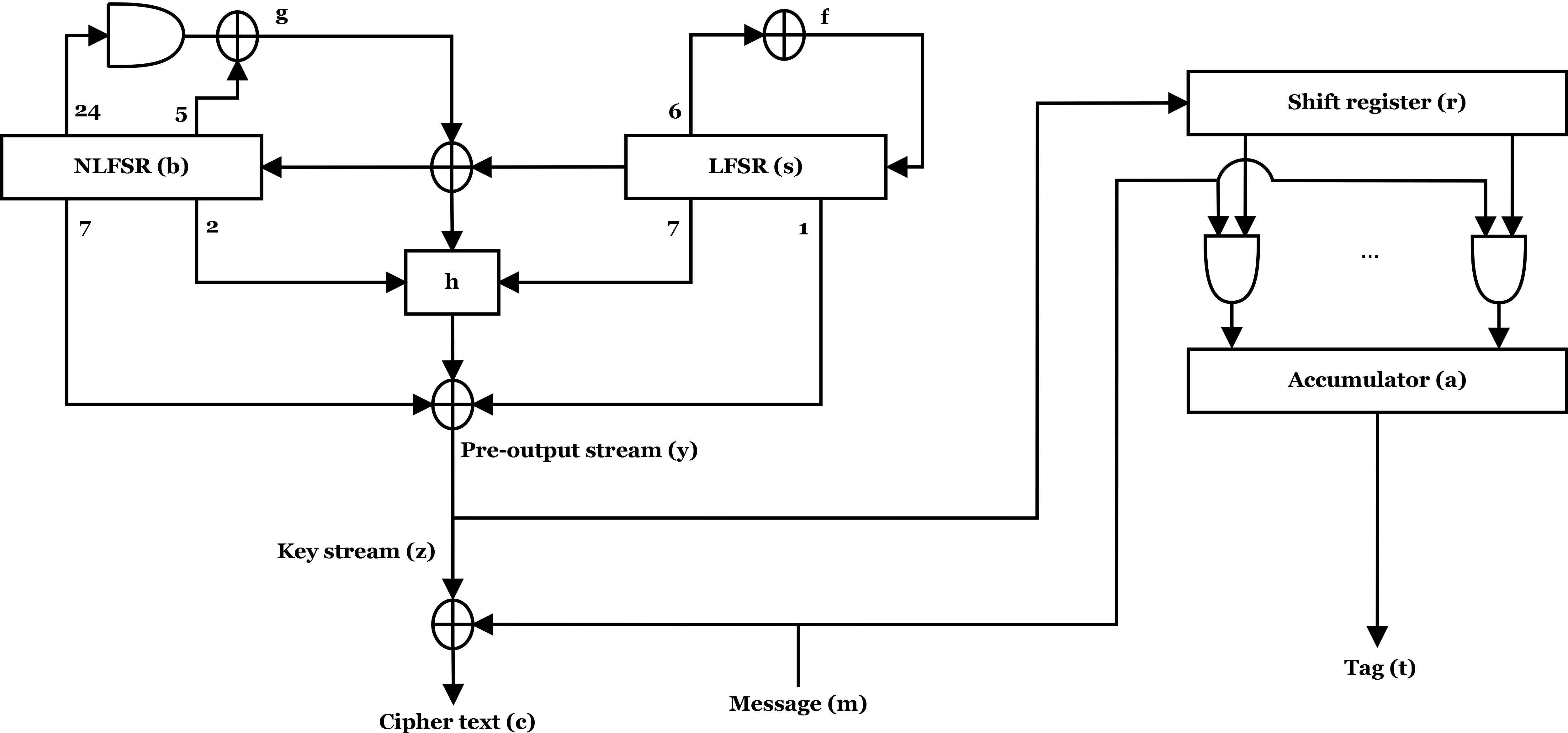

Grain 128a consists of two large parts: Pre-output function and MAC. The pre-output function has an internal state size of 256 bits, consisting of two registers of size 128 bit:

NLFSR

A nonlinear-feedback shift register (NLFSR) is a shift register whose input bit is a non-linear function of its previous state.

For an n-bit shift register ''r'' its next state is defined as:

r_(b_0, b_1, b_2, \ldots, b_)=r_(b_1, b_2, \ldots, f(b ...

and

LFSR

In computing, a linear-feedback shift register (LFSR) is a shift register whose input bit is a linear function of its previous state.

The most commonly used linear function of single bits is exclusive-or (XOR). Thus, an LFSR is most often a sh ...

. The MAC supports variable tag lengths w such that

Grain 128a consists of two large parts: Pre-output function and MAC. The pre-output function has an internal state size of 256 bits, consisting of two registers of size 128 bit:

Grain 128a consists of two large parts: Pre-output function and MAC. The pre-output function has an internal state size of 256 bits, consisting of two registers of size 128 bit:  Grain 128a consists of two large parts: Pre-output function and MAC. The pre-output function has an internal state size of 256 bits, consisting of two registers of size 128 bit:

Grain 128a consists of two large parts: Pre-output function and MAC. The pre-output function has an internal state size of 256 bits, consisting of two registers of size 128 bit: