|

Big.LITTLE

ARM big.LITTLE is a heterogeneous computing Computer architecture, architecture developed by Arm Holdings, coupling relatively battery-saving and slower processor cores (''LITTLE'') with relatively more powerful and power-hungry ones (''big''). The intention is to create a multi-core processor that can adjust better to dynamic computing needs and use less power than clock scaling alone. ARM's marketing material promises up to a 75% savings in power usage for some activities. Most commonly, ARM big.LITTLE architectures are used to create a multi-processor system-on-chip (MPSoC). In October 2011, big.LITTLE was announced along with the ARM Cortex-A7 MPCore, Cortex-A7, which was designed to be Instruction set architecture, architecturally compatible with the ARM Cortex-A15 MPCore, Cortex-A15. In October 2012 ARM announced the ARM Cortex-A53, Cortex-A53 and ARM Cortex-A57, Cortex-A57 (ARMv8, ARMv8-A) cores, which are also intercompatible to allow their use in a big.LITTLE chip. ARM ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

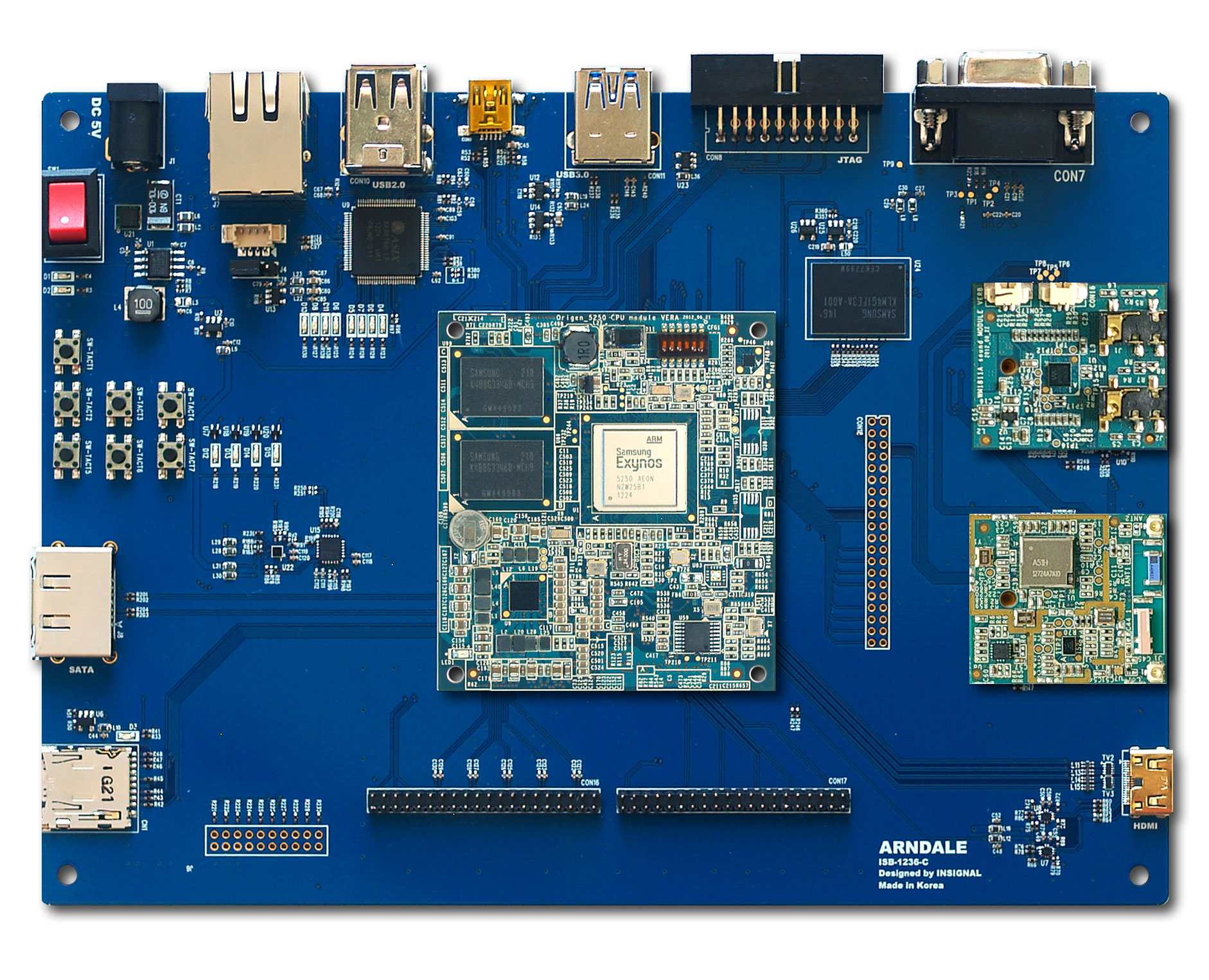

Exynos

The Samsung Exynos (stylized as SΛMSUNG Exynos), formerly Hummingbird (), is a series of ARM architecture, Arm-based System on a chip, system-on-chips developed by Samsung Electronics' System LSI division and manufactured by Samsung Foundry. It is a continuation of Samsung's earlier List of Samsung systems on a chip, S3C, S5L and S5P line of SoCs. The first debut of Samsung's indigenously developed SoC is Samsung Hummingbird (S5PC110/111), later renamed as Exynos 3 Single 3110. Samsung announce it on July 27, 2009. In 2011, Samsung announced Exynos 4 Dual 4210 that was later equipped on Samsung Galaxy S II. Since then, Samsung has used Exynos as a representative brand name of their SoC, based on Arm Cortex cores. In 2017, Samsung launched their proprietary Arm ISA-based customized core designs, codenamed "Exynos M". Exynos M series core made a debut with Exynos M1 nicknamed "Mongoose", which was used for Exynos 8 Octa 8890. The Exynos M-series have been implemented throughout t ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Cortex-A15 MPCore

The ARM Cortex-A15 MPCore is a 32-bit processor core licensed by ARM Holdings implementing the ARMv7-A architecture. It is a multicore processor with out-of-order superscalar pipeline running at up to 2.5 GHz. Overview ARM has claimed that the Cortex-A15 core is 40 percent more powerful than the Cortex-A9 core with the same number of cores at the same speed. The first A15 designs came out in the autumn of 2011, but products based on the chip did not reach the market until 2012. Key features of the Cortex-A15 core are: * 40-bit Large Physical Address Extensions (LPAE) addressing up to 1 TB of RAM with a 32-bit virtual address space. * 15 stage integer/17–25 stage floating point pipeline, with out-of-order speculative issue 3-way superscalar execution pipeline * 4 cores per cluster, up to 2 clusters per chip with CoreLink 400 (CCI-400, an AMBA-4 coherent interconnect) and 4 clusters per chip with CCN-504. ARM provides specifications but the licensees individually ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Multi-core Processor

A multi-core processor (MCP) is a microprocessor on a single integrated circuit (IC) with two or more separate central processing units (CPUs), called ''cores'' to emphasize their multiplicity (for example, ''dual-core'' or ''quad-core''). Each core reads and executes Instruction set, program instructions, specifically ordinary Instruction set, CPU instructions (such as add, move data, and branch). However, the MCP can run instructions on separate cores at the same time, increasing overall speed for programs that support Multithreading (computer architecture), multithreading or other parallel computing techniques. Manufacturers typically integrate the cores onto a single IC Die (integrated circuit), die, known as a ''chip multiprocessor'' (CMP), or onto multiple dies in a single Chip carrier, chip package. As of 2024, the microprocessors used in almost all new personal computers are multi-core. A multi-core processor implements multiprocessing in a single physical package. Des ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Cortex-A7 MPCore

The ARM Cortex-A7 MPCore is a 32-bit microprocessor core licensed by ARM Holdings implementing the ARMv7-A architecture announced in 2011. Overview It has two target applications; firstly as a smaller, simpler, and more power-efficient successor to the Cortex-A8. The other use is in the big.LITTLE architecture, combining one or more A7 cores with one or more Cortex-A15 cores into a heterogeneous system. To do this it is fully feature-compatible with the A15. Key features of the Cortex-A7 core are: * Partial dual-issue, in-order microarchitecture with an 8-stage pipeline * NEON SIMD instruction set extension * VFPv4 Floating Point Unit * Thumb-2 instruction set encoding * Jazelle RCT * Hardware virtualization * Large Page Address Extensions (LPAE) * Integrated level 2 Cache (0–1 MB) * 1.9 DMIPS / MHz * Typical clock speed 1.5 GHz Chips Several system-on-chips (SoC) have implemented the Cortex-A7 core, including: * Allwinner A20 (dual-core A7 + Mali-400 MP2 GPU) * ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Heterogeneous Computing

Heterogeneous computing refers to systems that use more than one kind of processor or core. These systems gain performance or energy efficiency not just by adding the same type of processors, but by adding dissimilar coprocessors, usually incorporating specialized processing capabilities to handle particular tasks. Heterogeneity Usually heterogeneity in the context of computing refers to different instruction-set architectures (ISA), where the main processor has one and other processors have another - usually a very different - architecture (maybe more than one), not just a different microarchitecture ( floating point number processing is a special case of this - not usually referred to as heterogeneous). In the past heterogeneous computing meant different ISAs had to be handled differently, while in a modern example, Heterogeneous System Architecture (HSA) systems eliminate the difference (for the user) while using multiple processor types (typically CPUs and GPUs), usua ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARMv8

ARM (stylised in lowercase as arm, formerly an acronym for Advanced RISC Machines and originally Acorn RISC Machine) is a family of RISC instruction set architectures (ISAs) for computer processors. Arm Holdings develops the ISAs and licenses them to other companies, who build the physical devices that use the instruction set. It also designs and licenses cores that implement these ISAs. Due to their low costs, low power consumption, and low heat generation, ARM processors are useful for light, portable, battery-powered devices, including smartphones, laptops, and tablet computers, as well as embedded systems. However, ARM processors are also used for desktops and servers, including Fugaku, the world's fastest supercomputer from 2020 to 2022. With over 230 billion ARM chips produced, , ARM is the most widely used family of instruction set architectures. There have been several generations of the ARM design. The original ARM1 used a 32-bit internal structure but had ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Cortex-A53

The ARM Cortex-A53 is one of the first two central processing units implementing the ARMv8-A 64-bit instruction set designed by ARM Holdings' Cambridge design centre, along with the Cortex-A57. The Cortex-A53 is a 2-wide decode superscalar processor, capable of dual-issuing some instructions. It was announced October 30, 2012 and is marketed by ARM as either a stand-alone, more energy-efficient alternative to the more powerful Cortex-A57 microarchitecture, or to be used alongside a more powerful microarchitecture in a big.LITTLE configuration. It is available as an IP core to licensees, like other ARM intellectual property and processor designs. Overview * 8-stage pipelined processor with 2-way superscalar, in-order execution pipeline * DSP and NEON SIMD extensions are mandatory per core * VFPv4 Floating Point Unit onboard (per core) * Hardware virtualization support * TrustZone security extensions * 64-byte cache lines * 10-entry L1 TLB, and 512-entry L2 TLB * 4KiB c ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Cortex-A17

The ARM Cortex-A17 is a 32-bit processor core implementing the ARMv7-A architecture, licensed by ARM Holdings. Providing up to four cache-coherent cores, it serves as the successor to the Cortex-A9 and replaces the previous ARM Cortex-A12 specifications. ARM claims that the Cortex-A17 core provides 60% higher performance than the Cortex-A9 core, while reducing the power consumption by 20% under the same workload. ARM renamed Cortex-A12 to a variant of Cortex-A17 since the second revision of the A12 core in early 2014, because these two were indistinguishable in performance and all features available in the A17 were used as upgrades in the A12. New features of the Cortex-A17 specification, not found in the Cortex-A9 specification, are all improvements from the third-generation ARM Cortex-A, which also includes the Cortex-A7 and Cortex-A15: * Hardware virtualization and 40-bit Large Physical Address Extensions (LPAE) addressing * Full-system coherency, bringing support for th ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Out-of-order Execution

In computer engineering, out-of-order execution (or more formally dynamic execution) is an instruction scheduling paradigm used in high-performance central processing units to make use of instruction cycles that would otherwise be wasted. In this paradigm, a processor executes instructions in an order governed by the availability of input data and execution units, rather than by their original order in a program. In doing so, the processor can avoid being idle while waiting for the preceding instruction to complete and can, in the meantime, process the next instructions that are able to run immediately and independently. History Out-of-order execution is a restricted form of dataflow architecture, which was a major research area in computer architecture in the 1970s and early 1980s. Early use in supercomputers The first machine to use out-of-order execution was the CDC 6600 (1964), designed by James E. Thornton, which uses a scoreboard to avoid conflicts. It permits ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Multi-processor System-on-chip

A system on a chip (SoC) is an integrated circuit that combines most or all key components of a computer or electronic system onto a single microchip. Typically, an SoC includes a central processing unit (CPU) with memory, input/output, and data storage control functions, along with optional features like a graphics processing unit (GPU), Wi-Fi connectivity, and radio frequency processing. This high level of integration minimizes the need for separate, discrete components, thereby enhancing power efficiency and simplifying device design. High-performance SoCs are often paired with dedicated memory, such as LPDDR, and flash storage chips, such as eUFS or eMMC, which may be stacked directly on top of the SoC in a package-on-package (PoP) configuration or placed nearby on the motherboard. Some SoCs also operate alongside specialized chips, such as cellular modems. Fundamentally, SoCs integrate one or more processor cores with critical peripherals. This comprehensive integration ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

ARM Cortex-A57

The ARM Cortex-A57 is a central processing unit implementing the ARMv8-A 64-bit instruction set designed by ARM Holdings. The Cortex-A57 is an out-of-order superscalar pipeline. It is available as SIP core to licensees, and its design makes it suitable for integration with other SIP cores (e.g. GPU, display controller, DSP, image processor, etc.) into one die constituting a system on a chip (SoC). Overview * Pipelined processor with deeply out of order, speculative issue 3-way superscalar execution pipeline * DSP and NEON SIMD extensions are mandatory per core * VFPv4 Floating Point Unit onboard (per core) * Hardware virtualization support * Thumb-2 instruction set encoding reduces the size of 32-bit programs with little impact on performance. * TrustZone security extensions * Program Trace Macrocell and CoreSight Design Kit for unobtrusive tracing of instruction execution * 32 KiB data (2-way set-associative) + 48 KiB instruction (3-way set-associative) L1 ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |