|

XDR DRAM

XDR DRAM (extreme data rate dynamic random-access memory) is a high-performance dynamic random-access memory interface. It is based on and succeeds RDRAM. Competing technologies include DDR2 SDRAM, DDR2 and GDDR4 SDRAM, GDDR4. Overview XDR was designed to be effective in small, high-bandwidth consumer systems, high-performance memory applications, and high-end Graphics processing unit, GPUs. It eliminates the unusually high latency problems that plagued early forms of RDRAM. Also, XDR DRAM has heavy emphasis on per-pin bandwidth, which can benefit further cost control on PCB production. This is because fewer lanes are needed for the same amount of bandwidth. Rambus owns the rights to the technology. XDR is used by Sony in the PlayStation 3 console. Technical specifications Performance * Initial clock rate at 400 MHz. * (ODR): Eight bits per clock cycle per lane. * Each chip provides 8, 16, or 32 programmable lanes, providing up to 230.4 gigabit, Gbit/s (28.8&nbs ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

XDRAM

XDR DRAM (extreme data rate dynamic random-access memory) is a high-performance dynamic random-access memory interface. It is based on and succeeds RDRAM. Competing technologies include DDR2 and GDDR4. Overview XDR was designed to be effective in small, high-bandwidth consumer systems, high-performance memory applications, and high-end GPUs. It eliminates the unusually high latency problems that plagued early forms of RDRAM. Also, XDR DRAM has heavy emphasis on per-pin bandwidth, which can benefit further cost control on PCB production. This is because fewer lanes are needed for the same amount of bandwidth. Rambus owns the rights to the technology. XDR is used by Sony in the PlayStation 3 console. Technical specifications Performance * Initial clock rate at 400 MHz. * (ODR): Eight bits per clock cycle per lane. * Each chip provides 8, 16, or 32 programmable lanes, providing up to 230.4 Gbit/s (28.8 GB/s) at 900 MHz (7.2 GHz effective). Featu ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Low Voltage Differential Signaling

Low-voltage differential signaling (LVDS), also known as TIA/EIA-644, is a technical standard that specifies electrical characteristics of a differential, serial signaling standard. LVDS operates at low power and can run at very high speeds using inexpensive twisted-pair copper cables. LVDS is a physical layer specification only; many data communication standards and applications use it and add a data link layer as defined in the OSI model on top of it. LVDS was introduced in 1994, and has become popular in products such as LCD-TVs, in-car entertainment systems, industrial cameras and machine vision, notebook and tablet computers, and communications systems. The typical applications are high-speed video, graphics, video camera data transfers, and general purpose computer buses. Early on, the notebook computer and LCD display vendors commonly used the term LVDS instead of FPD-Link when referring to their protocol, and the term ''LVDS'' has mistakenly become synonymous with ' ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

XDR2 DRAM

XDR2 DRAM was a proposed type of dynamic random-access memory that was offered by Rambus. It was announced on July 7, 2005 and the specification for which was released on March 26, 2008. Rambus has designed XDR2 as an evolution of, and the successor to, XDR DRAM. XDR2 DRAM is intended for use in high-end graphics cards and networking equipment. As a fabless semiconductor company, Rambus only produces a design; it must make deals with memory manufacturers to produce XDR2 DRAM chips, and there has been a notable lack of interest in doing so. Changes from XDR DRAM Signaling In addition to a higher clock rate (up to 800 MHz), the XDR2 differential data lines transfer data at 16 times the system clock rate, transferring 16 bits per pin per clock cycle. This "Hexadecimal Data Rate" is twice XDR's 8× multiplier. The basic burst size has also doubled. Unlike XDR, memory commands are also transmitted over differential point-to-point links at this high data rate. The command bus ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Double Data Rate

In computing, a computer bus operating with double data rate (DDR) transfers data on both the rising and falling edges of the clock signal. This is also known as double pumped, dual-pumped, and double transition. The term toggle mode is used in the context of NAND flash memory. Overview The simplest way to design a clocked electronic circuit is to make it perform one transfer per full cycle (rise and fall) of a clock signal. This, however, requires that the clock signal changes twice per transfer, while the data lines change at most once per transfer. When operating at a high bandwidth, signal integrity limitations constrain the clock frequency. By using both edges of the clock, the data signals operate with the same limiting frequency, thereby doubling the data transmission rate. This technique has been used for microprocessor front-side busses, Ultra-3 SCSI, expansion buses ( AGP, PCI-X), graphics memory (GDDR), main memory (both RDRAM and DDR1 through DDR5), and the ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Active-low

In digital circuits, a logic level is one of a finite number of states that a digital signal can inhabit. Logic levels are usually represented by the voltage difference between the signal and ground, although other standards exist. The range of voltage levels that represent each state depends on the logic family being used. A '' logic-level shifter'' can be used to allow compatibility between different circuits. 2-level logic In binary logic the two levels are logical high and logical low, which generally correspond to binary numbers 1 and 0 respectively. Signals with one of these two levels can be used in boolean algebra for digital circuit design or analysis. Active state The use of either the higher or the lower voltage level to represent either logic state is arbitrary. The two options are active high and active low. Active-high and active-low states can be mixed at will: for example, a read only memory integrated circuit may have a chip-select signal that is active-low, ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Single-ended Signalling

Single-ended signaling is the simplest and most commonly used method of transmitting electrical signals over wires. One wire carries a varying voltage that represents the signal, while the other wire is connected to a reference voltage, usually ground. The main alternative to single-ended signaling is called ''differential signaling'' where the two conductors carry signals equal in magnitude but of opposite electric polarity. Single-ended signaling is less expensive to implement than differential, but it has a distinct disadvantage: a single-ended system requires a power supply voltage equal to the maximum amplitude of the signal to be received whereas a differential system only requires a voltage half of the signal amplitude to be received. For a given power supply voltage then, a differential system produces signals of twice the amplitude and therefore has twice as good noise immunity (6 dB higher signal-to-noise ratio) as a single-ended system. The main advantage of single-e ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Delay-locked Loop

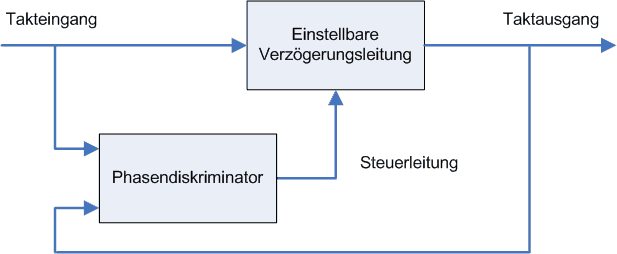

In electronics, a delay-locked loop (DLL) is a pseudo-digital circuit similar to a phase-locked loop (PLL), with the main difference being the absence of an internal voltage-controlled oscillator, replaced by a delay line. A DLL can be used to change the phase of a clock signal (a signal with a periodic waveform), usually to enhance the ''clock rise''-to-''data output valid'' timing characteristics of integrated circuits (such as DRAM devices). DLLs can also be used for clock recovery (CDR). From the outside, a DLL can be seen as a negative delay gate placed in the clock path of a digital circuit. The main component of a DLL is a delay chain composed of many delay gates connected output-to-input. The input of the chain (and thus of the DLL) is connected to the clock that is to be negatively delayed. A multiplexer is connected to each stage of the delay chain; a control circuit automatically updates the selector of this multiplexer to produce the negative delay effect. The output ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Phase-locked Loop

A phase-locked loop or phase lock loop (PLL) is a control system that generates an output signal whose phase is related to the phase of an input signal. There are several different types; the simplest is an electronic circuit consisting of a variable frequency oscillator and a phase detector in a feedback loop. The oscillator's frequency and phase are controlled proportionally by an applied voltage, hence the term voltage-controlled oscillator (VCO). The oscillator generates a periodic signal of a specific frequency, and the phase detector compares the phase of that signal with the phase of the input periodic signal, to adjust the oscillator to keep the phases matched. Keeping the input and output phase in lockstep also implies keeping the input and output frequencies the same. Consequently, in addition to synchronizing signals, a phase-locked loop can track an input frequency, or it can generate a frequency that is a multiple of the input frequency. These properties are use ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

IC Power Supply Pin

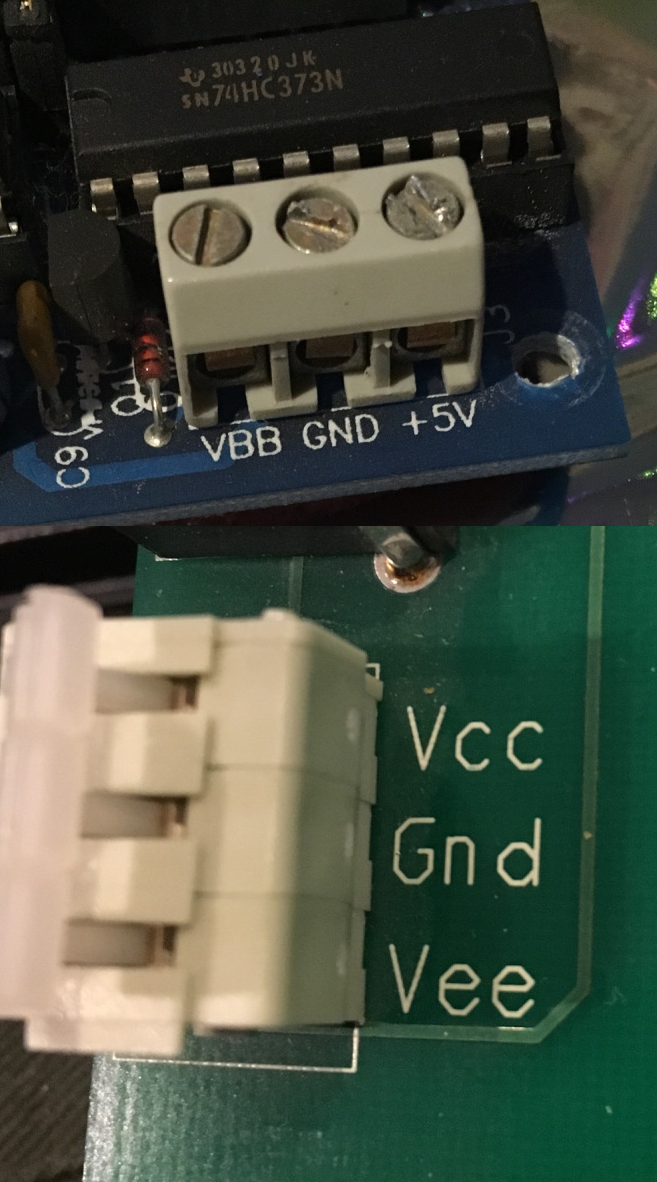

IC power-supply pins denote a voltage and current supply terminals in electric, electronics engineering, and in Integrated circuit design. Integrated circuits (ICs) have at least two pins that connect to the power rails of the circuit in which they are installed. These are known as the power-supply pins. However, the labeling of the pins varies by IC family and manufacturer. The double subscript notation usually corresponds to a first letter in a given IC family (transistors) notation of the terminals (e.g. VDD supply for a drain terminal in FETs etc.). The simplest labels are V+ and V−, but internal design and historical traditions have led to a variety of other labels being used. V+ and V− may also refer to the non-inverting (+) and inverting (−) voltage inputs of ICs like op amps. For power supplies, sometimes one of the supply rails is referred to as ground (abbreviated "GND") positive and negative voltages are relative to the ground. In digital electronics, negat ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Chip Scale Package

A chip scale package or chip-scale package (CSP) is a type of integrated circuit package. Originally, CSP was the acronym for ''chip-size packaging.'' Since only a few packages are chip size, the meaning of the acronym was adapted to ''chip-scale packaging''. According to IPC's standard J-STD-012, ''Implementation of Flip Chip and Chip Scale Technology'', in order to qualify as chip scale, the package must have an area no greater than 1.2 times that of the die and it must be a single-die, direct surface mountable package. Another criterion that is often applied to qualify these packages as CSPs is their ball pitch should be no more than 1 mm. The concept was first proposed by Junichi Kasai of Fujitsu and Gen Murakami of Hitachi Cable in 1993. The first concept demonstration however came from Mitsubishi Electric. The die may be mounted on an interposer upon which pads or balls are formed, like with flip chip ball grid array (BGA) packaging, or the pads may be etched or prin ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Open Collector

An open collector is a common type of output found on many integrated circuits (IC), which behaves like a switch that is either connected to ground or disconnected. Instead of outputting a signal of a specific voltage or current, the output signal is applied to the base of an internal NPN transistor whose collector is externalized (open) on a pin of the IC. The emitter of the NPN transistor is connected internally to the ground pin. If the output device is a MOSFET the output is called open drain and it functions in a similar way. For example, the I²C bus and 1-Wire bus are based on this concept. Function In the picture, the transistor base is labeled "IC output". This is a signal from the internal IC logic to the transistor. This signal controls the transistor switching. The external output is the transistor collector; the transistor forms an interface between the internal IC logic and parts external to the IC. On schematic component symbols, the open output is indicated wit ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |

Dynamic Random-access Memory

Dynamic random-access memory (dynamic RAM or DRAM) is a type of random-access semiconductor memory that stores each bit of data in a memory cell, usually consisting of a tiny capacitor and a transistor, both typically based on metal-oxide-semiconductor (MOS) technology. While most DRAM memory cell designs use a capacitor and transistor, some only use two transistors. In the designs where a capacitor is used, the capacitor can either be charged or discharged; these two states are taken to represent the two values of a bit, conventionally called 0 and 1. The electric charge on the capacitors gradually leaks away; without intervention the data on the capacitor would soon be lost. To prevent this, DRAM requires an external ''memory refresh'' circuit which periodically rewrites the data in the capacitors, restoring them to their original charge. This refresh process is the defining characteristic of dynamic random-access memory, in contrast to static random-access memory (SRAM ... [...More Info...] [...Related Items...] OR: [Wikipedia] [Google] [Baidu] |